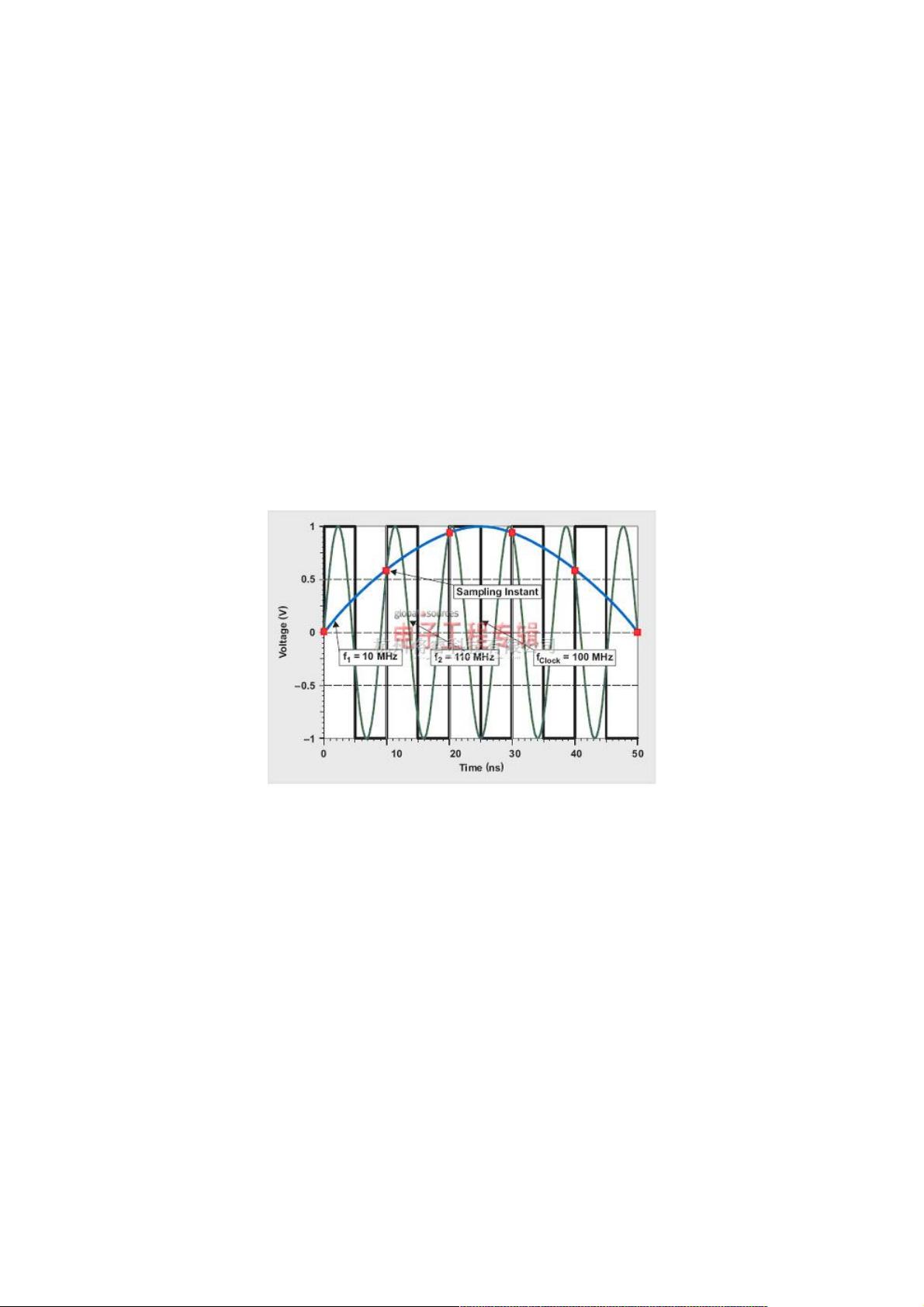

新型的高速ADC都具备高模拟输入带宽(约为最大采样频率的3到6倍),因此它们可以用于许多欠采样应用中。ADC设计的最新进展极大地扩展了可用输入范围,这样系统设计人员便可以去掉至少一个中间频率级,从而降低成本和功耗。在欠采样接收机设计中必须要特别注意采样时钟,因为在一些高输入频率下时钟抖动会成为限制信噪比(SNR)的主要原因。 本系列文章共有三部分,"第1部分"重点介绍如何准确地估算某个时钟源的抖动,以及如何将其与ADC的孔径抖动组合。在"第2部分"中,该组合抖动将用于计算ADC的SRN,然后将其与实际测量结果对比。"第3部分"将介绍如何通过改善ADC的孔径抖动来进一步增加ADC的SNR, 在模拟技术中,准确估算采样时钟抖动对于高性能的数字信号处理至关重要,尤其是在高速模数转换器(ADC)的应用中。随着ADC技术的进步,现在的高速ADC具有高模拟输入带宽,允许它们在欠采样模式下工作,即以远低于输入信号最高频率的采样率进行采样。这在很多情况下可以简化系统设计,去除额外的中间频率级,降低整体成本和功耗。然而,欠采样时钟抖动的影响会变得尤为突出,特别是在处理高输入频率信号时,它可能成为限制系统信噪比(SNR)的主要因素。 这一系列文章分为三个部分,旨在深入探讨采样时钟抖动的估算及其对ADC性能的影响。第一部分聚焦于如何精确地测量时钟源的抖动,并解释如何结合ADC的孔径抖动进行分析。孔径抖动是指ADC转换过程中的时间不确定性,它与时钟抖动一起影响着采样精度。 第二部分则利用组合后的总抖动来计算ADC的信噪比裕度(SRN),并将理论计算结果与实际测量数据进行比较。SRN是衡量ADC在考虑所有噪声源后剩余的SNR。通过比较理论计算与实测数据,可以评估ADC性能的实际表现,以及是否存在时钟抖动过大的问题。 第三部分重点关注如何通过改进ADC的孔径抖动来提高SNR,包括优化时钟信号的转换速率。转换速率影响时钟信号通过零交叉点的速度,从而影响ADC时钟电路的触发阈值。更快的转换速率可能导致更大的计时不准确,即窗口抖动,这与时钟抖动不同但同样影响SNR。 SNR受到多种因素的限制,包括量化噪声、热噪声以及时钟抖动。量化噪声在管线式ADC中通常不显著,而热噪声在低输入频率时限制SNR。时钟抖动的影响随着输入频率的增加而增强。公式1展示了SNRJitter与输入频率和总时钟抖动的关系。在固定时钟抖动条件下,SNR随输入频率的增加而线性降低。 例如,一个14位ADC在400 fs时钟抖动下,当输入频率从10MHz增加到100MHz时,SNR会因时钟抖动减少约20dB。另一方面,ADC的热噪声在所有频率下保持相对稳定,对于14位ADC来说,其热噪声大约在70到74 dB之间,但随着输入频率的提高,时钟抖动的影响逐渐超过热噪声,成为主要的SNR限制因素。 总结来说,准确估算和管理采样时钟抖动对于优化高速ADC的性能至关重要。通过理解抖动如何影响ADC的SNR,设计者能够采取措施减小抖动影响,从而提升系统的整体信号质量。这一系列文章提供的方法和分析将为系统设计者提供实用工具,帮助他们在面临高输入频率和采样率挑战时,实现更高效、更可靠的模拟到数字转换。

- 粉丝: 8

- 资源: 912

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 客户需求快速小程序项目开发技巧

- java项目,课程设计-医疗服务系统.zip

- YOLO 注释风力涡轮机表面损坏-以 YOLO 格式注释风力涡轮机表面损伤 一万六千多文件

- 第一个适用于 Java 的 REST API 框架.zip

- Nvidia GeForce GT 1030显卡驱动(Win7)

- TIA PORTAL V17 UPD8- 更新包(最新版本2024.09)-链接地址.txt

- 示例应用程序展示了客户端和服务器上 JavaFX 和 Spring 技术的集成.zip

- Screenshot_2024-11-25-14-29-06-21.jpg

- MagicEXIFTool.zip

- fontawesome-webfont.woff

信息提交成功

信息提交成功