没有合适的资源?快使用搜索试试~ 我知道了~

18342138 郑卓民 实验八1

需积分: 0 0 下载量 124 浏览量

2022-08-08

21:21:34

上传

评论

收藏 6.22MB DOCX 举报

温馨提示

试读

21页

2、根据真值表,一般采用卡诺图进行化简,得出逻辑表达式 3、如果已对器件类型有所规定或限制,则应将函数表达式变换成与器件类型相适应 的形式 4、根据化简或变换后

资源详情

资源评论

资源推荐

实验八 ALU 功能的实现

18342138 郑卓民 软工四班

预习报告

1. 复习常用组合逻辑电路工作原理和设计方法,及与之相应的 MSI 功能表及其使用方

法。

数字电路按逻辑功能和电路结构的不同特点,可分为组合逻辑电路和时序逻辑电路

两大类。组合逻辑电路是根据给定的逻辑问题,设计出能实现逻辑功能的电路。用小

规模集成电路实现组合逻辑电路,要求是使用的芯片最少,连线最少。一般设计步骤

如下:

1、首先根据实际情况确定输入变量、输出变量的个数,列出逻辑真值表。

2、根据真值表,一般采用卡诺图进行化简,得出逻辑表达式。

3、如果已对器件类型有所规定或限制,则应将函数表达式变换成与器件类型

相适应 的形式。

4、根据化简或变换后的逻辑表达式,画出逻辑电路。

5、根据逻辑电路图,查找所用集成器件的管脚图,将管脚号标在电路图上,

再接线,验证。

2. 复习采用中规模集成电路实现组合逻辑电路的方法。

1. 要对集成电路有深入的了解,知道集成电路的实现原理,各管脚的含义。

2. 中规模的器件,如译码器、数据选择器等,它们本身是为了实现某种逻辑功能而

设计的,但由于它们的一些特点,我们也可以用它们来实现任意逻辑函数。

3. 设计组合逻辑电路的流程的基础依然是:

i. 根据给定事件的因果关系列出真值表;

ii. 由真值表写函数式;

iii. 对函数式进行化简或变换;

iv. 画出逻辑图,并测试逻辑功能。

但在其中可以插入使用已有集成电路模块,简化设计,使电路功能更清晰。

3. 复习使用 vivado IP 核设计组合逻辑电路的方法。

IP 可直接使用,简化电路逻辑设计。

IP 核是一段具有特定电路功能的硬件描述语言程序,该程序与集成电路工艺无关,

可以移植到不同的半导体工艺中去生产集成电路芯片。Vivado 提供了很多 IP 核可

以直接使用,例如数学运算(乘法器,除法器,浮点运算器等)、信号处理(FFT、

DFT、DDS 等)。IP 核类似编程中的函数库,可以直接调用,非常方便,大大加快了

开发速度。

实验报告

实验目的:

1. 熟悉 vivado IP 核的功能与使用方法。

2. 掌握用 MSI 设计的组合逻辑电路的方法。

实验仪器以及器件:

1. BASYS3 实验板;

2. Vivado IP 核 : xup_74LS08_1.0( 与 门 ), xup_74LS32_1.0( 或

门 ),xup_74LS04_1.0( 非 门 ), xup_74LS151_1.0( 八 选 一 数 据 选 择 器 ),

xup_74LS138_1.0(3-8 译码器),

实验原理:

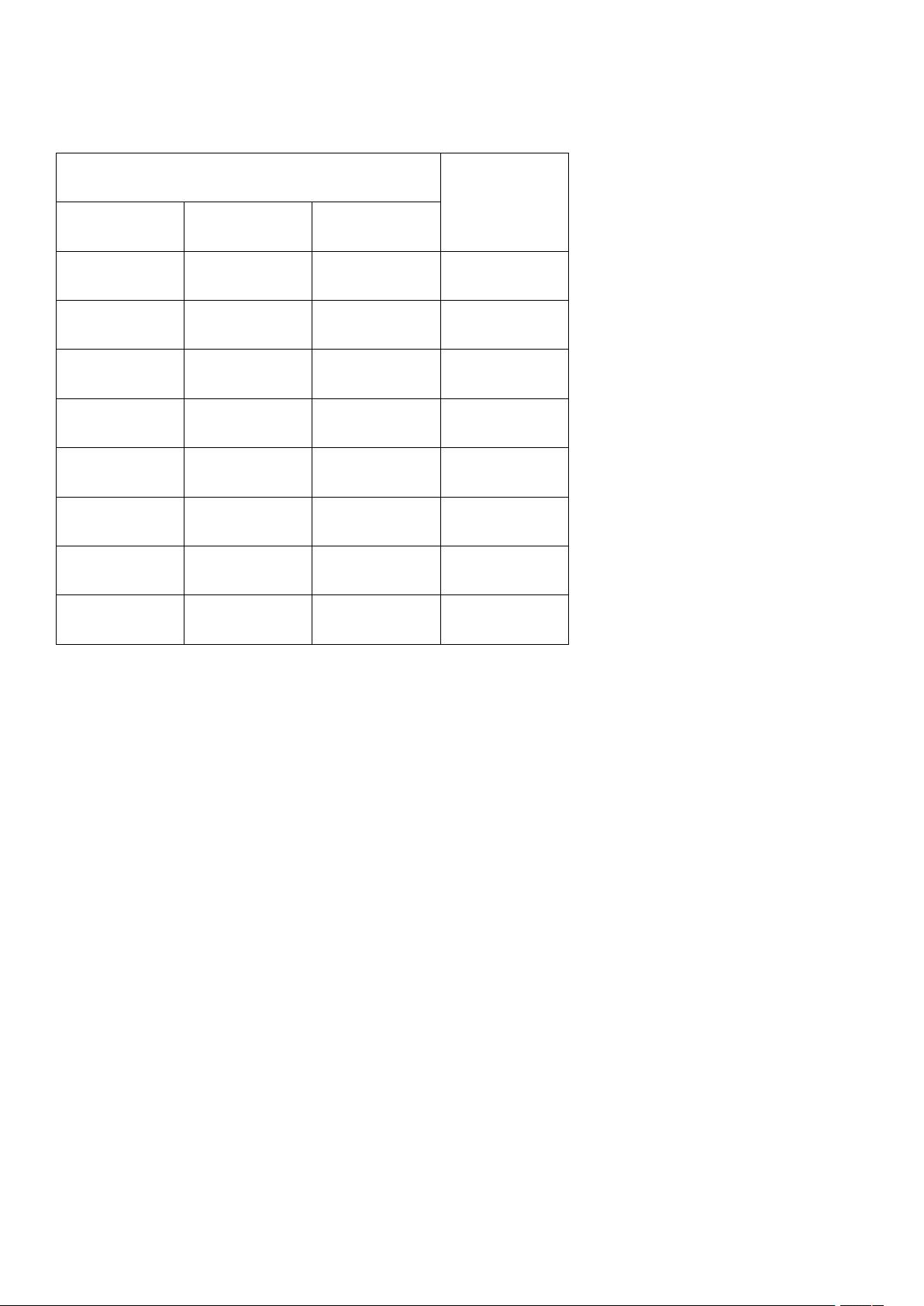

1. 一种供参考的 ALU 功能表如下表:

控制端

M2

M1

M0

功能

0

0

0

与

0

0

1

或

0

1

0

A 非

0

1

1

B 非

1

0

0

异或

1

0

1

全加

1

1

0

全减

1

1

1

清零

上述 ALU 有六个输入端包括三个控制端和三个数据输入端,其中 A、B 为 1bit 输入端

操作数。

控制端: M2、M1、M0 控制端决定 ALU 的八种运算功能,分别为与、或、非、异或、全

加、全减、清零。

数据输入端:当 ALU 进行全加(全减)运算时,三个数据输入端分别为被加数/被减数、

加数/减数、进位/借位。当 ALU 进行逻辑运算(与、或、非、异或)时,三个数据输

入端中的两个作为操作数的输入,另一个可以忽略(在设计报告中需指明)。

输出端:当 ALU 进行全加(全减)运算时,两个输出端分别为和(差)、进位(借位)。

当 ALU 进行逻辑运算时,两个输出端为逻辑运算的结果和结果的取反。

2. 在 vivado 中可以对连接的组合逻辑电路进行封装,由此使逻辑单元可以成为以后实

验可能使用到的 IP 核,简化设计流程和电路连接复杂度。

实验注意事项:

1. Xup_74ls151_1.0(八选一数据选择器)IP 核,S_n 是高电平时 74ls151 清零,因此

ALU 的清零功能可使用 S_n 端口。

2. 约束文件的设置,可运行 Run Synthesis,综合通过后选择 Open Synthesized

Design,菜单 windows 打开 I/O ports 窗口,在窗口中根据 Basys3 实验板用户手册

的引脚对应表绑定输入输出端口,然后保存为 xdc 约束文件即可。

3. 4bit ALU 中前一级的进位/借位与下一级 ALU 运算输入 A、B 一起作为输入端进入下

一级 ALU 的运算。

实验内容:

实验内容一:

1. 在 Basys3 实验板实现一个六输入二输出的 ALU,即完成 1bitALU,包括功能控制端

M2、M1、M0(拨码开关),数据输入端(A0、B0、Cn)(拨码开关), 数据输出端 Y、

Cn+1(LED 灯),ALU 功能表同实验原理部分,要求使用 74LS 系列 IP 核实现。

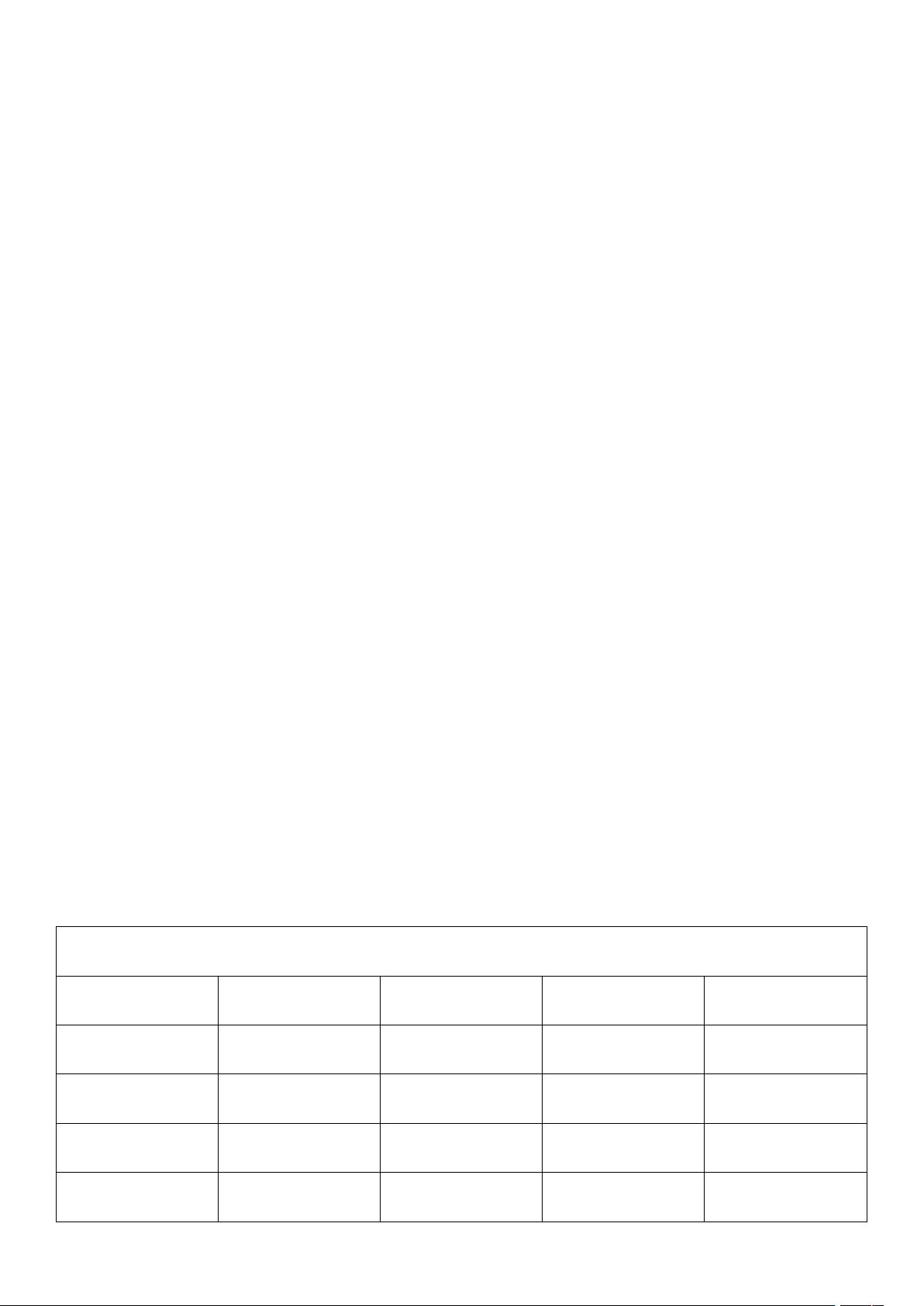

步骤一:根据 ALU 功能表画出对应各功能端的真值表:

M2M1M0 = 000 功能与

Cn

B

A

Y

Cn+1(Y`)

X

0

0

0

1

X

1

0

0

1

X

0

1

0

1

X

1

1

1

0

M2M1M0 = 001 功能或

Cn

B

A

Y

Cn+1(Y`)

X

0

0

0

1

X

1

0

1

0

X

0

1

1

0

X

1

1

1

0

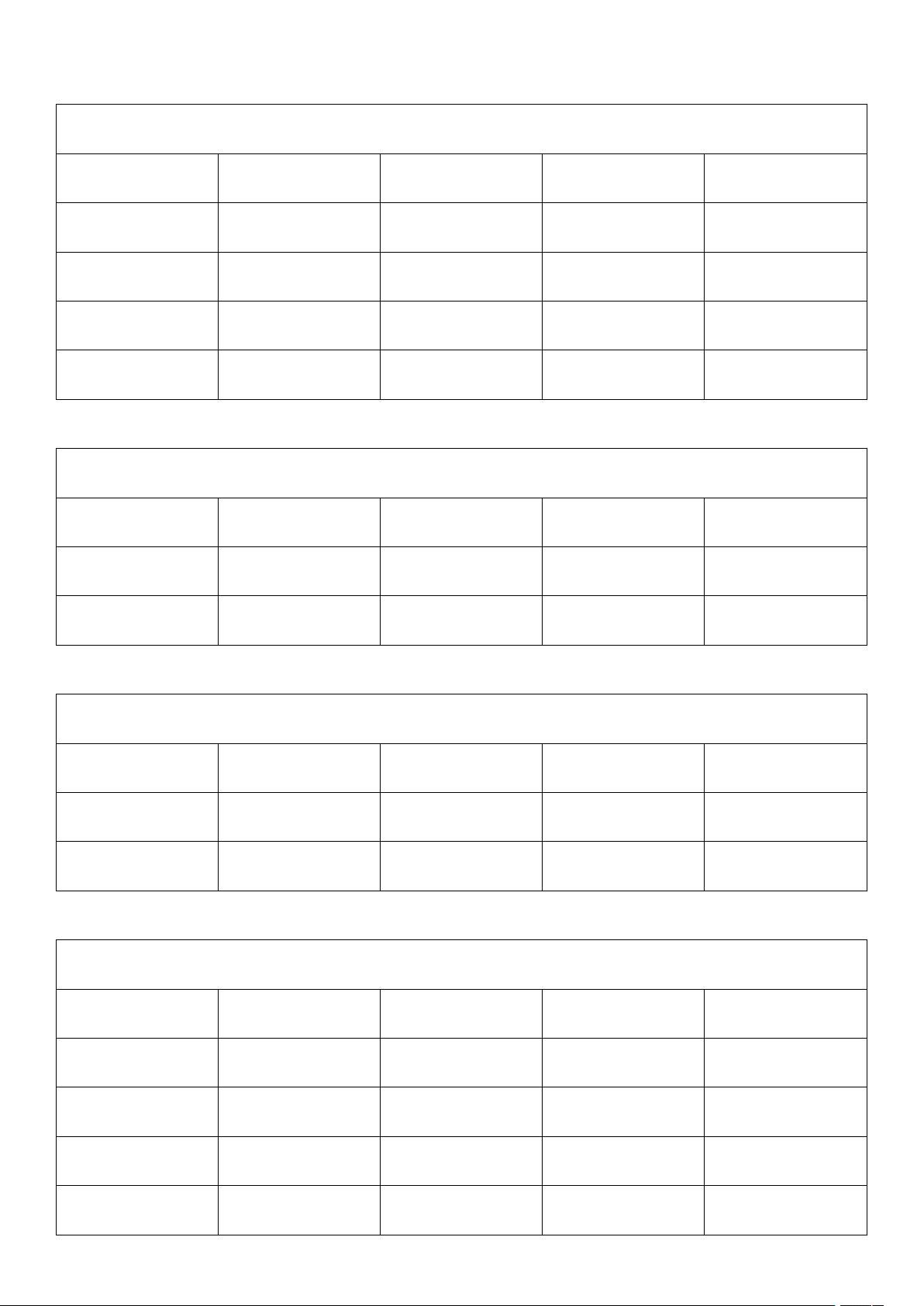

M2M1M0 = 010 功能 A 非

Cn

B

A

Y

Cn+1(Y`)

X

X

0

1

0

X

X

1

0

1

M2M1M0 = 011 功能 B 非

Cn

B

A

Y

Cn+1(Y`)

X

0

X

1

0

X

1

X

0

1

M2M1M0 = 100 功能异或

Cn

B

A

Y

Cn+1(Y`)

X

0

0

0

1

X

1

0

1

0

X

0

1

1

0

X

1

1

0

1

剩余20页未读,继续阅读

马虫医生

- 粉丝: 24

- 资源: 324

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0