第一次实验_周玉川_20172213020061

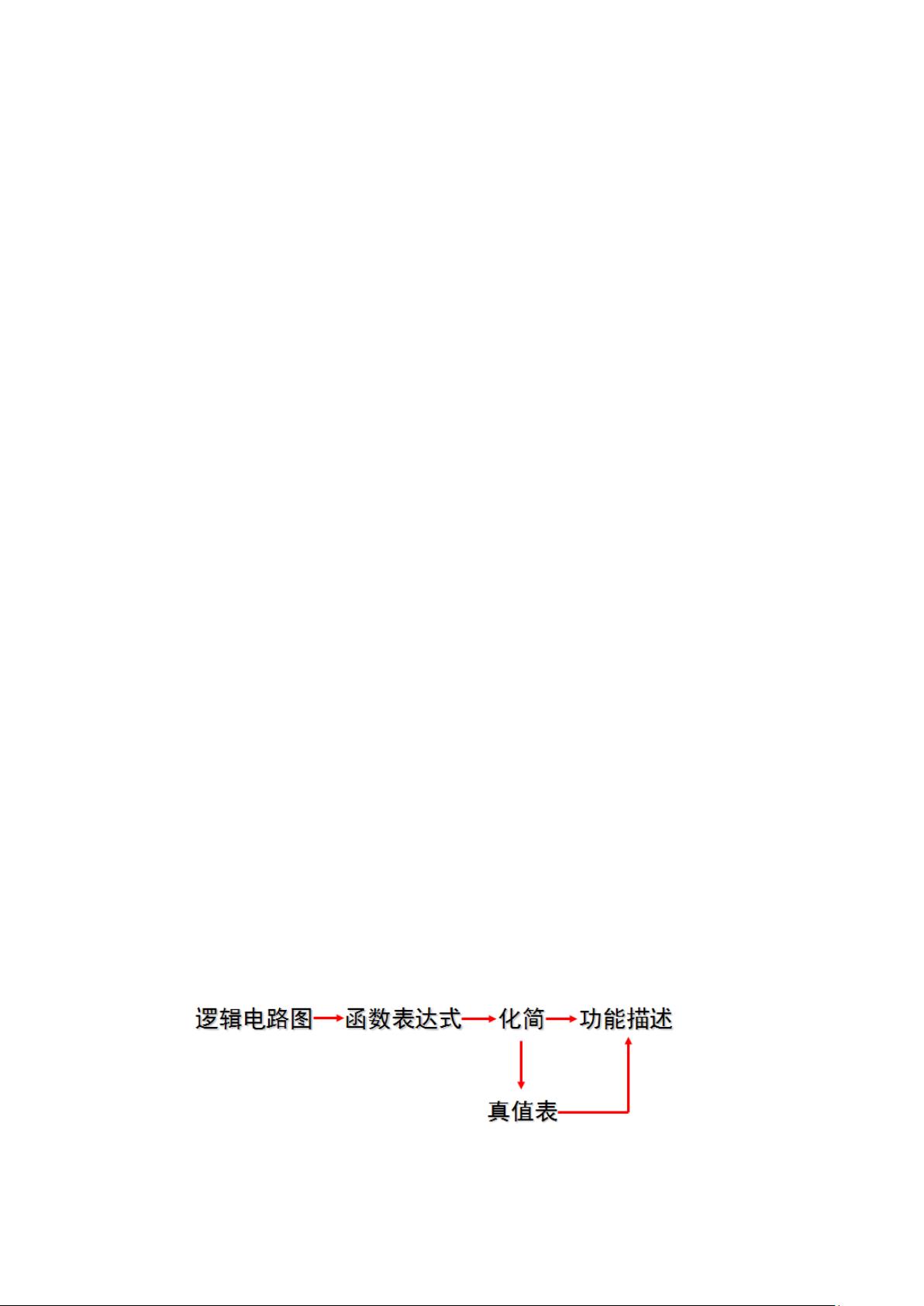

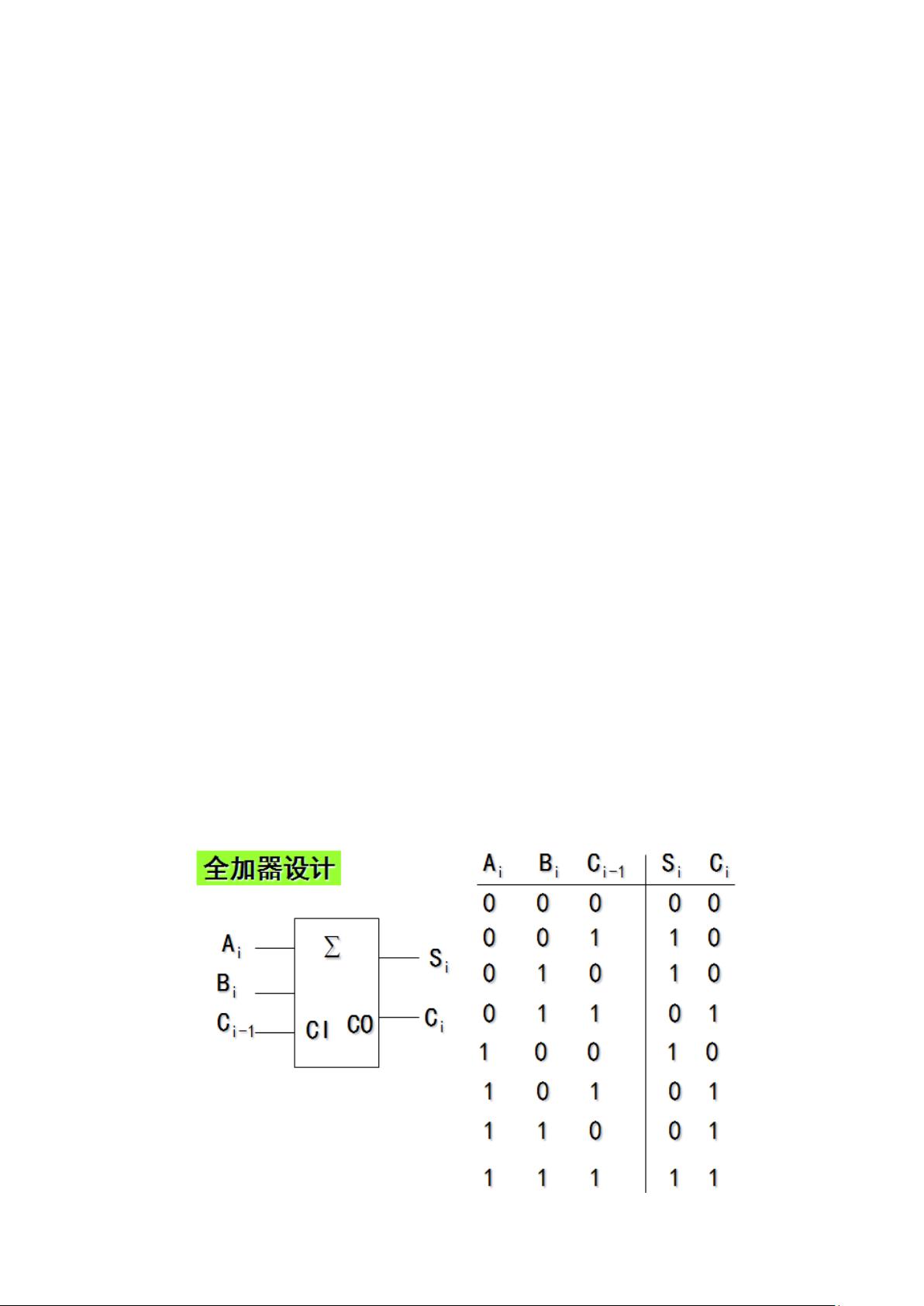

【实验报告概述】 本次实验是数字逻辑课程的一部分,由学生周玉川在电子科技大学信息与软件工程学院进行。实验的主要目标是掌握基本的数字逻辑概念,包括集成门电路的逻辑功能与特性、逻辑符号的理解、集成电路的使用以及组合逻辑电路的设计和测试方法。通过全加器或全减器的设计与实现,学生得以实践逻辑电路分析和设计的过程。 【实验原理】 1. **组合逻辑电路分析方法**:通过对事件因果关系的抽象分析,确定输入变量和输出变量。定义逻辑状态,通常以“0”代表逻辑低,“1”代表逻辑高。接着,根据因果关系列出真值表。然后,通过化简或变换得到逻辑函数表达式。绘制逻辑电路图来体现这些关系。 2. **组合逻辑电路设计方法**:A. 同样的逻辑抽象过程用于确定输入和输出。B. 逻辑赋值定义了输入和输出的状态。C. 列出并根据因果关系完成真值表。D. 使用逻辑代数方法简化逻辑函数。E. 将简化后的逻辑函数转化为实际的电路图。 3. **全加器或全减器设计**:全加器用于加法运算,全减器则用于减法运算。通过74LS86异或门和74LS00与非门的组合,可以构建这些逻辑单元,通过改变输入信号,观察输出和进位/借位信号,验证其功能。 【实验内容】 1. **TTL门电路逻辑功能验证**:使用74LS00和74LS04等集成门电路,验证它们的逻辑功能,如异或门和与非门,通过真值表验证其逻辑特性。 2. **全加器或全减器设计**:利用74LS86异或门和74LS00与非门搭建全加器或全减器电路,根据真值表输入逻辑信号,观察并记录输出和进位/借位信号。 【实验设备与器材】 实验所需的设备包括数字逻辑试验箱、导线、74LS00、74LS04和74LS86等集成器件。 【实验步骤与结果分析】 1. 对异或门、与非门进行了逻辑功能验证,通过真值表对比实验结果,确保了逻辑门的正确性。 2. 设计并实现了简单的组合逻辑电路,验证了逻辑操作的正确性。 3. 构建了全加器或全减器电路,通过输入不同逻辑电平信号,验证了其加法和减法功能,同时记录了进位/借位情况。 【总结分析】 这次实验强调了对数字逻辑基础知识的理解和实际操作技能的培养。实验过程中,团队合作、安全操作和细心分析的重要性得到了体现。通过实验,学生不仅熟悉了实验设备,还学会了如何正确使用和保护集成电路。同时,实验过程中的错误和挑战也让学生意识到在复杂电路设计时需要具备的细心和耐心,以及团队协作的价值。

剩余17页未读,继续阅读

- 粉丝: 25

- 资源: 315

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 基于Java与前端技术的全国实时疫情信息网站设计源码

- 基于鸿蒙系统的HarmonyHttpClient设计源码,纯Java实现类似OkHttp的HttpNet框架与优雅的Retrofit注解解析

- 基于HTML和JavaScript的廖振宇图书馆前端设计源码

- 基于Java的Android开发工具集合源码

- 通过 DirectX 12 Hook (kiero) 实现通用 ImGui.zip

- 基于Java开发的YY网盘个人网盘设计源码

- 通过 DirectX 11 基于 GPU 调整图像大小.zip

- 通用 DirectX.zip

- 基于Python语言的推荐系统设计源码推荐

- 通用 C++,DirectX 游戏引擎模板.zip

信息提交成功

信息提交成功

评论0