北大计算机系高级计算机系统结构课件chx14-arch06-vliw1

需积分: 0 142 浏览量

更新于2022-08-03

收藏 1.65MB PDF 举报

点数较多,以下将详细解析相关知识点:

**高级计算机系统结构**

这门课程涉及的是计算机系统的核心设计原理,包括微处理器、流水线技术、指令级并行性(ILP)以及超长指令字(VLIW)架构。课程的重点在于理解和优化计算机内部的工作流程,以提高性能。

**基于静态调度的ILP**

ILP(Instruction-Level Parallelism)是指在同一时间片内处理多条指令的能力。静态调度是一种在编译阶段确定指令执行顺序的方法,它预先分析代码并安排指令以最大化并行性。这种方法有助于在超标量处理器中更有效地利用资源,通过预测和避免潜在的数据冲突来提高执行效率。

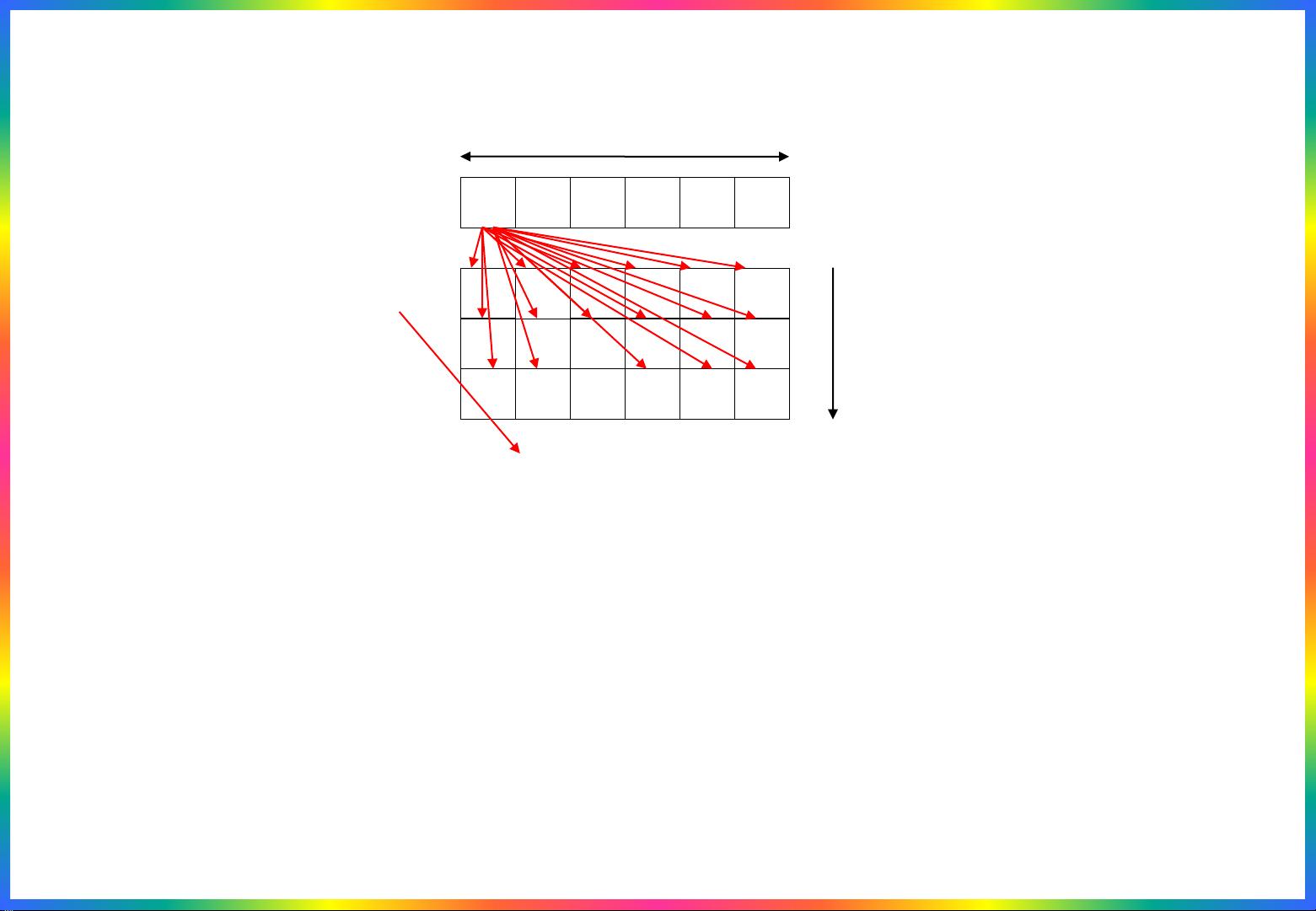

**VLIW(Very Long Instruction Word)**

VLIW架构是将多个操作打包在一个指令中,每个操作槽对应一个固定的函数。这样做的好处是可以确保在同一时钟周期内执行多个操作,从而实现指令级并行。VLIW设计强调了指令间的并行性,减少了指令检查(如RAW检查,即Read-After-Write)和数据互锁,以实现更高的并行计算能力。

**超标量技术**

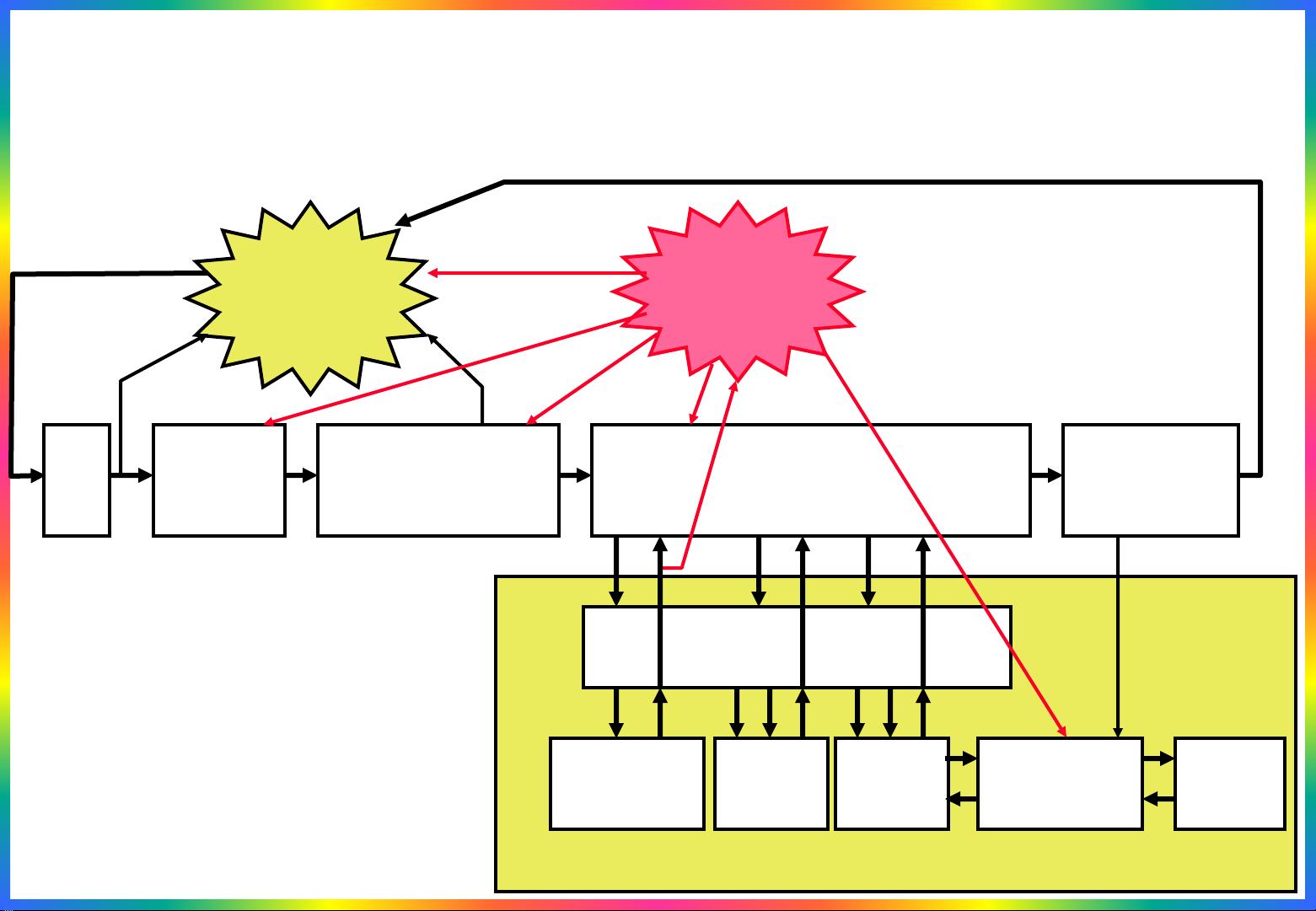

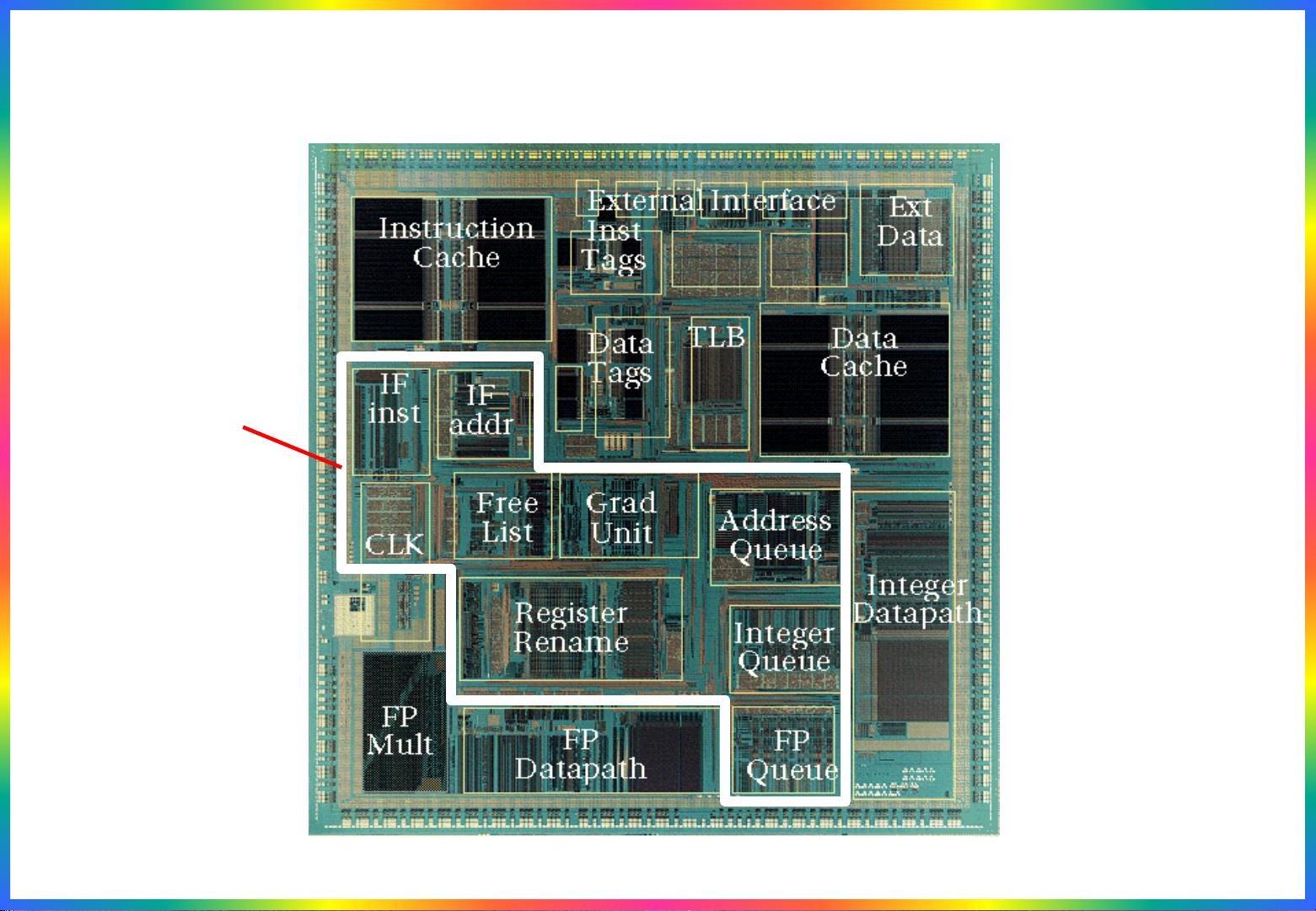

超标量处理器能够在单个时钟周期内执行多条指令,通过使用多个执行单元和指令重排序(Reorder Buffer)来实现。这种技术包括转移预测、推测式执行和物理寄存器堆的设计优化,以减少流水线停顿和提高效率。例如,简单的转移预测技术能有效提升性能,而基于路径的预测器可以达到95%以上的正确率。同时,超标量处理器还需要推测式存储缓冲器来处理存储操作,以避免等待确认而造成的延迟。

**控制逻辑的可扩展性**

随着处理器发令宽度(Issue Width,即W)的增加,控制逻辑的复杂度也显著上升。每条新发射的指令都需要与流水线中的其他指令检查相关性,导致硬件规模以W的指数级增长。乱序执行机器的控制逻辑尤其复杂,因为它需要处理更大的指令窗口,包括指令缓冲器(ROB)中的指令,这使得逻辑复杂度增长速度超过W的平方,接近W的立方。

**处理器设计的挑战**

在优化处理器设计时,需要平衡控制逻辑的复杂性和性能。例如,乱序控制逻辑如MIPS R10000的复杂设计展示了在实现高性能乱序执行时面临的工程挑战。此外,串行ISA(指令集架构)到并行执行的转换是编译器的任务,需要找出独立的操作并进行调度,以充分利用超长指令字的优势。

这门课程深入探讨了高级计算机系统结构中的关键概念和技术,特别是如何通过VLIW和超标量设计提高处理器性能,以及如何通过优化控制逻辑和编译策略来实现并行执行。这些知识对于理解现代处理器工作原理至关重要。