简单组合逻辑电路_张程远_20170114291

需积分: 0 80 浏览量

更新于2022-08-08

收藏 1.19MB DOCX 举报

简单组合逻辑电路是数字电子技术中的基础组成部分,它主要由小规模集成电路构成,用于执行特定的逻辑运算。在这个实验中,我们关注的重点是全加运算和减法运算电路的设计,以及原码、反码和补码的概念应用。

一、原码、反码和补码的概念

原码是最直接表示一个数字的二进制形式,正数的原码与其数值相同,负数的最高位(符号位)为1,其余位与对应的正数相同。反码是正数不变,负数除符号位外其他各位按位取反。补码则是正数不变,负数的补码是其反码加1,它用于表示负数并在计算中避免溢出。

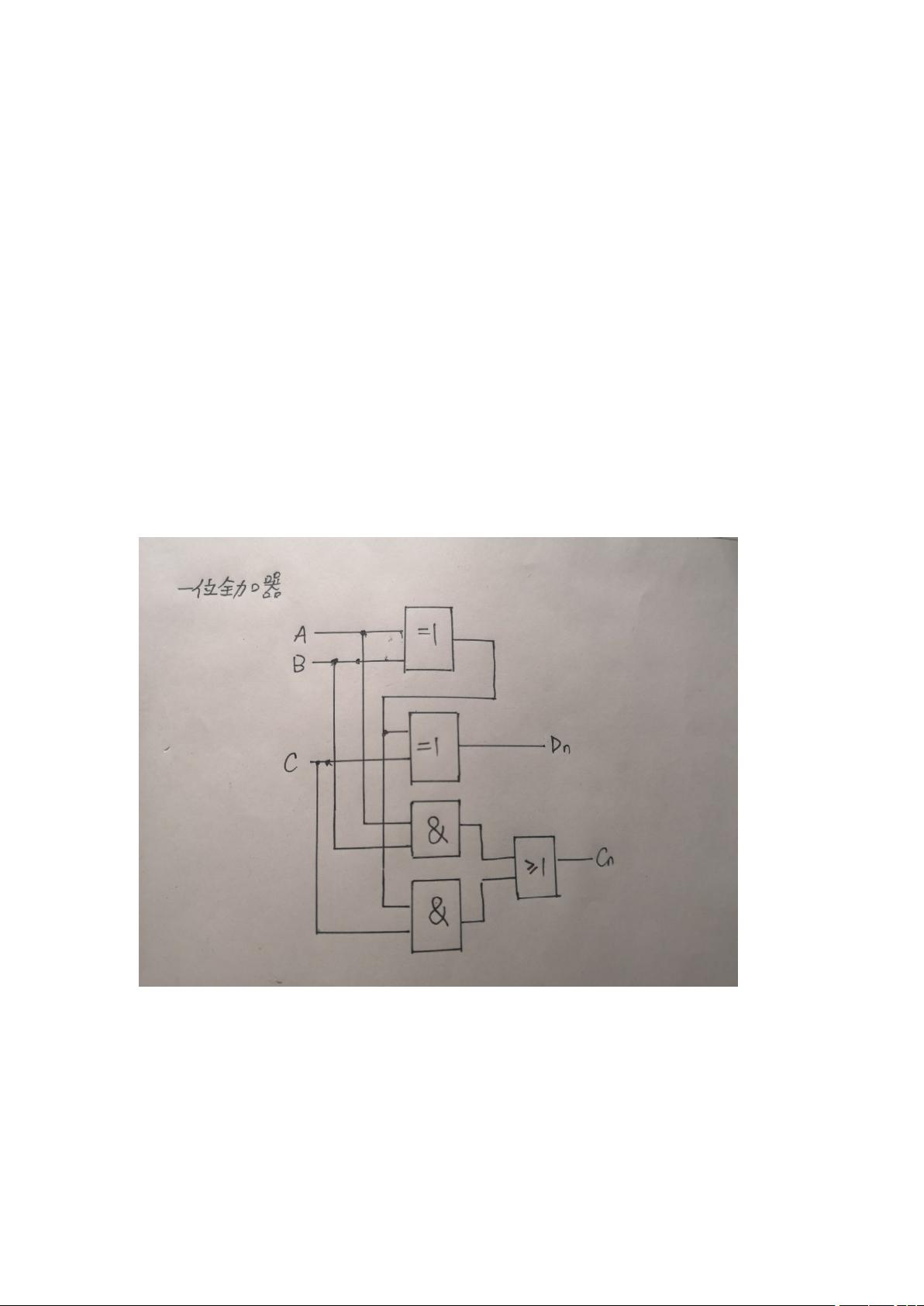

二、全加运算电路

全加器是组合逻辑电路的一种,能完成两个二进制数的加法和进位功能。一位全加器接受两个输入A和B,以及上一位的进位Cin,产生和S以及本位的进位Cout。两位全加器则是两个一位全加器的组合,考虑了高位的进位,可以完成两个二进制数的两位加法。

三、减法运算电路

减法运算电路可以通过全加器实现,利用补码表示负数。在减法中,被减数B转换为其补码,然后与减数A进行加法运算。如果A大于等于B,结果为正,直接显示;如果A小于B,结果为负,需要用补码表示,并显示借位信息。在实验的第二部分,当A大于等于B时,数码管显示差值,否则显示补码表示的差值,借位用发光二极管表示。

四、改进的两位减法运算

改进的减法运算电路在A小于B时,不仅显示负号,还会显示用原码表示的差值。这意味着在减法运算过程中,不仅处理了借位和补码,还对负数的原码进行了显示。

五、实验流程与设计思路

实验设计涉及的流程包括判断除数是否为0,然后根据被除数与除数的关系进行减法运算,输出商和余数。流程图可以帮助我们清晰地理解这个过程,通过逻辑门(如AND、OR、NOT等)的组合实现相应的逻辑功能。

六、实验挑战与解决策略

实验的难点在于接线,由于元件多、线路复杂,容易造成混淆。为了解决这个问题,可以采用不同颜色的电线区分不同的输入输出,记录关键节点的值,并确保每个模块的电源连接正确。遇到因VCC未接导致的问题,反映出对接线的严谨性还需提高,以后需要更加细心检查。

这次实验深化了对组合逻辑电路的理解,特别是全加器和减法器的设计,同时也强调了实际操作中的组织和检查技巧,这对于提升电子工程技能至关重要。

芊暖

- 粉丝: 28

- 资源: 339

最新资源

- 考虑条件风险价值的多微网主从-合作博弈动态定价与优化调度模型 摘要:代码主要做的是多微网的能量交互与动态定价问题 代码整体采用主从博弈框架,上层是零商的动态定价模型,同时考虑了条件风险价值,对不确定

- springboot项目毕业就业信息管理系统的设计与实现.zip

- springboot项目安康学院新型冠状病毒肺炎疫情防控专题网站的设计与实现.zip

- springboot项目毕业生实习与就业管理系统的设计与实现.zip

- 基于YOLOv8的课堂学生行为检测系统源码+设计报告.zip

- springboot项目车辆管理系统.zip

- springboot项目大学生科创项目在线管理系统的设计与实现.zip

- springboot项目电影订票及评论网站的设计与实现.zip

- springboot项目高校专业实习管理系统的设计和开发.zip

- springboot项目反欺诈平台的建设.zip

- springboot项目付费问答系统的设计与实现.zip

- springboot项目基于BS的社区物业管理系统.zip

- springboot项目火锅店管理系统.zip

- springboot项目基于BS的老年人体检管理系统.zip

- 自动化顶升剥料贴膜组装流水线sw18可编辑全套技术资料100%好用.zip

- springboot项目基于HTML的问卷调查系统的设计与实现.zip