没有合适的资源?快使用搜索试试~ 我知道了~

第六章 习题解答1. IO 接口的一般结构包括哪些部分?它们各具有什么功能?解答:接口电路主要由控制命令逻辑电路、状态设置和存储电路、数据存储和缓冲电路3部分组

资源详情

资源评论

资源推荐

第六章 习题解答

1. IO 接口的一般结构包括哪些部分?它们各具有什么功能?

解答:接口电路主要由控制命令逻辑电路、状态设置和存储电路、数据存储和缓冲电路3部

分组成

控制命令逻辑电路一般由命令寄存器和控制执行逻辑组成,这一部分是接口电路的“中

央处理器”,用来完成全部接口操作的控制。

状态设置和存储电路主要由一组状态寄存器构成,中央处理器和外设就是根据状态寄存

器的内容进行协调动作的。

数据存储和缓冲电路也是一组寄存器,用于暂存中央处理器和外设之间传送的数据,以

完成速度匹配工作。

2. IO 接口的数据通信方式分为几类?各有什么优缺点?各自主要的应用场景有哪些?

解答:

只有两种:串行传送和并行传送。

并行数据的每一位都对应独立的传输线路,所以数据传送速度快,但线路多,一般只用于较

短距离的数据传送。

串行数据传送主要用于远程终端或经过公共电话网的计算机之间的通信。远距离数据传送采

用串行方式比较经济。但串行数据传送比并行数据传送控制复杂,要求收发双方遵从统一的

通讯协议。

3. IO 接口的通信控制方式有哪些?分别具有什么特点?

解答:

查询、中断和DMA 3种方式控制接口的传送操作。

查询方式是中央处理器在数据传送之前通过接口的状态设置存储电路询问外设,待外设允许

传送数据后才传送数据的操作方式。在查询方式下,中央处理器需要花费较多的时间去不断

地“询问”外设,外设的接口电路处于被动状态。

中断方式是在外设要与中央处理器传送数据时,外设向中央处理器发出请求,中央处理器响

应后再传送数据的操作方式。在中断方式下,中央处理器不必查询外设,而由接口在外设的

输出数据发送完毕或接收数据准备好时通知中央处理器,中央处理器再发送或接收数据。

DMA方式是数据不经过中央处理器在存储器和外设之间直接传送的操作方式。DMA方式是

这3种方式中效率最高的一种传送方式,DMA方式控制接口也最复杂,需要专用的DMA控制

器。

4. IO 接口寻址方式分为几类?各有什么优缺点?

解答:

有两种不同的I/O接口寻址方式:一种是标准的I/O寻址,另一种是存储器映象I/O寻址

(memory mapped I/O)。

存储器映象 I/O 寻址方式的优点是:

(1)CPU 对外设的操作可使用全部的存储器操作指令,故指令多,使用方便,如可对

外设中的数据(存于外设的寄存器中)进行算术和逻辑运算,进行循环或移位等;

(2)存储器和外设的地址分布图是同一个;

(3)不需要专门的输入/输出指令。

其缺点是:

(1)外设占用了内存单元,使内存容量减小;

(2)存储器操作指令通常要比I/O指令的字节多,故加长了I/O操作的时间。

标准I/O寻址方式优缺点正好相反。

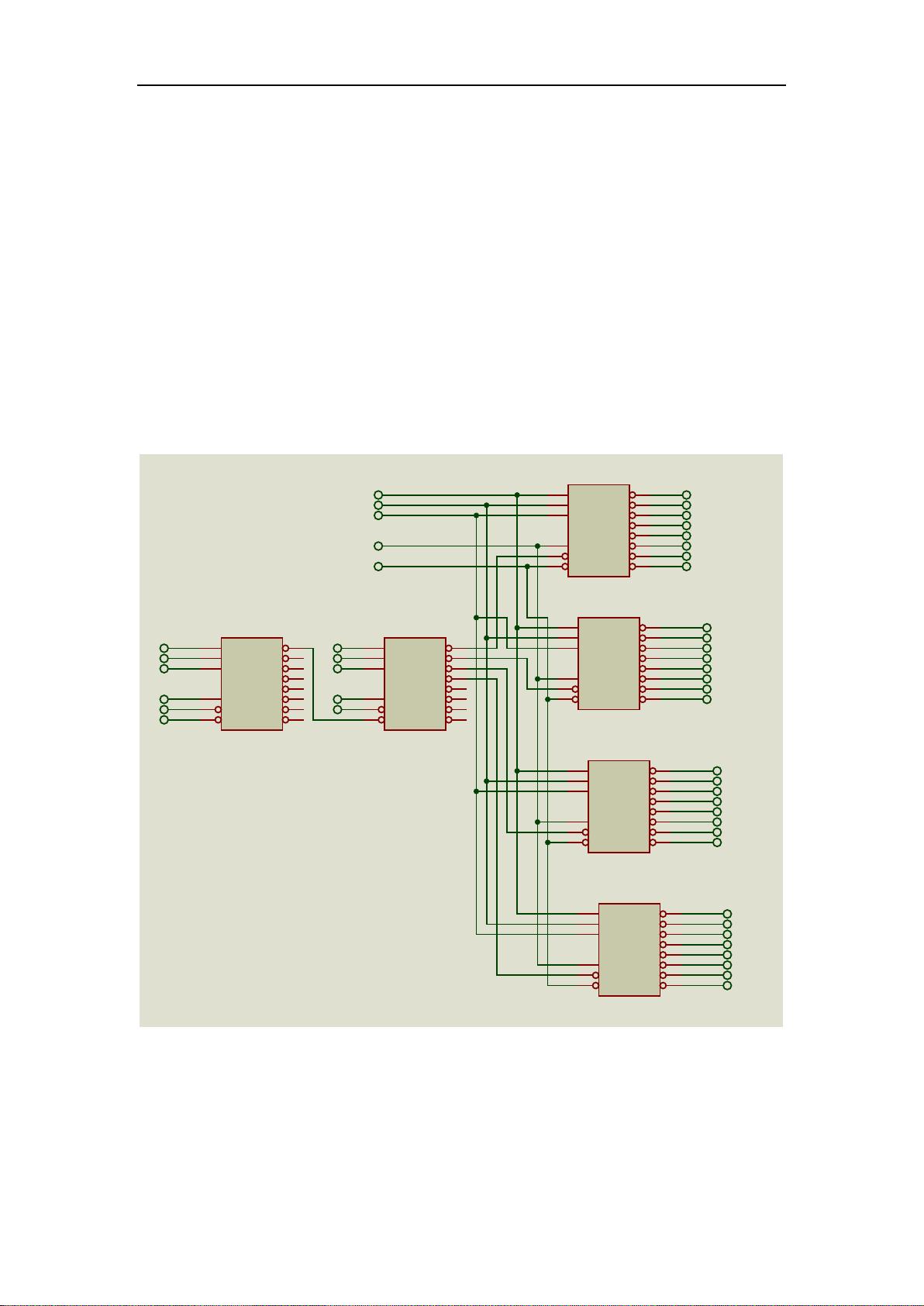

5. 设某16 位地址总线的接口要求端口地址范围为0x2A0H~0x2BF,试仅用138 译码器设计

端口译码电路,并写出各输出端的地址。

解答:16位地址总线,表示提供了A0~A15地址信号,端口地址范围为0x2A0H~0x2BF,由此

可知A15~A5固定为:0000 0010 101;A4~A0可以任意变化,因此需要将A15~A5参与译码,形

成138的使能信号,而A4~A0形成各个具体端口地址的选择信号,共32个不同的端口地址,

每片138可以提供8个不同的端口地址,由此可知需要4片138,而这4片138需要4个不同的使

能信号,因此又需要一片138,这片138共6个输入端,2个输入端为地址选择,剩余的4个输

入端可以连接高位地址信号。电路原理图如下图所示。

A

1

B

2

C

3

E1

6

E2

4

E3

5

Y0

15

Y1

14

Y2

13

Y3

12

Y4

11

Y5

10

Y6

9

Y7

7

U3

74LS138

A

1

B

2

C

3

E1

6

E2

4

E3

5

Y0

15

Y1

14

Y2

13

Y3

12

Y4

11

Y5

10

Y6

9

Y7

7

U4

74LS138

A

1

B

2

C

3

E1

6

E2

4

E3

5

Y0

15

Y1

14

Y2

13

Y3

12

Y4

11

Y5

10

Y6

9

Y7

7

U5

74LS138

A

1

B

2

C

3

E1

6

E2

4

E3

5

Y0

15

Y1

14

Y2

13

Y3

12

Y4

11

Y5

10

Y6

9

Y7

7

U6

74LS138

A

1

B

2

C

3

E1

6

E2

4

E3

5

Y0

15

Y1

14

Y2

13

Y3

12

Y4

11

Y5

10

Y6

9

Y7

7

U2

74LS138

A

1

B

2

C

3

E1

6

E2

4

E3

5

Y0

15

Y1

14

Y2

13

Y3

12

Y4

11

Y5

10

Y6

9

Y7

7

U1

74LS138

A1

A2

A0

A5

A6

A3

A4

A8

A7

A10

A11

A12

A13

A9

A14

A15

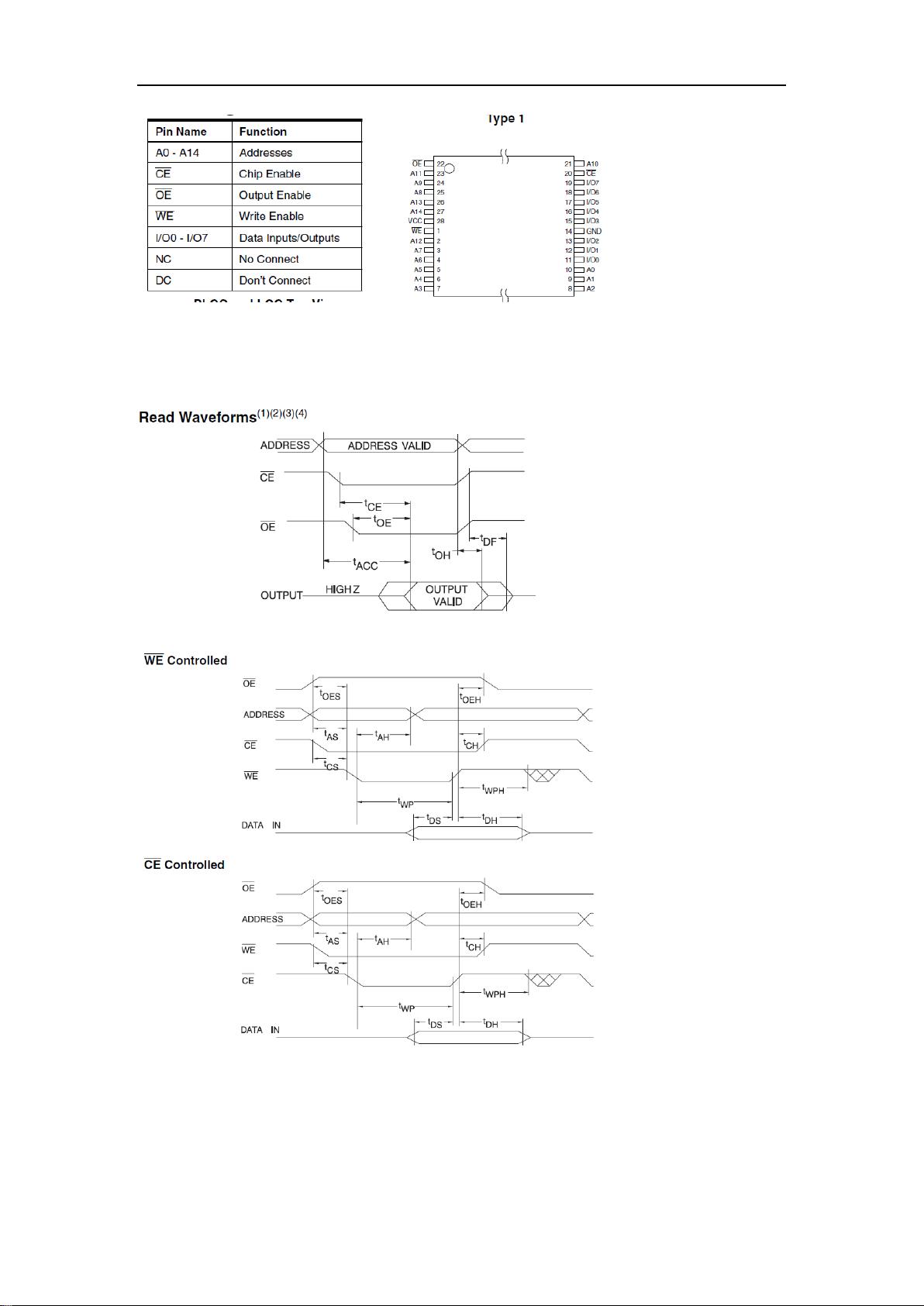

6. 通过查阅存储芯片AT29C256 的数据手册,说明该存储芯片的容量,地址线、数据线宽度

以及读写操作时序。

解答:

地址线:15位

数据线:8位

容量:32KB

读时序图:

写时序图:

7. 试为一个32 位的微处理器设计一个存储容量为128K*32b 的SRAM 存储器,要求采用

SRAM 62256 存储芯片,并且该存储器需能支持字节、半字以及字类型的数据访问。

解答:128K*32b的SRAM存储器共需32位数据线(D0~D31),19根地址线(A0~A18),由于要

支持字节、半字以及字类型的数据访问,因此提供字节使能信号BE0,BE1,BE2,BE3,从而

剩余11页未读,继续阅读

Jaihwoe

- 粉丝: 18

- 资源: 350

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0