Volume 3 :Chapter 29. 仿真HPS 组件2

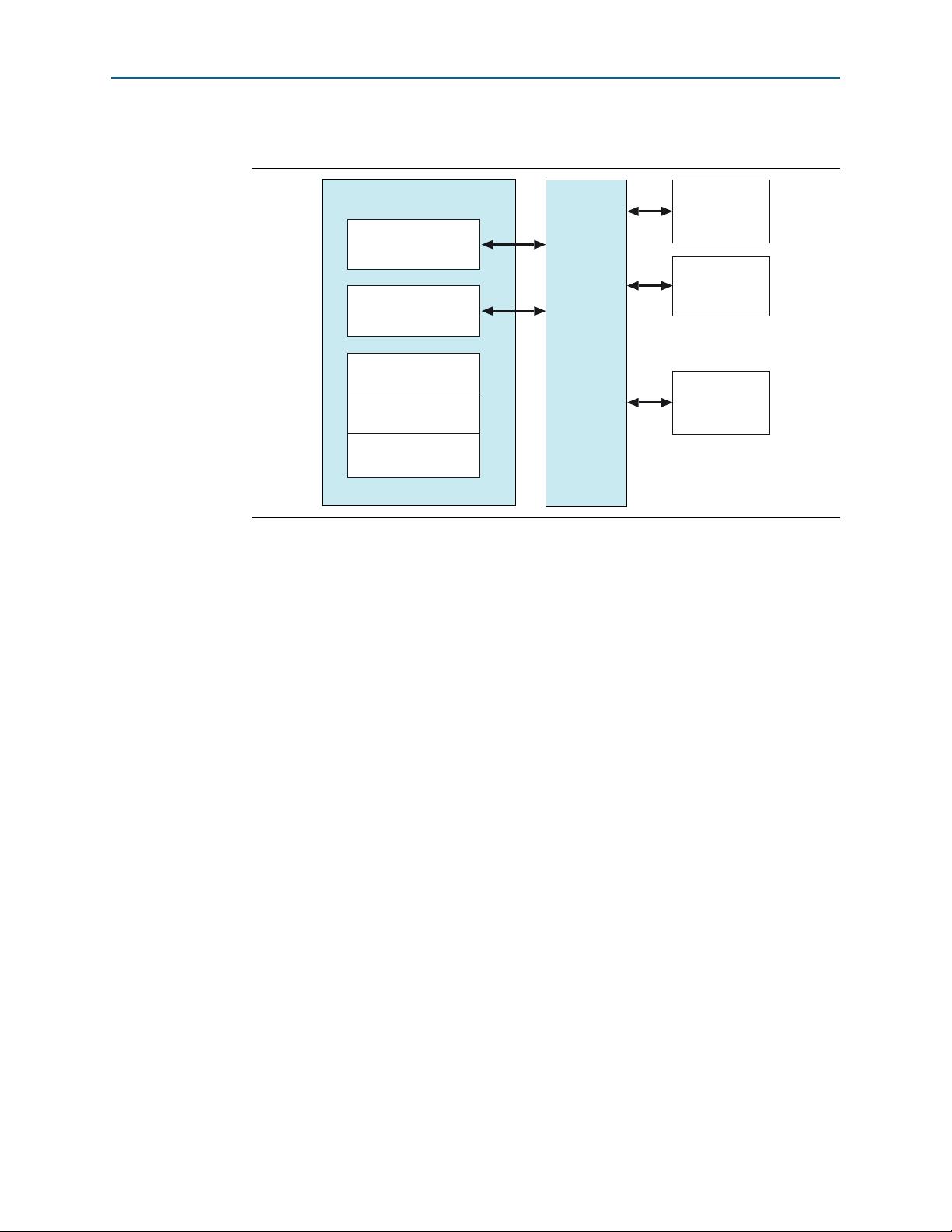

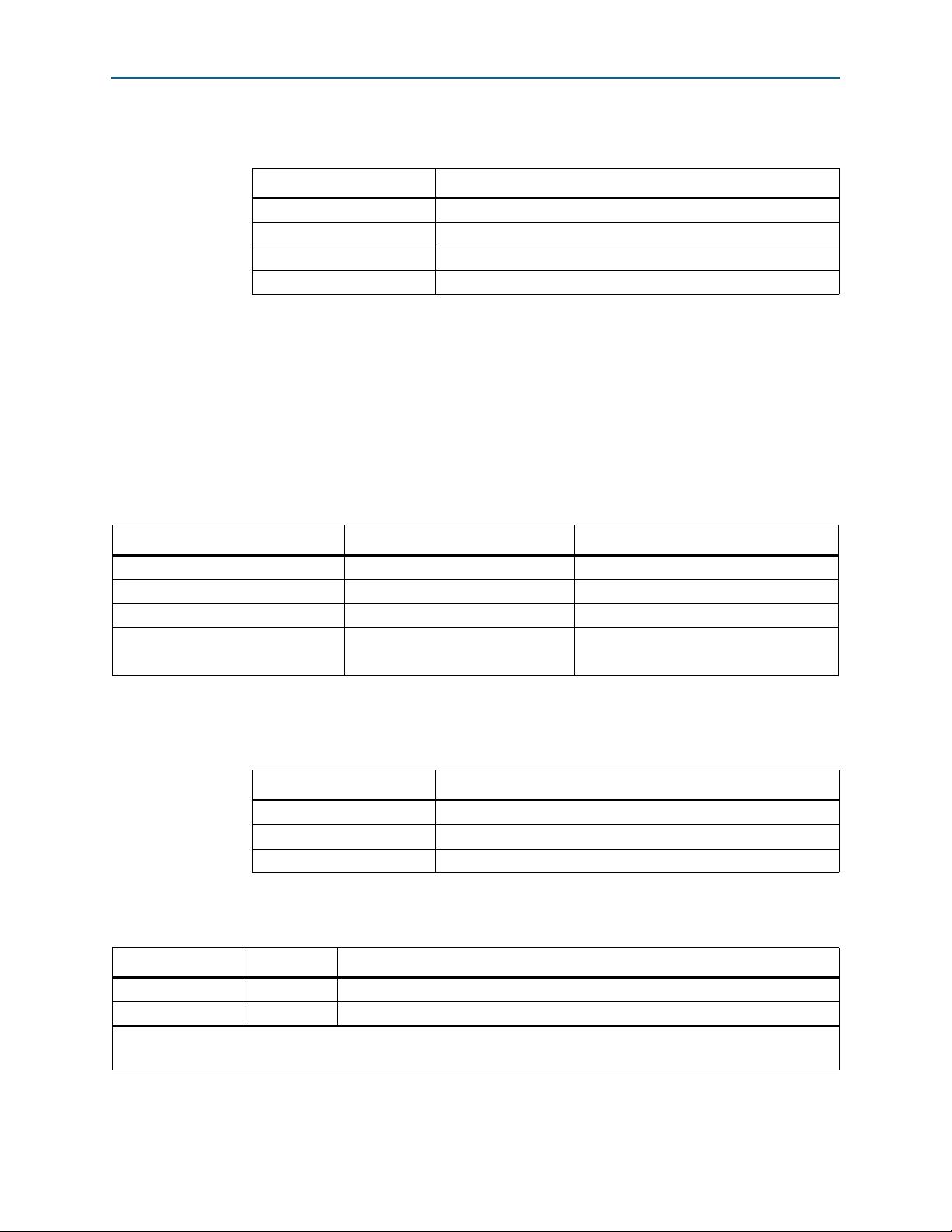

《硬核处理器系统(HPS)组件的仿真支持详解》 在电子设计领域,尤其是在使用Cyclone V器件的系统中,硬核处理器系统(HPS)的仿真组件扮演着至关重要的角色。本章节主要探讨HPS组件的仿真支持,旨在帮助开发者理解和应用这些组件,以实现与FPGA内核逻辑的有效交互。 HPS仿真模型涵盖了HPS与FPGA之间接口的全面功能模拟,包括总线功能模型(BFMs)和SDRAM存储器的仿真。这些模型不仅使得开发者能在设计阶段就测试接口的正确性,还允许对HPS与FPGA间的通信进行验证。然而,值得注意的是,HPS仿真并不包括如ARM Cortex-A9 MPCore处理器等在HPS内部实现的具体模块。 在使用Qsys系统集成工具实例化HPS组件时,必须指定仿真支持文件。Qsys会在生成过程中自动提供与所选HPS-FPGA接口对应的模型,简化了设计流程。想要深入了解仿真流程,可以查阅"仿真流程"部分(第29-8页),这里详细介绍了从设置到验证的整个过程。 Cyclone V器件手册第三卷中的"Instantiating the HPS Component"章节提供了关于实例化组件的详细指导,这对于理解如何将HPS组件整合进FPGA设计至关重要。仿真支持覆盖了多种接口,如: 1. 时钟和复位接口:确保系统时序的准确同步。 2. FPGA-to-HPS AMBA AXI从接口:用于FPGA向HPS传输数据。 3. HPS-to-FPGA AXI主接口:允许HPS控制FPGA的逻辑。 4. 轻型HPS-to-FPGA AXI主接口:为低带宽应用提供高效接口。 5. FPGA-to-HPS SDRAM接口:处理与HPS内存的交互。 6. MPU通用I/O接口:处理微处理器单元的输入输出操作。 7. MPU备用和事件接口:处理MPU的额外功能和事件响应。 8. 中断接口:支持快速响应外部或内部中断请求。 9. DMA控制器外设请求接口:优化内存访问性能。 10. 调试APB接口:为系统调试提供便利。 11. 系统跟踪宏单元(STM)硬件事件:记录系统行为以供分析。 12. FPGA交叉触发接口和跟踪端口接口:提升调试效率和精度。 图29-1(位于第29-2页)直观展示了HPS中的BFM结构,清晰地呈现了各个接口的相互作用。Altera的BFM API提供了标准化的函数调用,简化了开发者与这些模型的交互,从而加速了设计验证和调试过程。 HPS组件的仿真支持是确保基于Cyclone V器件的系统设计正确性和可靠性的关键环节。通过理解和熟练运用这些仿真工具,开发者可以更高效地开发和验证与HPS连接的FPGA软逻辑或知识产权(IP),从而推动复杂电子系统的设计和实现。

剩余13页未读,继续阅读

- 粉丝: 26

- 资源: 318

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- MATLAB界面版本-疲劳专注度检测系统.zip

- MATLAB界面版本-疲劳检测GUI设计.zip

- MATLAB界面版本-苹果水果分级.zip

- MATLAB界面版本-脐橙水果分级.zip

- MATLAB界面版本-漂浮物识别.zip

- MATLAB界面版本-人脸门禁系统.zip

- MATLAB界面版本-人脸考勤设计.zip

- MATLAB界面版本-人脸购物系统.zip

- MATLAB界面版本-人脸识别.zip

- MATLAB界面版本-手势控制系统.zip

- MATLAB界面版本-人脸识别系统.zip

- MATLAB界面版本-手势识别设计.zip

- MATLAB界面版本-手势识别.zip

- MATLAB界面版本-手势识别系统.zip

- MATLAB界面版本-数字信号处理.zip

- MATLAB界面版本-数字信号处理GUI设计.zip

信息提交成功

信息提交成功

评论0