小崔个人精进录

- 粉丝: 39

- 资源: 316

最新资源

- 基于S7-200 PLC的饮料自动装箱机控制系统:梯形图接线图原理及IO分配与组态画面详解,基于S7-200 PLC与组态王界面的饮料自动装箱机控制系统设计与实施:原理图、IO分配及梯形图接线图解析

- 本科课设低速轴齿轮参考cad图

- 基于三菱PLC与MCGS的饮料灌装全自动控制系统:梯形图程序详解、接线图与IO分配及组态展示,基于三菱PLC与MCGS的饮料灌装自动控制:专业解析梯形图程序、接线图原理与IO分配及组态界面设计,基于三

- 中科大DSP2第一次上机作业-LMS计算机练习

- 基于S7-200 PLC的饮料灌装机综合控制系统详解:梯形图程序、接线图、IO配置与组态设计,基于S7-200 PLC的饮料灌装机控制系统详解:梯形图程序、接线图与IO配置实践,基于S7-200 PL

- 基于三菱PLC与MCGS组态音乐喷泉控制教程:涵盖梯形图程序、接线图及原理图的全方位解决方案,基于三菱PLC与MCGS组态的音乐喷泉智能控制系统:梯形图程序、接线图与组态设计,基于三菱PLC和MCGS

- 基于欧姆龙PLC的智能音乐喷泉控制系统设计与实现:电气控制、梯形图程序及图纸详解,基于欧姆龙PLC的花样喷泉智能控制系统设计:涵盖电气控制、音乐同步及详细图纸资料,基于欧姆龙PLC的花样喷泉控制系统设

- 本科课设低速轴参考CAD图纸

- Leaflet学习文档-标注点

- 深入解析ABB变频器功率部分维修原理图:精确导航,助力专业维修人员高效作业,深入解析ABB变频器功率部分维修原理图:细节掌握,高效修复,ABB变频器维修原理图 仅有功率部分,不含主板 ,ABB

- 单个螺栓含螺纹网格全部六面体(60万)

- Java 反编译工具,win版,版本1.5.1

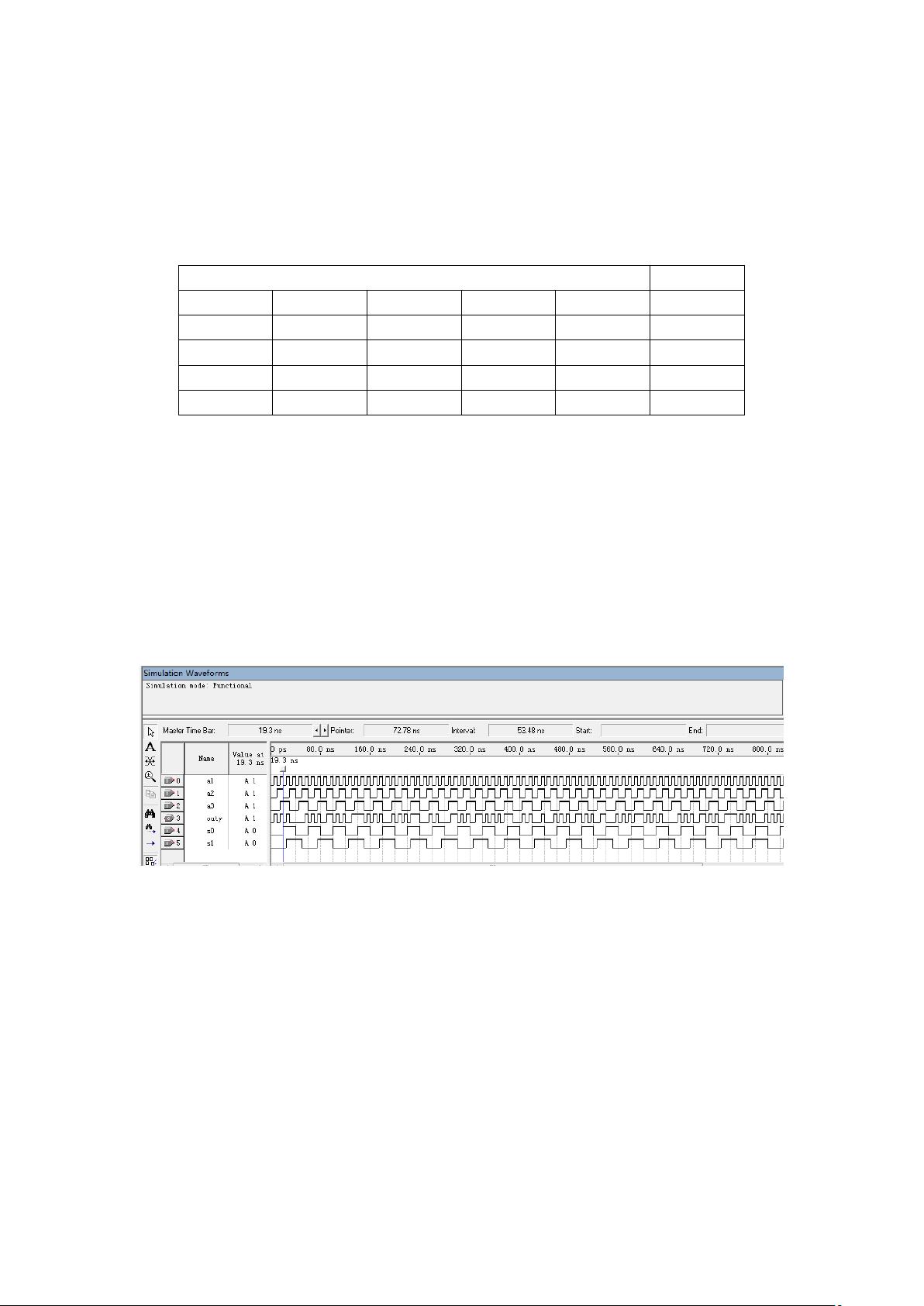

- 51学习相关资料源码原理图等

- 基于STM32的智能水产养殖系统(含代码、电路、参考论文)

- 中科大DSP2第二次上机作业

- 长短记忆网络LSTM(MATLAB):分类与回归问题的算法优化与实践教程,长短记忆网络LSTM教程:用MATLAB解决分类与回归问题,数据替换简易操作,集成多种智能算法优化预测模型,长短记忆网络LST

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

评论0