Quartus II调用ModelSim进行仿真方法1

需积分: 0 38 浏览量

更新于2022-08-08

1

收藏 198KB DOCX 举报

Quartus II 是一款由 Altera(现已被 Intel 收购)开发的综合设计环境,主要用于FPGA(Field-Programmable Gate Array)和CPLD(Complex Programmable Logic Device)的设计、仿真和编程。在Quartus II 中,集成了一些IP CORE( Intellectual Property Core),这些预定义的功能模块简化了设计过程,但进行逻辑仿真时则需要额外的步骤。ModelSim 是一款广泛使用的硬件描述语言(HDL)仿真器,支持VHDL和Verilog等语言,用于验证数字电路设计。

以下是使用Quartus II调用ModelSim SE进行仿真的详细步骤:

1. **创建工程和添加IP CORE**:

在Quartus II中新建一个工程,并根据需求添加相应的IP CORE。这一步骤是设计的基础,确保所有必要的逻辑模块都已包含在内。

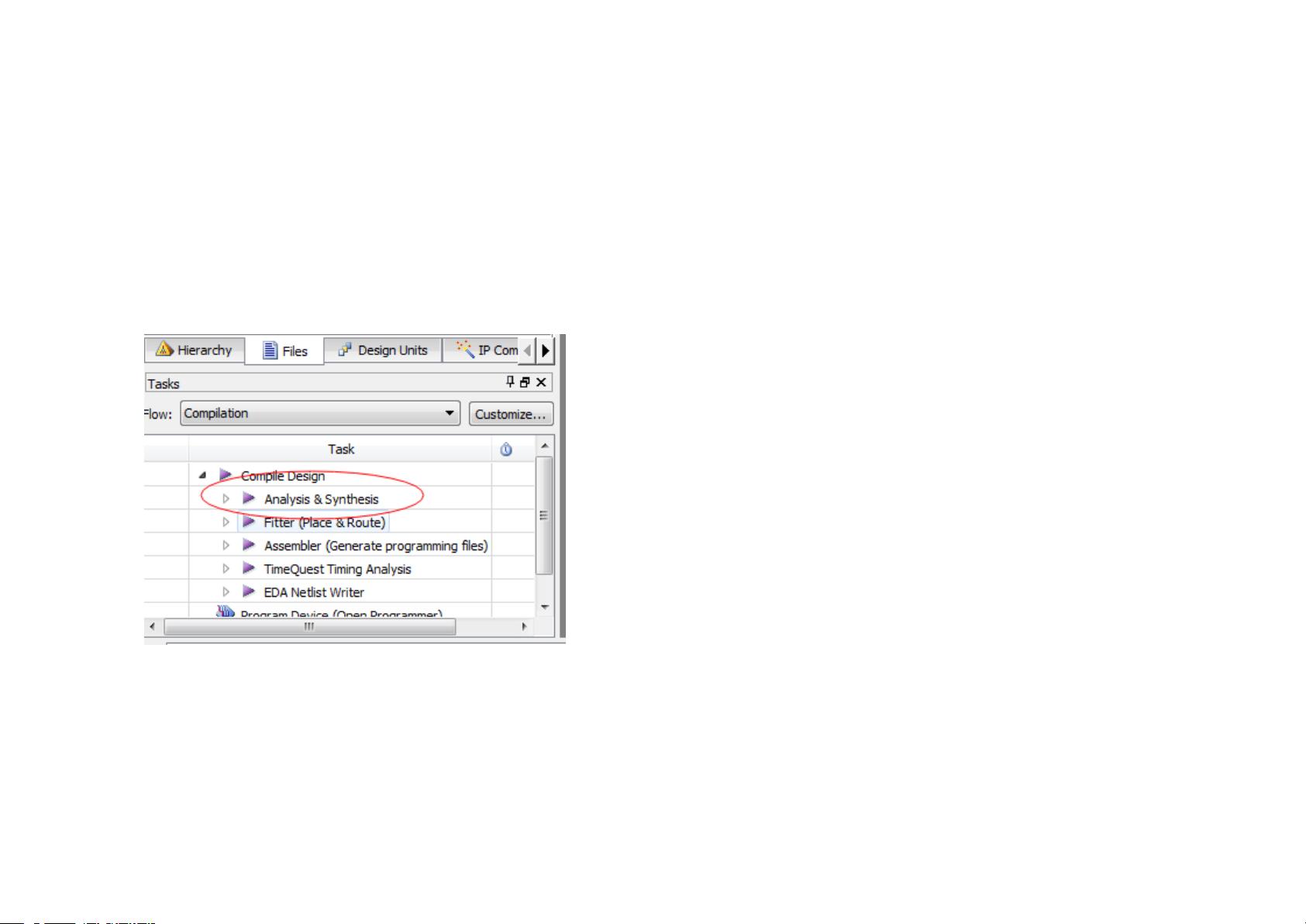

2. **编译设计**:

完成IP CORE的配置后,点击Task菜单中的Analysis & Synthesis,对设计进行编译。这一步会生成门级网表,为后续的仿真做好准备。

3. **配置ModelSim路径**:

进入Tools -> Options,选择EDA Tool Options,设置ModelSim的路径。通常ModelSim的可执行文件位于 `/win32` 或 `/win64` 目录下。确保正确设置,以便Quartus II能够调用ModelSim进行仿真。

4. **设置仿真时间尺度**:

在Assignments菜单中选择Settings,进入EDA Tool Settings,然后选择Simulation选项。在这里,你可以设置仿真时的时间尺度,例如设置为1ns,以便精确控制仿真时间。

5. **生成测试平台模板**:

执行Processing -> Start -> Start test bench Template writer,Quartus II将自动生成一个测试平台模板文件,后缀为.vt,位于工程的simulation\modelsim目录下。

6. **编辑测试平台文件**:

使用文本编辑器(如Quartus II内置的或外部的如vim)打开.vt文件,修改文件扩展名为.v,以及模块名称,将其格式化为标准的Verilog测试平台格式,例如`**_tb.v`和`module **_tb`。

7. **添加测试平台到仿真设置**:

回到Quartus II,通过Assignment -> Settings -> EDA Tool Settings -> Simulation,选择Test Benches,点击New,输入文件名并找到刚修改的`.v`文件,将其添加为测试平台。

8. **启动仿真**:

准备完成后,通过Tools -> Run -> Simulation Tool启动ModelSim进行仿真。此时,Quartus II将调用ModelSim进行设计的逻辑仿真。

9. **查看和调整仿真结果**:

ModelSim会显示仿真的波形图。如果自动优化的波形不符合预期,可以通过End Simulation,然后按照通常的仿真流程手动调整观察点和时间窗口,以获得所需的仿真视图。

注意,在仿真过程中,可能需要编写和修改测试激励,以确保能覆盖设计的所有功能。同时,ModelSim提供的调试工具,如查看变量值、设置断点等,也是进行高效仿真的关键。一旦仿真验证无误,就可以将设计下载到目标FPGA进行实际硬件测试了。

通过以上步骤,你可以有效地利用Quartus II和ModelSim的结合,进行复杂的FPGA设计验证,确保逻辑功能的正确性。在实际项目中,理解并熟练掌握这些步骤对于提升设计效率至关重要。