没有合适的资源?快使用搜索试试~ 我知道了~

drv8313 内置MOS 2.5A 60V 3PWM1

需积分: 0 1 下载量 160 浏览量

2022-08-03

17:42:37

上传

评论

收藏 2.32MB PDF 举报

温馨提示

试读

39页

drv8313 内置MOS 2.5A 60V 3PWM1

资源推荐

资源详情

资源评论

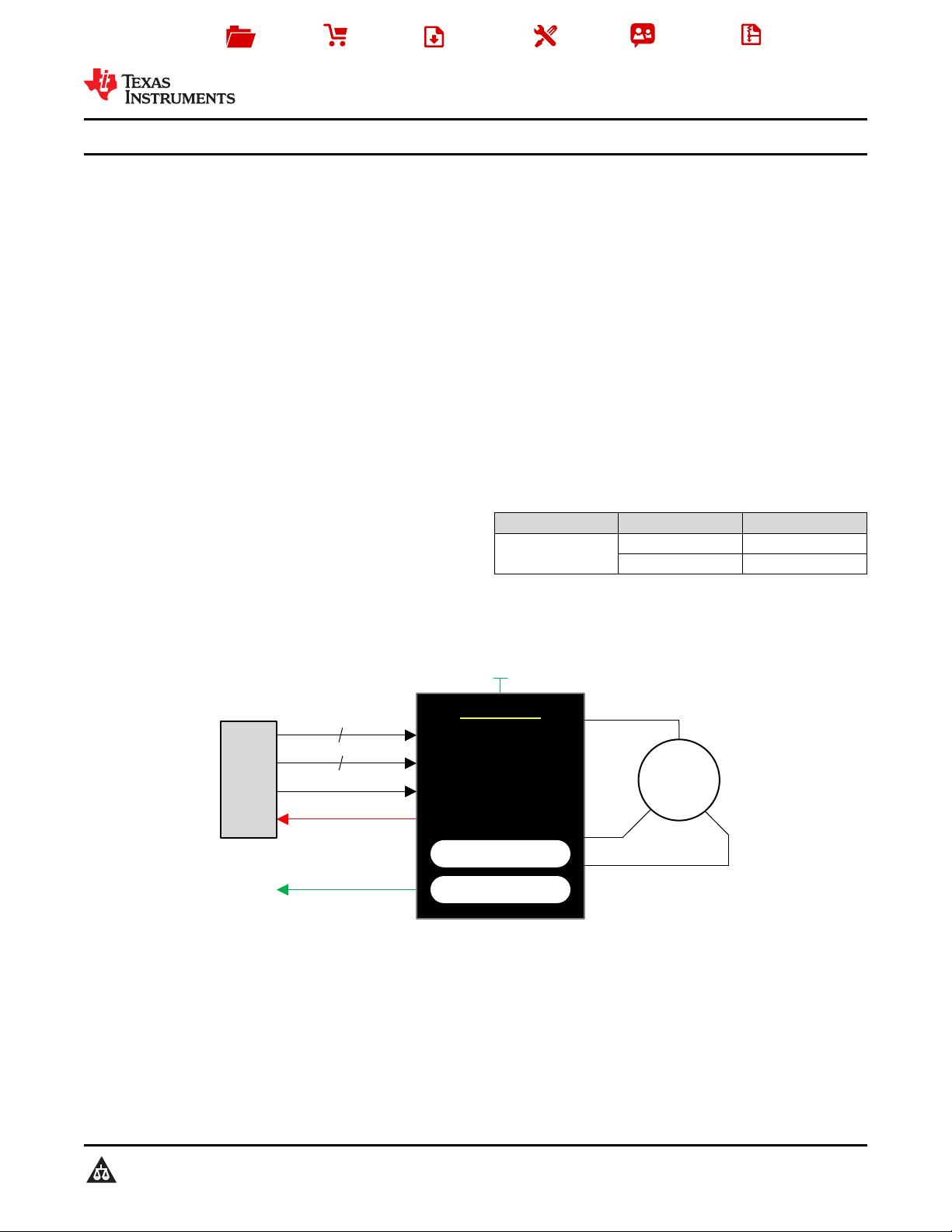

8 to 60 V

DRV8313

3 ½-H Bridge

Driver

IN

EN

Built-In Protection

nFAULT

M

3.3-V LDO

Controller

3.3 V

10 mA

nSLEEP

3.5 A

Copyright © 2016, Texas Instruments Incorporated

Product

Folder

Sample &

Buy

Technical

Documents

Tools &

Software

Support &

Community

Reference

Design

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

DRV8313

SLVSBA5D –OCTOBER 2012–REVISED APRIL 2016

DRV8313 2.5-A Triple 1/2-H Bridge Driver

1

1 Features

1

• Triple 1/2-H Bridge Driver IC

– 3-Phase brushless DC Motors

– Solenoid and Brushed DC Motors

• High Current-Drive Capability: 2.5-A Peak

• Low MOSFET ON-Resistance

• Independent 1/2-H-Bridge Control

• Uncommitted Comparator Can Be Used for

Current Limit or Other Functions

• Built-In 3.3-V 10-mA LDO Regulator

• 8-V to 60-V Operating Supply-Voltage Range

• Sleep Mode for Standby Operation

• Small Package and Footprint

– 28-Pin HTSSOP (PowerPAD™ Package)

– 36-Pin VQFN

2 Applications

• Camera Gimbals

• HVAC Motors

• Office Automation Machines

• Factory Automation and Robotics

3 Description

The DRV8313 provides three individually controllable

half-H-bridge drivers. The device is intended to drive

a three-phase brushless-DC motor, although it can

also be used to drive solenoids or other loads. Each

output driver channel consists of N-channel power

MOSFETs configured in a 1/2-H-bridge configuration.

Each 1/2-H-bridge driver has a dedicated ground

terminal, which allows independent external current

sensing.

An uncommitted comparator is integrated into the

DRV8313, which allows for the construction of

current-limit circuitry or other functions.

Internal protection functions are provided for

undervoltage, charge pump faults, overcurrent, short

circuits, and overtemperature. Fault conditions are

indicated by the nFAULT pin.

Device Information

(1)

PART NUMBER PACKAGE BODY SIZE (NOM)

DRV8313

HTSSOP (28) 9.70 mm × 4.40 mm

VQFN (36) 6.00 mm × 6.00 mm

(1) For all available packages, see the orderable addendum at

the end of the data sheet.

Simplified Schematic

2

DRV8313

SLVSBA5D –OCTOBER 2012–REVISED APRIL 2016

www.ti.com

Product Folder Links: DRV8313

Submit Documentation Feedback Copyright © 2012–2016, Texas Instruments Incorporated

Table of Contents

1 Features.................................................................. 1

2 Applications ........................................................... 1

3 Description ............................................................. 1

4 Revision History..................................................... 2

5 Pin Configuration and Functions......................... 3

6 Specifications......................................................... 4

6.1 Absolute Maximum Ratings ...................................... 4

6.2 ESD Ratings ............................................................ 4

6.3 Recommended Operating Conditions....................... 5

6.4 Thermal Information ................................................. 5

6.5 Electrical Characteristics........................................... 6

6.6 Switching Characteristics.......................................... 7

6.7 Typical Characteristics.............................................. 8

7 Detailed Description............................................ 10

7.1 Overview ................................................................. 10

7.2 Functional Block Diagram ....................................... 10

7.3 Feature Description................................................. 11

7.4 Device Functional Modes........................................ 14

8 Application and Implementation ........................ 15

8.1 Application Information............................................ 15

8.2 Typical Applications ................................................ 15

9 Power Supply Recommendations...................... 22

9.1 Bulk Capacitance .................................................... 22

10 Layout................................................................... 23

10.1 Layout Guidelines ................................................. 23

10.2 Layout Example .................................................... 23

10.3 Thermal Considerations........................................ 25

10.4 Power Dissipation ................................................. 25

11 Device and Documentation Support ................. 26

11.1 Documentation Support ........................................ 26

11.2 Community Resources.......................................... 26

11.3 Trademarks........................................................... 26

11.4 Electrostatic Discharge Caution............................ 26

11.5 Glossary................................................................ 26

12 Mechanical, Packaging, and Orderable

Information ........................................................... 26

4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Changes from Revision C (November 2015) to Revision D Page

• Changed pin 18 of the VQFN (RHH) package from GND to RSVD ...................................................................................... 4

Changes from Revision B (January 2015) to Revision C Page

• Added a new package to the Device Information table ......................................................................................................... 1

• Added a new VQFN package for the device ......................................................................................................................... 3

• Corrected a numbering error on one of the ground pins in the Pin Functions table ............................................................. 3

Changes from Revision A (November 2012) to Revision B Page

• Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation

section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and

Mechanical, Packaging, and Orderable Information section ................................................................................................. 4

Thermal

Pad

36 IN210OUT1

1EN1 27 nSLEEP

35 EN211PGND1

2IN1 26 nRESET

34 IN312PGND2

3GND 25 V3P3

33 EN313OUT2

4NC 24 GND

32 GND14NC

5CPL 23 GND

31 GND15OUT3

6CPH 22 COMPN

30 GND16PGND3

7VCP 21 COMPP

29 nCOMPO17GND

8NC 20 GND

28 nFAULT18RSVD

9VM 19 VM

1CPL 28 GND

2CPH 27 IN1

3VCP 26 EN1

4VM 25 IN2

5OUT1 24 EN2

6PGND1 23 IN3

7PGND2 22 EN3

8OUT2 21 NC

9OUT3 20 GND

10PGND3 19 nCOMPO

11VM 18 nFAULT

12COMPP 17 nSLEEP

13COMPN 16 nRESET

14GND 15 V3P3

3

DRV8313

www.ti.com

SLVSBA5D –OCTOBER 2012–REVISED APRIL 2016

Product Folder Links: DRV8313

Submit Documentation FeedbackCopyright © 2012–2016, Texas Instruments Incorporated

5 Pin Configuration and Functions

PWP Package

28-Pin HTSSOP With PowerPAD Package

Top View

NC - No internal connection

RHH Package

36-Pin VQFN With Exposed Thermal Pad

Top View

(1) I = input, O = output, OD = open-drain output, PWR = power, NC = no connect

Pin Functions

PIN

TYPE

(1)

DESCRIPTION

NAME

NO.

PWP RHH

COMPN 13 22 I Comparator negative input. Uncommitted comparator input

COMPP 12 21 I Comparator positive input. Uncommitted comparator input

CPL 1 5 PWR

Charge pump. Connect a VM-rated, 0.01-µF ceramic capacitor between CPH and

CPL.

CPH 2 6 PWR

Charge pump. Connect a VM-rated, 0.01-µF ceramic capacitor between CPH and

CPL.

EN1 26 1 I Channel enable. Logic high enables the 1/2-H bridge channel; internal pulldown

EN2 24 35 I Channel enable. Logic high enables the 1/2-H bridge channel; internal pulldown

EN3 22 33 I Channel enable. Logic high enables the 1/2-H bridge channel; internal pulldown

GND 14, 20, 28

3, 17, 20,

23, 24, 30,

31, 32,

PWR Device ground. Connect to system ground

IN1 27 2 I

Channel input. Logic high pulls 1/2-H bridge high, logic low pulls 1/2-H bridge low; no

effect when ENx is low; internal pulldown input.

IN2 25 36 I

Channel input. Logic high pulls 1/2-H bridge high, logic low pulls 1/2-H bridge low; no

effect when ENx is low; internal pulldown input.

IN3 23 34 I

Channel input. Logic high pulls 1/2-H bridge high, logic low pulls 1/2-H bridge low; no

effect when ENx is low; internal pulldown input.

NC 21 4, 8, 14 NC No internal connection. Recommended net given in block diagram (if any)

nCOMPO 19 29 OD

Comparator output. Uncommitted comparator output; open drain requires an external

pullup.

nFAULT 18 28 OD

Fault indication pin. Pulled logic-low with fault condition; open-drain output requires an

external pullup.

nRESET 16 26 I

Reset input. Active-low reset input initializes internal logic, clears faults, and disables

the outputs, internal pulldown

4

DRV8313

SLVSBA5D –OCTOBER 2012–REVISED APRIL 2016

www.ti.com

Product Folder Links: DRV8313

Submit Documentation Feedback Copyright © 2012–2016, Texas Instruments Incorporated

Pin Functions (continued)

PIN

TYPE

(1)

DESCRIPTION

NAME

NO.

PWP RHH

nSLEEP 17 27 I

Sleep mode input. Logic high to enable device; logic low to enter low-power sleep

mode; internal pulldown

OUT1 5 10 O Half-H bridge output, connect to the load

OUT2 8 13 O Half-H bridge output, connect to the load

OUT3 9 15 O Half-H bridge output, connect to the load

PGND1 6 11 PWR Low-side FET source. Connect to GND or to low-side current-sense resistors

PGND2 7 12 PWR Low-side FET source. Connect to GND or to low-side current-sense resistors

PGND3 10 16 PWR Low-side FET source. Connect to GND or to low-side current-sense resistors

RSVD — 18 — Reserved. Leave this pin disconnected.

V3P3 15 25 PWR

Internal regulator. Internal supply voltage; bypass to GND with a 6.3-V, 0.47-µF

ceramic capacitor; up to 10-mA external load

VCP 3 7 PWR Charge pump. Connect a 16-V, 0.1-µF ceramic capacitor to VM

VM 4, 11 9, 19 PWR

Power supply. Connect to motor supply voltage; bypass to GND with two 0.1-µF

capacitors (for each pin) plus one bulk capacitor rated for VM

Thermal pad PWR Must be connected to ground

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings

only, and do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended

Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to the network ground terminal.

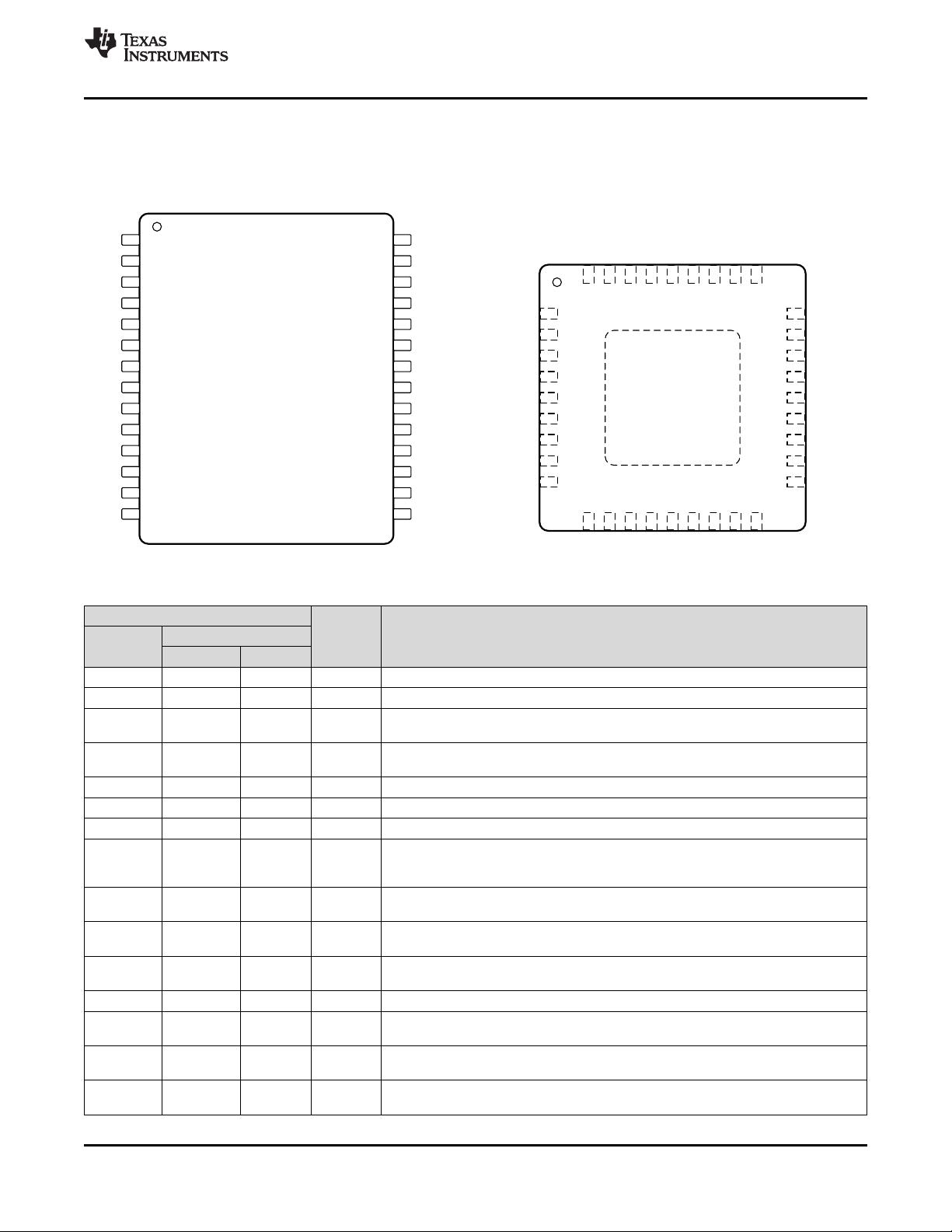

6 Specifications

6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)

(1)(2)

MIN MAX UNIT

Power-supply voltage (VM) –0.3 65 V

Power supply voltage ramp rate (VM) 0 2 V/µs

Charge pump voltage (VCP, CPH) –0.3 VM + 12 V

Charge pump negative switching pin (CPL) –0.3 VM V

Internal regulator current output (V3P3) 0 10 mA

Internal regulator voltage (V3P3) –0.3 3.8 V

Control pin voltage (nRESET, nSLEEP, nFAULT, nCOMPO, ENx, INx) –0.5 7 V

Comparator input-voltage (COMPP, COMPN) –0.5 7 V

Open drain output current (nFAULT, nCOMPO) 0 10 mA

Continuous phase node pin voltage (OUTx) –0.7 VM + 0.7 V

Continuous 1/2-H-bridge source voltage (PGNDx) –600 600 mV

Peak output current (OUTx) Internally limited A

Operating junction temperature T

J

–40 150 °C

Storage temperature T

stg

–60 150 °C

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

6.2 ESD Ratings

VALUE UNIT

V

(ESD)

Electrostatic discharge

Human body model (HBM), per ANSI/ESDA/JEDEC JS-001

(1)

±3000

V

Charged device model (CDM), per JEDEC specification JESD22-C101

(2)

±1500

5

DRV8313

www.ti.com

SLVSBA5D –OCTOBER 2012–REVISED APRIL 2016

Product Folder Links: DRV8313

Submit Documentation FeedbackCopyright © 2012–2016, Texas Instruments Incorporated

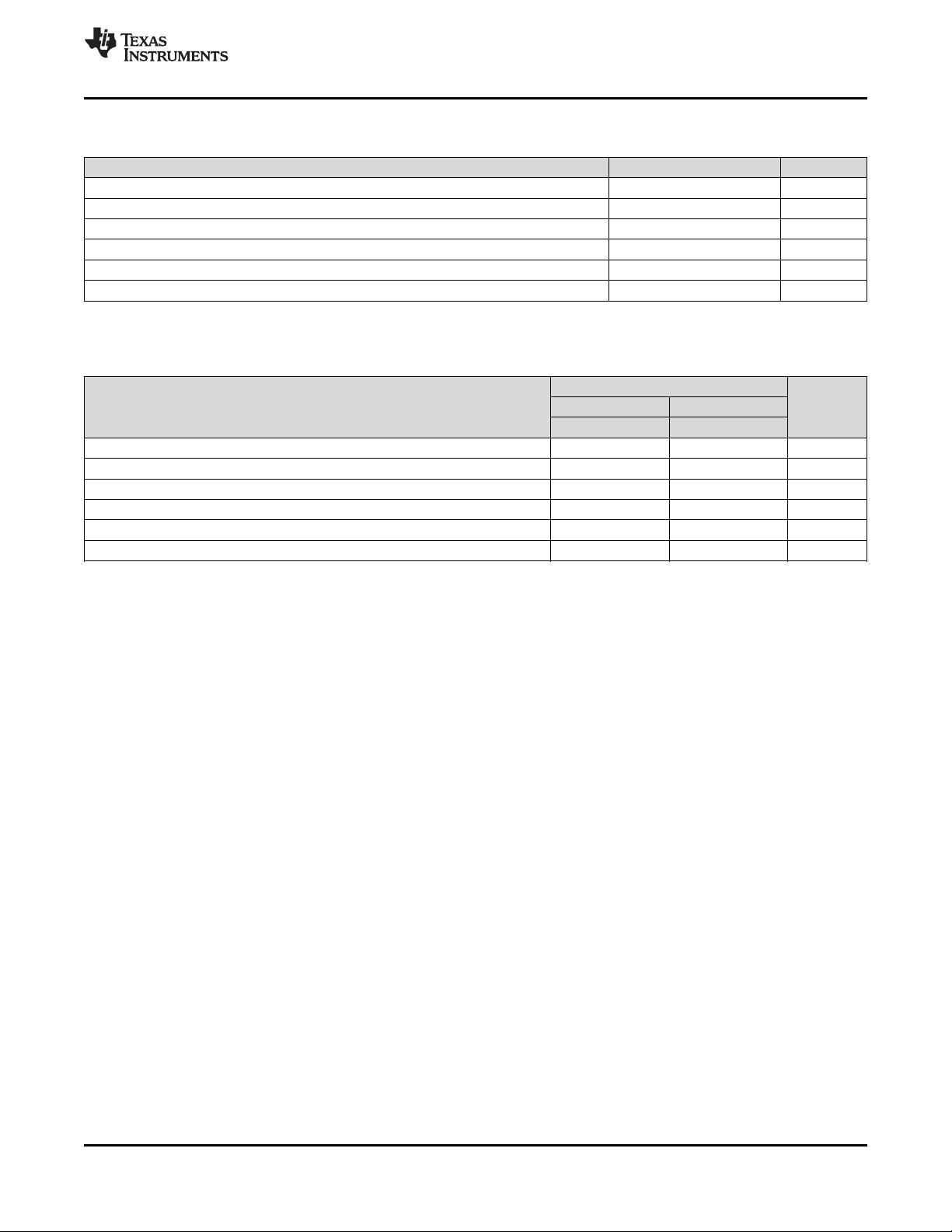

(1) Both VM pins must be connected to the same supply voltage.

(2) Power dissipation and thermal limits must be observed.

6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

MIN MAX UNIT

VM Motor power-supply voltage

(1)

8 60 V

V

IN

Digital pin voltage 0 5.5 V

f

PWM

Applied PWM signal on ENx, INx 0 250 kHz

V

GNDX

PGNDx pin voltage –500 500 mV

I

V3P3

V3P3 load current 0 10

(2)

mA

T

A

Operating ambient temperature –40 125 °C

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

report, SPRA953.

6.4 Thermal Information

THERMAL METRIC

(1)

DRV8313

UNITPWP (HTSSOP) RHH (VQFN)

28 PINS 36 PINS

R

θJA

Junction-to-ambient thermal resistance 31.6 31.1 °C/W

R

θJC(top)

Junction-to-case (top) thermal resistance 15.9 17.3 °C/W

R

θJB

Junction-to-board thermal resistance 5.6 5.6 °C/W

ψ

JT

Junction-to-top characterization parameter 0.2 0.2 °C/W

ψ

JB

Junction-to-board characterization parameter 5.5 5.6 °C/W

R

θJC(bot)

Junction-to-case (bottom) thermal resistance 1.4 1.3 °C/W

剩余38页未读,继续阅读

资源评论

邢小鹏

- 粉丝: 24

- 资源: 327

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功