没有合适的资源?快使用搜索试试~ 我知道了~

时钟抖动消除器与同步器_DSC557-0344FL1_规格书_MICROCHIP(美国微芯)时钟抖动消除器与同步器规格书.PDF

需积分: 5 0 下载量 32 浏览量

2023-11-26

15:14:59

上传

评论

收藏 1.61MB PDF 举报

温馨提示

试读

16页

时钟抖动消除器与同步器_DSC557-0344FL1_规格书_MICROCHIP(美国微芯)时钟抖动消除器与同步器规格书,中文数据手册,适合硬件电路设计开发人员使用。

资源推荐

资源详情

资源评论

2020 Microchip Technology Inc. DS20006318A-page 1

DSC557-03

Features

• Complies with PCIe Gen1/2/3/4 Common Clock

Spec

• Integrated MEMS Resonator Eliminates the Need

for External 25 MHz Crystal

• 100 MHz HCSL/LVDS/LVCMOS Options

A

vailable

• Wide Temperature Range:

- Ext. Industrial: –40°C to +105°C

- Industrial: –40°C to +85°C

- Commercial: –20°C to +70°C

• Supply Range of 2.25V to 3.6V

• Low Power Consumption

- 30% Lower than Competing Devices

• Excellent Shock & Vibration Immunity

- Qualified to MIL-STD-883

• Space Saving 14-Lead QFN Package

• Lead-Free and RoHS-Compliant

Applications

• Communications/Networking

- Ethernet

- 1G, 10GBASE-T/KR/LR/SR, and FcoE

- Routers and Switches

- Gateways, VoIP, Wireless AP’s

- Passive Optical Networks

• Storage

- SAN, NAS, SSD, JBOD

• Embedded Applications

- Industrial, Medical, and Avionics

- Security Systems and Office Automation

- Digital Signage, POS and others

• Consumer Electronics

- Smart TV, Bluray, STB

General Description

The DSC557-03 is a two output PCI express clock

generator meeting Gen1, Gen2, Gen3 and Gen 4

specifications. The clock generator uses proven silicon

MEMS technology to provide 100 MHz* differential

output clocks with excellent jitter and stability over a

wide range of supply voltages and temperatures. By

eliminating the external quartz crystal, the DSC557-03

significantly enhances reliability and accelerates

product development, while meeting stringent clock

performance criteria for a variety of communications,

storage, and networking applications.

DSC557-03 has an Output Enable / Disable feature

allowing it to disable the outputs when OE is low

. The

device is available in a space saving 14 pin QFN.

Additional output formats are also available in any

combination of LVCMOS, LVDS, and HCSL.

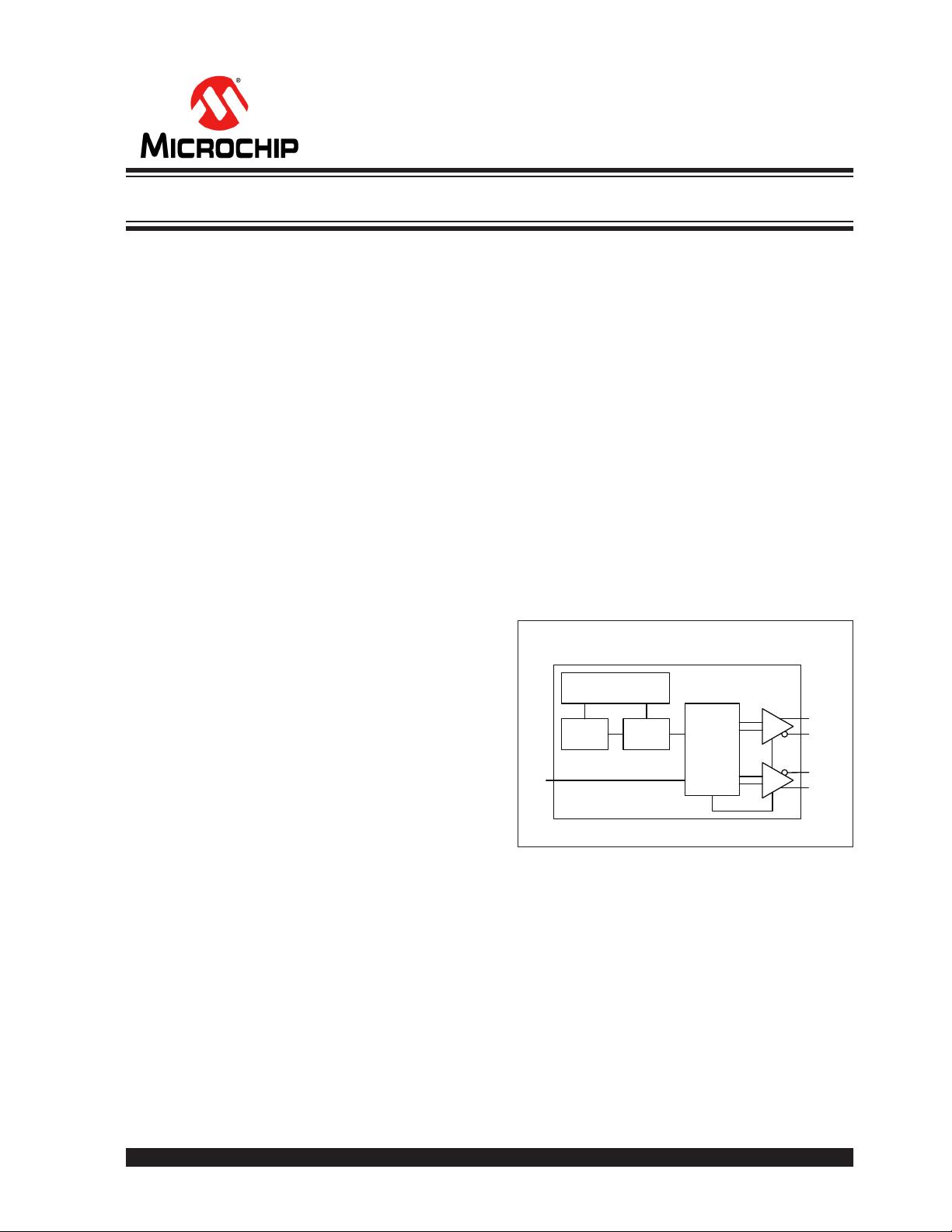

Block Diagram

Control Circuitry

MEMS PLL

Output

Control

and

Divider

CLK1+

CLK1-

CLK0+

CLK0-

OE

Two Output PCIe Gen1/2/3/4 Clock Generator

2020 Microchip Technology Inc.

•符合PCIe Gen1/2/3/4通用时钟规格•集成MEMS谐振器

消除了对外部25 MHz晶体的需求•100 MHz HCSL/LVDS

/LVCMOS选项可用•宽温度范围:

•符合PCIe Gen1/2/3/4通用时钟规格•集成MEMS谐振器

消除了对外部25 MHz晶体的需求•100 MHz HCSL/LVDS

/LVCMOS选项可用•宽温度范围:

-工业外:- 40°C至+105°C

—工业:- 40℃~ +85℃

—商用:- 20℃~ +70℃

•供电范围2.25V至3.6V•低功耗-比竞争产品

低30%•出色的抗冲击和抗振性-符合MIL-ST

D-883•节省空间的14引脚QFN封装•无铅和

符合rohs标准

•通信/网络-以太网- 1G, 10GBASE-T/KR/LR/SR

和FcoE -路由器和交换机-网关,VoIP,无线AP

-无源光网络•存储- SAN, NAS, SSD, JBOD•嵌

入式应用-工业,医疗和航空电子设备-安全系

统和办公自动化-数字标牌,POS等•消费电子

产品-智能电视,蓝光,机顶盒

一般的描述

DSC557-03是一款满足Gen1, Gen2, Gen3和Gen 4规格的双

输出PCI快速时钟发生器。时钟发生器采用成熟的硅MEMS

技术,提供100 MHz*差分输出时钟,在广泛的电源电压和

温度范围内具有出色的抖动和稳定性。通过消除外部石英

晶体,DSC557-03显着提高了可靠性,加速了产品开发,

同时满足各种通信,存储和网络应用的严格时钟性能标准

。

DSC557-03具有输出启用/禁用功能,允许它在OE低时禁

用输出。该器件采用节省空间的14引脚QFN。其他输出格

式也可用于LVCMOS, LVDS和HCSL的任何组合。

框图

控制电路

输出控

制和分

压器

双输出PCIe Gen1/2/3/4时钟发生器

翻译仅供参考,如需更准确的信息,请参考英文版

DSC557-03

DS20006318A-page 2 2020 Microchip Technology Inc.

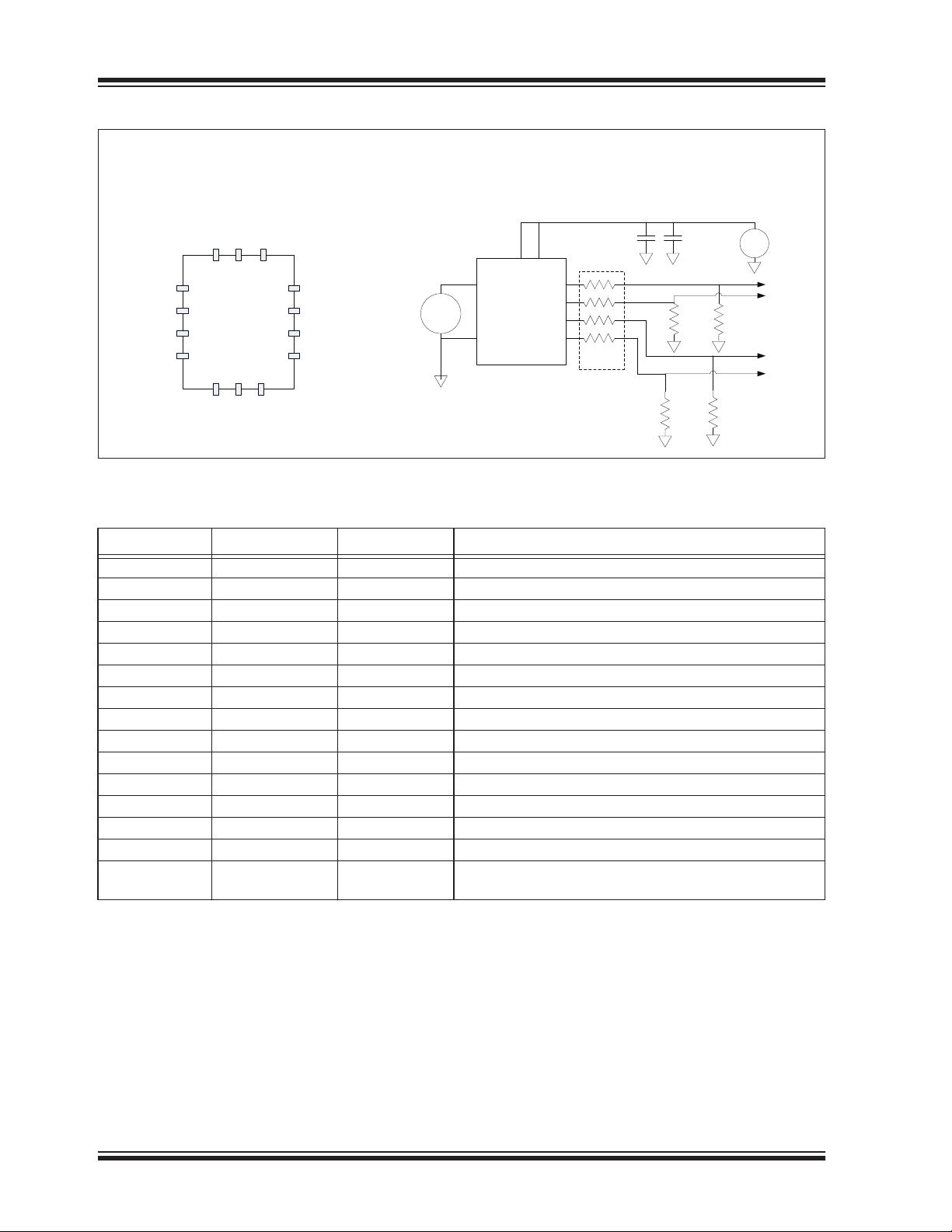

Package Type

Pin Diagram

14 Pin QFN

3.2 mm x 2.5 mm

Connection Diagram

14 Pin QFN

Two HCSL Outputs)

+

VDD

-

+

Enable

-

0.01 uF

50 : 50 :

50 : 50 :

CLK1+

CLK1-

CLK0+

CLK0-

1

2

3

4

5 6 7

8

9

10

11

121314

0.01 uF

Ropt

Ropt 22: 33 :optional

1

2

3

4

5 6 7

8

9

10

11

121314

NC

NC

NC

OE

VSS

NC

CLK1+

CLK1-

CLK0-

CLK0+

VDD0NC

NC

VDD1

TABLE 0-1: PIN DESCRIPTION (14 QFN)

Pin Number Pin Name Pin Type Description

1 OE I Output Enable; Active-high.

2 NC N/A Ground recommended or leave as a NC.

3 NC N/A Ground recommended or leave as a NC.

4 VSS Power Ground.

5 NC N/A Ground recommended or leave as a NC.

6 NC N/A Ground recommended or leave as a NC.

7 NC N/A Ground recommended or leave as a NC.

8 CLK1+ O True output of differential pair.

9 CLK1– O Complement output of differential pair.

10 CLK0– O Complement output of differential pair.

11 CLK0+ O True output of differential pair.

12 VDD1 Power Power Supply for Output 1 (CLK1+/–).

13 VDD0 Power Power Supply for Core and Output 0 (CLK0+/–).

14 NC N/A Ground recommended or leave as a NC.

ePAD ePAD N/A

Thermal pad, floating, not DC connected to substrate

ground.

2020 Microchip Technology Inc.

包类型

引脚图14引

脚QFN

3.2 mm x 2.5

接线图(14引脚QFN两

个HCSL输出)

0.01超滤0.01超滤

主题22:

表0 - 1: 引脚描述(14 qfn)

密码 销的名字 针式

允许输出;高电平。

地面建议或离开作为一个NC。

地面建议或离开作为一个NC。

地面建议或离开作为一个NC。

地面建议或离开作为一个NC。

地面建议或离开作为一个NC。

差分对的真输出。

微分对的补输出。

微分对的补输出。

差分对的真输出。

电源输出1 (CLK1+/ -)。

电源为核心和输出0 (CLK0+/ -)。

地面建议或离开作为一个NC。

热垫,浮动,不直流连接到基板接地。

2020 Microchip Technology Inc. DS20006318A-page 3

DSC557-03

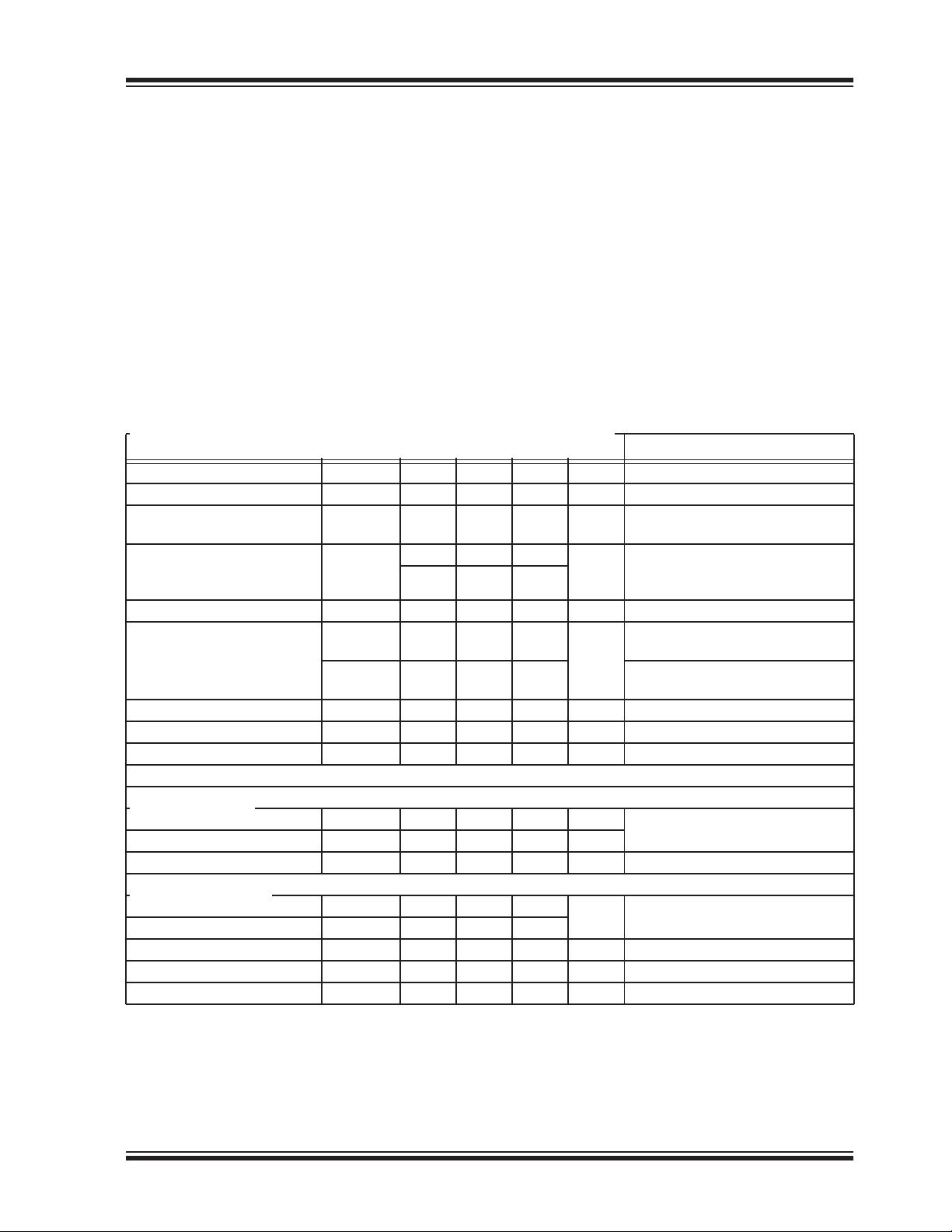

1.0 ELECTRICAL CHARACTERISTICS

Absolute Maximum Ratings †

Supply Voltage .......................................................................................................................................... –0.3V to +4.0V

Input Voltage .................................................................................................................................... –0.3V to V

DD

+ 0.3V

ESD Protection (HBM) ...............................................................................................................................................4 kV

ESD Protection (MM) ................................................................................................................................................400V

ESD Protection (CDM) ............................................................................................................................................1.5 kV

† Notice: Stresses above those listed under “Absolute Maximum Ratings” may cause permanent damage to the device.

This is a stress rating only and functional operation of the device at those or any other conditions above those indicated

in the operational sections of this specification is not intended.

Exposure to maximum rating conditions for extended

periods may affect device reliability.

ELECTRICAL CHARACTERISTICS

Electrical Characteristics: V

DD

= 3.3V; T = 25°C, unless specified otherwise.

Parameter Symbol Min. Typ. Max. Units Conditions

Supply Voltage V

DD

2.25 — 3.6 V Note 1

Supply Current I

DD

— — — — EN pin low - outputs are disabled

Supply Current (Two HCSL

Outputs),

Note 2

I

DD

— 60 — mA

EN pin high - outputs are enabled

R

L

= 50, F

O1

= F

O2

= 100 MHz

Frequency Stability f

— — ±100

ppm

Includes frequency variations due

to initial tolerance, temp. and power

supply voltage

— — ±50

Startup Time t

SU

— — 5 ms Note 3

Input Logic Levels,

V

IH

0.7 x

V

DD

— —

V

Input logic high

V

IL

— —

0.3 x

V

DD

Input logic low

Output Disable Time t

DA

— — 5 ns Note 4

Output Enable Time t

EN

— — 20 ns —

Pull-Up Resistor — — 40 — k Pull-up on OE pin

HCSL Outputs

Output Logic Levels

Output Logic High V

OH

0.725 — — V

R

L

= 50

Output Logic Low V

OL

— — 0.1 V

Peak to Peak Output Swing — — 750 — mV Single-ended

Output Transition Time

Rise Time t

R

200 — 400

ps 20% to 80%, R

L

= 50, C

L

= 2 pF

Fall Time t

F

200 — 400

Frequency f

0

— 100 — MHz Single frequency

Output Duty Cycle SYM 48 — 52 % Differential

Period Jitter Note 5 J

PER

— 2.5 — ps

RMS

F

O1

= F

O2

= 100 MHz

2020 Microchip Technology Inc.

电特性

绝对最高评级†

电源电压 ..........................................................................................................................................................................................................–0.3V to +4.0V

输入电压 ................................................................................................................................................................................... –0.3V to 【0099】 + 0.3V

ESD保护(HBM) ...................................................................................................................................................................................................................4 kV

ESD防护(MM) ...................................................................................................................................................................................................................400V

ESD保护(CDM) ...............................................................................................................................................................................................................1.5 kV

†注意:“绝对最大额定值”下列出的应力可能会对设备造成永久性损坏。

这只是一个应力额定值,不打算在高于本规范操作部分所述的那些或任何其他条件下进行设备的功能操作。长时间暴露在最

大额定条件下可能会影响设备的可靠性。

电特性

电气特性: V

DD

= 3.3V;T = 25°C,除非另有说明。参数

电源电压 注1

电源电流 EN引脚低输出被禁用

电源电流(两个HCSL输出),

注2

EN引脚高输出使能 R

L

= 50Ω, F

O1

=

F

O2

= 100mhz

频率稳定度

包括由初始公差、温度和电源电压引

起的频率变化

启动时间 注3

输入逻辑电平,

0.7倍

输入逻辑高

0.3倍

输入逻辑低

禁用输出时间 注意4

输出使能时间

上拉电阻 上拉OE引脚

HCSL输出

输出逻辑电平输出逻

辑高

输出逻辑低

峰值到峰值输出摆幅

Output Transition Time

上升时间

20% ~ 80%, R

L

= 50Ω, C

L

= 2 pF

下降时间

单一频率

输出占空比

周期抖动

F

O1

=F

O2

= 100mhz

DSC557-03

DS20006318A-page 4 2020 Microchip Technology Inc.

Jitter, Phase

(Common Clock Architecture)

Note 6

T

J

— 17 86 ps

PP

PCIe Gen 1.1

T

J

= D

J

+ 14.069 x R

J

(BER 10

-12

)

J

RMS-CCHF

— 1.46 3.1 ps

RMS

PCIe Gen 2.1, 1.5 MHz to Nyquist

J

RMS-CCLF

— 0.08 3.0 ps

RMS

PCIe Gen 2.1, 10 kHz to 1.5 MHz

J

RMS-CC

— 0.313 1.0 ps

RMS

PCIe Gen 3.0

— 0.313 0.5 ps

RMS

PCIe Gen 4.0

Integrated Phase Noise

(Data Clock Architecture)

Note 6

J

RMS-DCHF

— 2.15 — ps

RMS

PCIe Gen 2.1, 1.5 MHz to Nyquist

J

RMS-CCLF

— 0.06 — ps

RMS

PCIe Gen 2.1, 10 kHz to 1.5 MHz

J

RMS-DC

— 0.32 — ps

RMS

PCIe Gen 3.0

LVDS Output

Offset Voltage V

OS

1.125 1.25 1.40 V V

DD

= 2.5V/3.3V

V

OS

Magnitude Change V

OS

— — 50 mV —

Output High Voltage V

OH

0.9xV

DD

— — V —

Output Low Voltage V

OL

— —

0.1xV

DD

V —

Output Frequency f

OUT

— 100 — MHz —

Differential Output Voltage V

OD

275 350 475 mV

PP

—

V

OD

Magnitude Change V

OD

— — 40 mV —

LVDS Output Rise/Fall Time t

r

/t

f

— 200 — ps 20% – 80%

Output Duty Cycle ODC 48 50 52 % 20% – 80%, R

L

= 50, C

L

= 2 pF

Period Jitter, Peak to Peak J

PTP

— 2.5 — ps f

OUT

= 100 MHz, Standard Drive

Integrated Phase Noise J

PH

— 0.28 —

ps

RMS

200 kHz to 20 MHz @ 100 MHz,

T

A

= +105°C

— 0.4 — 100 kHz to 80 MHz @ 100 MHz

— 1.7 2.0 12 kHz to 10 MHz @ 100 MHz

LVCMOS Output

Output High Voltage V

OH

0.8xV

DD

— — V ±10 mA drive current

Output Low Voltage V

OL

— —

0.2xV

DD

V ±10 mA drive current

Output Frequency f

OUT

— 100 — MHz —

Output Rise/Fall Time t

r

/t

f

— 1.2 — ns 20% – 80%, C

L

= 15 pF

Output Duty Cycle ODC 48 50 52 % f

OUT

= 100 MHz, Standard Drive

Period Jitter J

PTP

— 3 — ps

RMS

f

OUT

= 100 MHz, Standard Drive

Integrated Phase Noise J

PH

— 0.3 —

ps

RMS

200 kHz to 20 MHz @ 100 MHz

— 0.38 — 100 kHz to 20 MHz @ 100 MHz

— 1.7 2.0 12 kHz to 20 MHz @ 100 MHz

Note 1: V

DD

pin should be filtered with a 0.1 F capacitor.

2: Output is enabled if OE pin is floated or not connected.

3: t

su

is time to 100 PPM stable output frequency after V

DD

is applied and outputs are enabled.

4: Output Waveform and Connection Diagram define the parameters.

5: Period Jitter includes crosstalk from adjacent output.

6: Jitter limits established by Gen 1.1, Gen 2.1, Gen 3.0 and Gen 4.0 PCIe standards.

ELECTRICAL CHARACTERISTICS (CONTINUED)

Electrical Characteristics: V

DD

= 3.3V; T = 25°C, unless specified otherwise.

Parameter Symbol Min. Typ. Max. Units Conditions

2020 Microchip Technology Inc.

(通用时钟架构

PCIe Gen 1.1

T

J

=D

J

+ 14.069 × R

J

(BER10

-12

))

PCIe Gen 2.1, 1.5 MHz到奈奎斯特

PCIe Gen 2.1, 10khz至1.5 MHz

PCIe Gen 3.0

PCIe Gen 4.0

集成相位噪声(数据时钟架

构

PCIe Gen 2.1, 1.5 MHz到奈奎斯特

PCIe Gen 2.1, 10khz至1.5 MHz

PCIe Gen 3.0

LVDS输出

补偿电压

V

OS

量级变化

输出高压

输出低电压

输出频率

差分输出电压

V

OD

量级变化

LVDS输出上升/下降时间

输出占空比

20% - 80%, R

L

= 50Ω, C

L

= 2 pF

周期抖动,峰值到峰值

f

OUT

= 100mhz,标准驱动器

集成相位噪声

200 kHz至20 MHz @ 100 MHz,

T

A

= +105°C

100 kHz至80 MHz @ 100 MHz

12 kHz至10 MHz @ 100 MHz

LVCMOS输出

输出高压 ±10ma驱动电流

输出低电压 ±10ma驱动电流

输出频率

输出上升/下降时间

20% - 80%, C

L

= 15pf

输出占空比

f

OUT

= 100mhz,标准驱动器

周期抖动

f

OUT

= 100mhz,标准驱动器

集成相位噪声

200 kHz至20 MHz @ 100 MHz

100 kHz至20 MHz @ 100 MHz

12 kHz至20 MHz @ 100 MHz

注1:

V

DD

引脚应用0.1 μF的电容滤波。

如果OE引脚浮动或未连接,则启用输出。

在应用 t

su

并使能输出后, V

DD

为达到100ppm稳定输出频率的时间。

输出波形和连接图定义参数。

周期抖动包括相邻输出的串扰。

Gen 1.1, Gen 2.1, Gen 3.0和Gen 4.0 PCIe标准建立的抖动限制。

电气特性(续)

电气特性: V

DD

= 3.3V;T = 25°C,除非另有说明。参数

剩余15页未读,继续阅读

资源评论

沐风听雨_A

- 粉丝: 300

- 资源: 183

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 蓝桥杯2024年第十五届省赛真题-前缀总分

- com.qihoo.appstore_300101305-1.apk

- tensorflow-gpu-2.7.1-cp37-cp37m-manylinux2010-x86-64.whl

- tensorflow-2.7.2-cp37-cp37m-manylinux2010-x86-64.whl

- tensorflow-2.7.1-cp39-cp39-manylinux2010-x86-64.whl

- 蓝桥杯2024年第十五届省赛真题-传送阵

- com.qihoo.appstore_300101305.apk

- linux之线程同步一.doc

- keil5配色方案10种

- python烟花代码.doc

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功