没有合适的资源?快使用搜索试试~ 我知道了~

时钟缓冲器,驱动器_ADCLK946BCPZ-REEL7_规格书_ADI(亚德诺).PDF

需积分: 5 0 下载量 155 浏览量

2023-11-26

15:13:15

上传

评论

收藏 736KB PDF 举报

温馨提示

试读

12页

时钟缓冲器,驱动器_ADCLK946BCPZ-REEL7_规格书_ADI(亚德诺)_LINEAR(凌特)时钟缓冲器,驱动器规格书,中文数据手册,适合硬件电路设计开发人员使用。

资源推荐

资源详情

资源评论

Six LVPECL Outputs,

SiGe Clock Fanout Buffer

Data Sheet

ADCLK946

Rev. B Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 ©2009–2017 Analog Devices, Inc. All rights reserved.

Technical Support www.analog.com

FEATURES

4.8 GHz operating frequency

75 fs rms broadband random jitter

On-chip input terminations

3.3 V power supply

APPLICATIONS

Low jitter clock distribution

Clock and data signal restoration

Level translation

Wireless communications

Wired communications

Medical and industrial imaging

ATE and high performance instrumentation

GENERAL DESCRIPTION

The ADCLK946 is an ultrafast clock fanout buffer fabricated on

the Analog Devices, Inc., proprietary XFCB3 silicon germanium

(SiGe) bipolar process. This device is designed for high speed

applications requiring low jitter.

The device has a differential input equipped with center-tapped,

differential, 100 Ω on-chip termination resistors. The input accepts

dc-coupled LVPECL, CML, 3.3 V CMOS (single ended), and

ac-coupled 1.8 V CMOS, LVDS, and LVPECL inputs. A V

REF

pin

is available for biasing ac-coupled inputs.

The ADCLK946 features six full-swing emitter-coupled logic

(ECL) output drivers. For LVPECL (positive ECL) operation,

bias V

CC

to the positive supply and V

EE

to ground. For ECL

operation, bias V

CC

to ground and V

EE

to the negative supply.

The ECL output stages are designed to directly drive 800 mV

each side into 50 Ω terminated to V

CC

− 2 V for a total differen-

tial output swing of 1.6 V.

The ADCLK946 is available in a 24-lead LFCSP and is specified

for operation over the standard industrial temperature range of

−40°C to +85°C.

FUNCTIONAL BLOCK DIAGRAM

Q0

Q0

Q1

Q1

Q2

Q2

Q3

Q3

Q4

Q4

Q5

Q5

LVPECL

CLK

V

T

V

REF

CLK

ADCLK946

REFERENCE

08053-001

F

igure 1.

六个LVPECL输出,

SiGe时钟扇出缓冲器

数据表

文档反馈

我们相信adi公司提供的信息是准确可靠的。但是,Analog Devices对其使用不承担任何责

任,也不对因其使用而可能导致的任何侵犯第三方专利或其他权利的行为承担任何责任。

规格如有更改,恕不另行通知。adi公司的任何专利或专利权均未隐含或以其他方式授予许

可。商标和注册商标是其各自所有者的财产。

One Technology Way,邮编:02062-9106,诺伍德,美国,电话:781.329.47

00

©2009-2017 Analog Devices, Inc。版权所有。

技术支持

4.8 GHz工作频率

片上输入端3.3 V电源

应用程序低抖动时钟分

布

时钟和数据信号恢复电平转换无线通信有线通

信医疗和工业成像ATE和高性能仪器仪表

一般的描述

ADCLK946是一款超快时钟扇出缓冲器,采用Analog Devices

公司专有的XFCB3硅锗(SiGe)双极工艺制造。该器件专为需要

低抖动的高速应用而设计。

该装置具有配备中心抽头、差动、100 Ω的差动输入

片上终端电阻。输入接受

直流耦合LVPECL、CML、3.3 V CMOS(单端)和交流耦合1.8 V

CMOS、LVDS和LVPECL输入。 V

REF

引脚可用于偏置交流耦合

输入。

ADCLK946具有六个全摆幅发射器耦合逻辑(ECL)输出驱动

器。对于LVPECL(正ECL)操作,偏置 V

CC

到正电源,偏置 V

EE

到地。对于ECL操作,偏置 V

CC

到地,偏置 V

EE

到负电源。

ECL输出级设计为直接驱动800 mV每侧50 Ω

端接至 V

CC

2 V的总差值

初压输出摆幅1.6 V。

ADCLK946提供24引脚LFCSP,指定在- 40°C至+85°C的标准

工业温度范围内工作。

功能框图

Q

0

Q

0

处

Q

1

Q

1

第

二

季

第

二

季

第

三

季

第

三

季

第

四

季

度

第

四

季

度

Q

5

Q

5

图1所示。

翻译仅供参考,如需更准确的信息,请参考英文版

ADCLK946 Data Sheet

Rev. B | Page 2 of 12

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications ....................................................................................... 1

General Description ......................................................................... 1

Functional Block Diagram .............................................................. 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

Electrical Characteristics ............................................................. 3

Absolute Maximum Ratings ............................................................ 5

Determining Junction Temperature .......................................... 5

ESD Caution .................................................................................. 5

Thermal Performance ...................................................................5

Pin Configuration and Function Descriptions ..............................6

Typical Performance Characteristics ..............................................7

Functional Description .....................................................................9

Clock Inputs ...................................................................................9

Clock Outputs ................................................................................9

PCB Layout Considerations ...................................................... 10

Input Termination Options ....................................................... 11

Outline Dimensions ....................................................................... 12

Ordering Guide .......................................................................... 12

REVISION HISTORY

8/2017—Rev. A to Rev. B

Changes to Figure 2 .......................................................................... 6

Updated Outline Dimensions ....................................................... 12

Changes to Ordering Guide .......................................................... 12

5/2010—Re

v. 0 to Rev. A

Changes to Table 1, DC Output Characteristics ........................... 3

4/2009—R

evision 0: Initial Version

数据表

Rev. B |第2页,共12页

目录表

一般的描述 ............................................................................................... 1

功能框图 .................................................................................................... 1

修订历史 .................................................................................................... 2

电特性 .................................................................................................... 3

绝对最大评级 .......................................................................................... 5

确定结温 ................................................................................................ 5

ESD谨慎 ................................................................................................. 5

热力性能 .................................................................................................5

引脚配置和功能说明 .............................................................................6

典型性能特点 ............................................................................................7

功能描述 .....................................................................................................9

时钟输入 .................................................................................................9

时钟输出 .................................................................................................9

PCB布局注意事项 ........................................................................... 10

输入终止选项 .................................................................................... 11

轮廓尺寸 .................................................................................................. 12

订购指南 ............................................................................................. 12

修订记录2017年8月

- 2017年5月A到Rev.

B

对图2的更改 ............................................................................................. 6

更新的外形尺寸 ................................................................................... 12

订购指南的更改 ................................................................................... 12

5/2010-Rev。0到Rev. A

表1直流输出特性的变化 ..................................................................... 3

4/2009-Revision 0:初版

Data Sheet ADCLK946

Rev. B | Page 3 of 12

SPECIFICATIONS

ELECTRICAL CHARACTERISTICS

Typical (typ) values are given for V

CC

− V

EE

= 3.3 V and T

A

= 25°C, unless otherwise noted. Minimum (min) and maximum (max) values

are given over the full V

CC

− V

EE

= 3.3 V ± 10% and T

A

= −40°C to +85°C variation, unless otherwise noted.

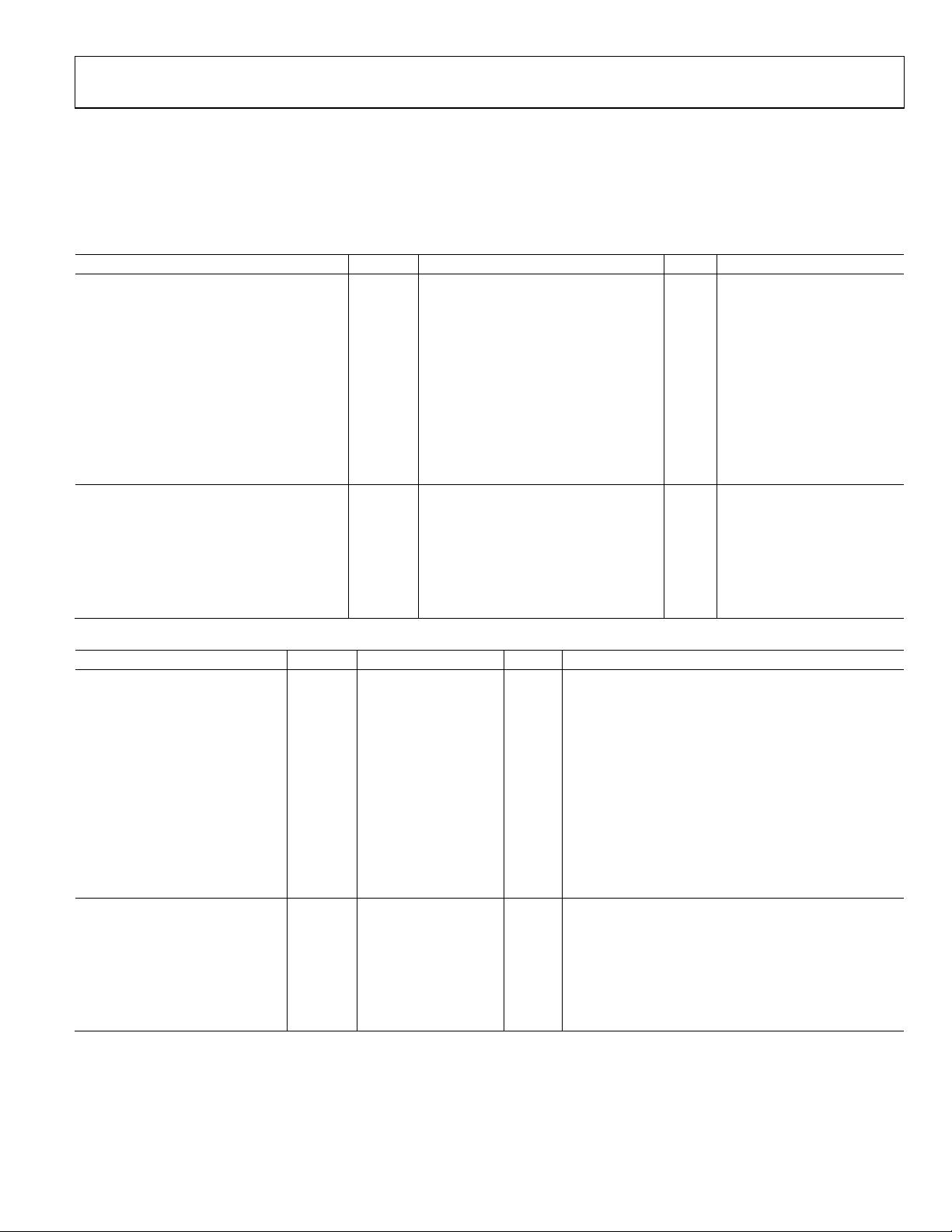

Table 1. Clock Inputs and Outputs

Parameter Symbol Min Typ Max Unit Test Conditions/Comments

DC INPUT CHARACTERISTICS

Input Voltage High Level

V

IH

V

EE

+ 1.6

V

CC

V

Input Voltage Low Level V

IL

V

EE

V

CC

− 0.2 V

Input Differential Range V

ID

0.4 3.4 V p-p ±1.7 V between input pins

Input Capacitance C

IN

0.4 pF

Input Resistance

Single-Ended Mode 50 Ω

Differential Mode 100 Ω

Common Mode

50

kΩ

Open V

T

Input Bias Current 20 µA

Hysteresis 10 mV

DC OUTPUT CHARACTERISTICS

Output Voltage High Level V

OH

V

CC

− 1.26 V

CC

− 0.76 V 50 Ω to (V

CC

− 2.0 V)

Output Voltage Low Level V

OL

V

CC

− 1.99 V

CC

− 1.54 V 50 Ω to (V

CC

− 2.0 V)

Output Voltage, Single-Ended V

O

610 960 mV V

OH

− V

OL

, output static

Reference Voltage V

REF

Output Voltage (V

CC

+ 1)/2 V −500 µA to +500 µA

Output Resistance 235 Ω

Table 2. Timing Characteristics

Parameter Symbol Min Typ Max Unit Test Conditions/Comments

AC PERFORMANCE

Maximum Output Frequency 4.5 4.8 GHz See Figure 4 for differential output voltage vs.

frequency, >0.8 V differential output swing

Output Rise/Fall Time t

R,

t

F

40 75 90 ps 20% to 80% measured differentially

Propagation Delay t

PD

150 185 220 ps V

ICM

= 2 V, V

ID

= 1.6 V p-p

Temperature Coefficient 50 fs/°C

Output-to-Output Skew 9 28 ps

Part-to-Part Skew

1

45 ps V

ID

= 1.6 V p-p

Additive Time Jitter

Integrated Random Jitter 28 fs rms BW = 12 kHz − 20 MHz, CLK = 1 GHz

Broadband Random Jitter

2

75 fs rms V

ID

= 1.6 V p-p, 8 V/ns, V

ICM

= 2 V

Crosstalk-Induced Jitter

3

90 fs rms

CLOCK OUTPUT PHASE NOISE

Absolute Phase Noise

Input slew rate > 1 V/ns (see Figure 11 for more details)

f

IN

= 1 GHz −119 dBc/Hz @ 100 Hz offset

−134 dBc/Hz @ 1 kHz offset

−145 dBc/Hz @ 10 kHz offset

−150 dBc/Hz @ 100 kHz offset

−150 dBc/Hz >1 MHz offset

1

The output skew is the difference between any two similar delay paths while operating at the same voltage and temperature.

2

Measured at the rising edge of the clock signal; calculated using the SNR of the ADC method.

3

The amount of added jitter measured at the output while two related, asynchronous, differential frequencies are applied to the inputs.

数据表

Rev. B b|第3页,共12页

电特性

除非另有说明,在 V

CC

~V

EE

= 3.3 V和 T

A

= 25°C时给出典型(类型)值。除非另有说明,最小(min)和最大(max)值在整个 V

CC

V

EE

= 3.3 V±1

0%和T

A

=40°C至+85°C变化范围内给出。

表1。时钟输入和输出

测试条件/评论

直流输入特性输入电压高电

平

输入电压低

输入差动范围 输入引脚之间±1.7 V

输入电容

输入电阻单端模式

差模

共模

输入偏置电流

直流输出特性输出电压高电平

至(V

CC

2.0 V)

输出电压低电平

到(V

CC

2.0 V)

输出电压,单端

V

OH

V

OL

,输出静态

参考电压

输出电压 500µA ~ +500µA

输出电阻

表2。时间特征

测试条件/评论

交流性能最大输出频率

差分输出电压与频率的关系见图4,>0.8 V差

分输出摆幅

输出上升/下降时间 20%到80%的测量结果不同

传播延迟

V

ICM

= 2v, V

ID

= 1.6 V p-p

温度系数

Output-to-Output斜

V

ID

= 1.6 V p-p

加性时间抖动集成随机抖

动

fs rms BW = 12khz20mhz, CLK = 1ghz

Jitter

2

fs rms

V

ID

= 1.6 V p-p, 8 V/ns, V

ICM

= 2 V

fs rms

时钟输出相位噪声绝对相位

噪声

输入压摆率> 1 V/ns(参见图11了解更多细节)

f

IN

= 1 GHz

@ 100 Hz偏移

@ 1 kHz偏移

@ 10 kHz偏移

@ 100 kHz偏移

> 1mhz偏移

输出偏差是在相同电压和温度下工作时任意两个相似延迟路径之间的差值。

测量时钟信号的上升沿;采用ADC方法计算信噪比。

当两个相关的异步差分频率应用于输入时,在输出端测量到的增加抖动量。

剩余11页未读,继续阅读

资源评论

沐风听雨_A

- 粉丝: 300

- 资源: 183

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功