《数字逻辑与数字系统》实验报告

天津大学本科生实验报告专用纸

学院 智能与计算学部 年级 2020 班级 姓名

学号 课程名称 数字逻辑与数字系统 实验日期 5.16 成绩

同组实验者

实验项目名称 算术逻辑单元(ALU)的设计与实现

一. 实验目的

1. 掌握全加器和行波进位加法器的结构;

2. 熟悉加减法运算及溢出的判断方法;

3. 掌握算术逻辑单元(ALU)的结构;

4. 熟练使用 SystemVerilog HDL 的行为建模和结构化建模方法对 ALU 进行

描述实现;

5. 为“单周期 MIPS 处理器的设计与实现”奠定基础。

二. 实验内容

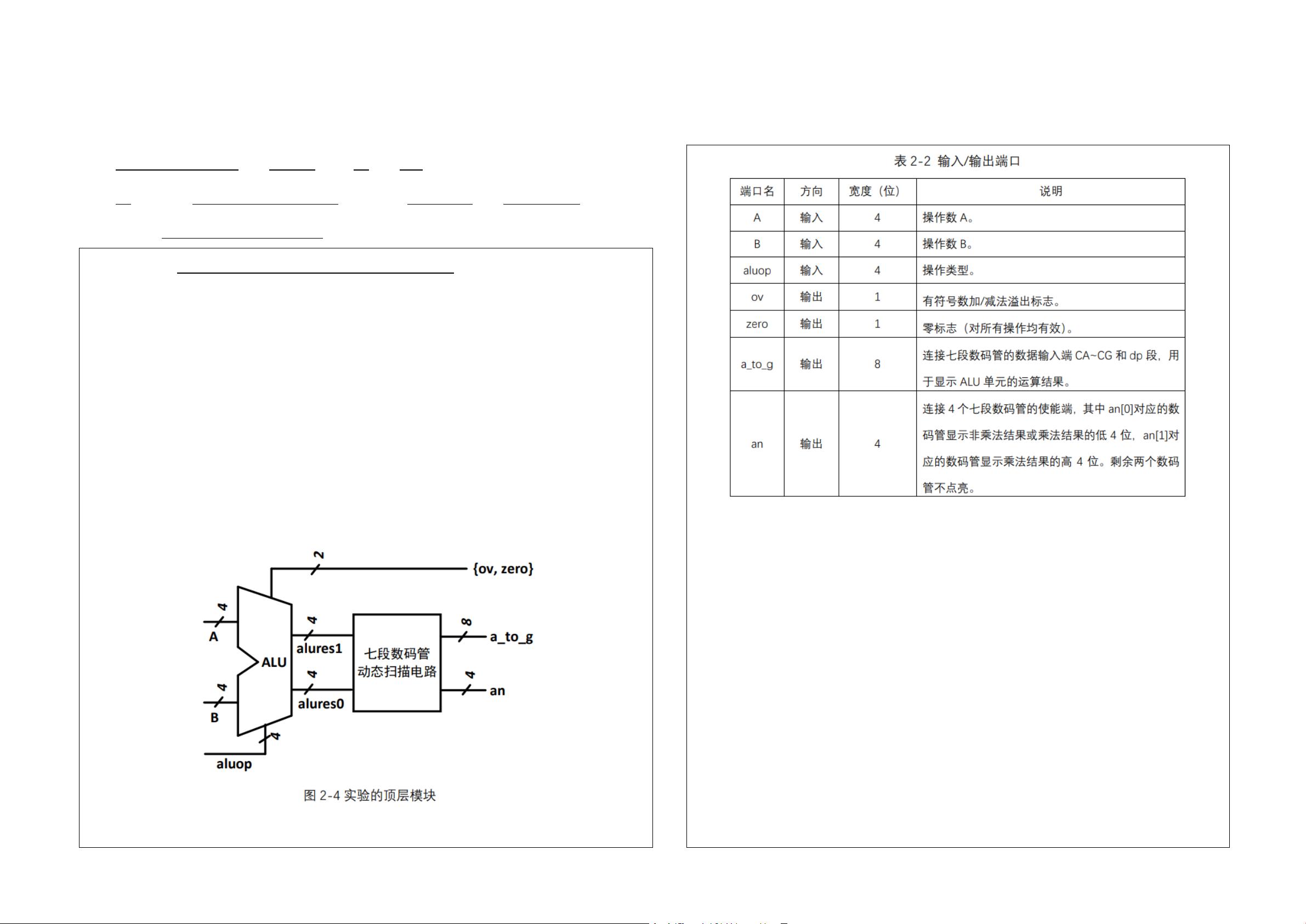

基于 SystemVerilog HDL 设计并实现一个 4 位 ALU 单元。整个工程的顶层模块如图 2-4 所

示,输入/输出端口如表 2-2 所示。注意,顶层模块由两个子模块组成,其中,一个是 ALU 单元,

另一个是 7 段数码管动态显示扫描单元。本次实验只需要实现 ALU 单元即可,动态显示扫描单

元在工程中直接提供。

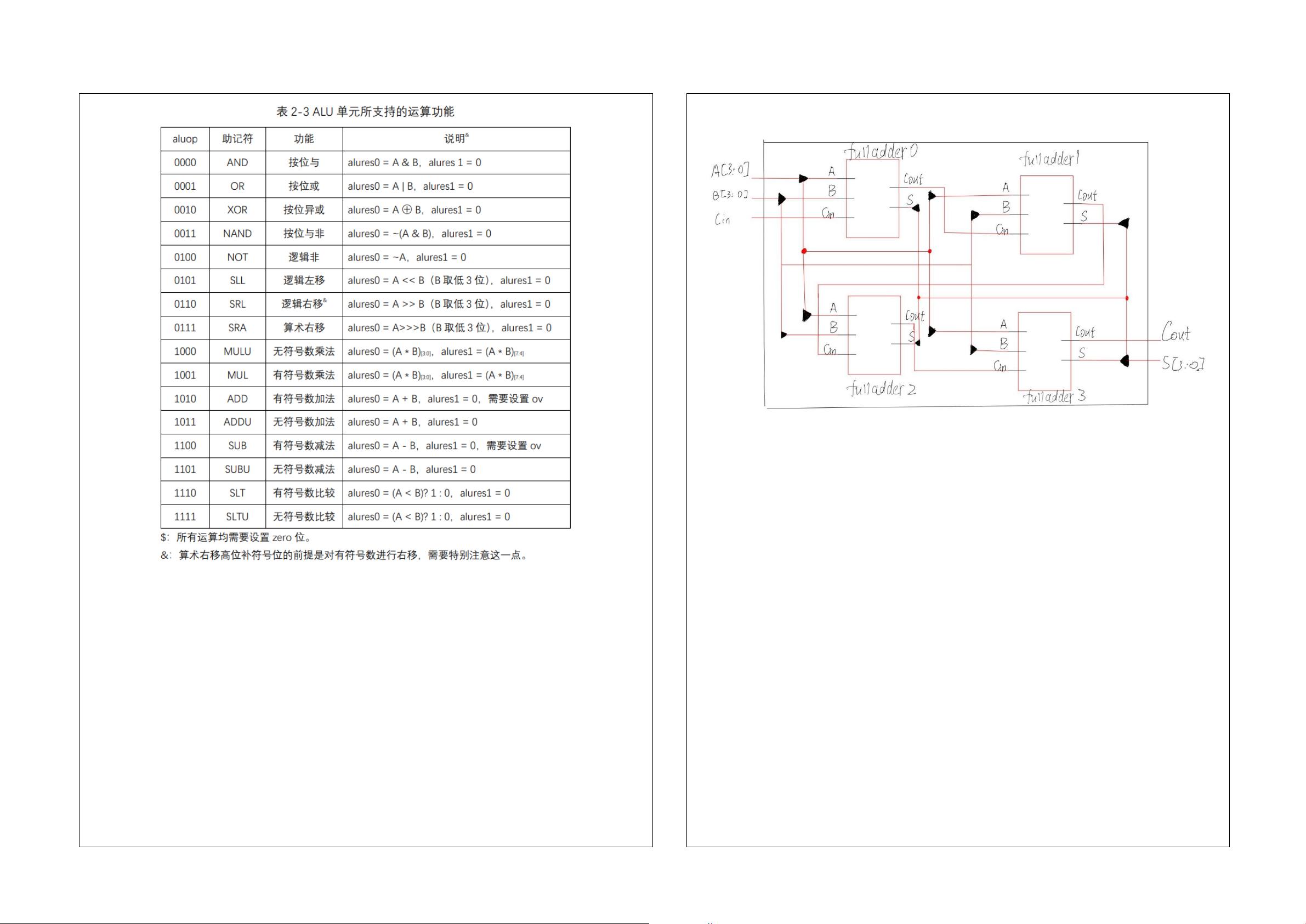

ALU 单元所支持的运算功能如表 2-3 所示。