CPU 实验报告

特点:

1. 哈佛存储器结构,大端格式;

2. 类 MIPS 精简指令集,支持子程序调用和软中断;

3. 实现了乘除法;

4. 五级流水线,工作频率可达 80MHz(每个时钟周期一条指令,不计流水线冲突)。

一、小组成员

于晃 无 64 负责部分数据通路以及调试

李龙毅 无 64 负责 ALU

闫轲 无 610 负责控制器、部分数据通路、汇编器以及调试

二、模块原理介绍

指令集介绍

这个指令集是由于晃和闫轲共同协定的,其中于晃提出了初始版本,闫轲根据实际情况

进行了改进。

指令集共包括 50 条指令,具体分配如下:

有符号四则运算

R 型指令 无符号四则运算

(ALU 运算) 逻辑运算

移位运算

Load/Store 指令

立即数装入高半字 LHI

I 型指令 比较指令 CMP

带立即数的 ALU 运算

各种分支指令 Bxx

J 型指令 子程序调用 CALL

软件中断 SYSINT

详细的表格控制码、控制信号分配可见压缩包中的 NewInstructions.xls。下面对各指令的设

计初衷进行介绍。

R 型指令

与老师给的 Z0 指令集不同,这个指令集将加减乘除四则运算都包括进去了,

会比只有加减的指令集更易用一些,算是部分实现了 FPU 的指令吧。不过缺点是

乘除法的延时会比加减法大一些。

无符号加减其实与有符号加减并无本质不同,X86 指令集没有无符号加减,

MIPS 指令集无符号加减与有符号的唯一区别是无符号加减不置 OV 标志寄存器。

这里参考 MIPS 指令集的做法,同时也照顾了指令集的“整齐性”。

逻辑运算中 NOT 指令其实可以用 XOR 指令来实现,这里单独用了一条指令

也是为了易用性和“整齐性”,但 NOT 指令只有两个操作数。

R 型指令的 Op 字段都为 0,具体功能由 Funct 字段指定。实现的功能为将

Rx 中内容和 Ry 中内容进行操作后存入 Rz。

Op

Rx

Ry

Rz

(useless)

Funct

6 位 5 位 5 位 5 位 5 位 6 位

I 型指令

根据老师要求,Load/Store 类指令按长度分为字节、(低)半字和字三种,

Load 类指令(内存寄存器)还分为有符号和无符号两种(Store 类指令不需区分),

因此共有 6 个 Load 指令,3 个 Store 指令。其格式为 L/S Rx, Offset, Ry,load 类指

令是将 Rx 中地址偏移 Offset 后指向的内存存入 Ry;store 类指令是将 Ry 存入 Rx

中地址偏移 Offset 后指向的内存。

LHI Ry, Imm16 指令实现了立即数装入高半字功能,与 ORI $0, Imm16,Ry 指

令接合即可实现装入 32 位立即数的功能。

CMP Rx, Ry 实现了比较两个寄存器值(本质为有符号减)并置标志寄存器的

功能,为下面的条件分支指令做准备。

带立即数的 ALU 运算与寄存器 ALU 运算的唯一区别是:前者不存在 NOT 指

令。

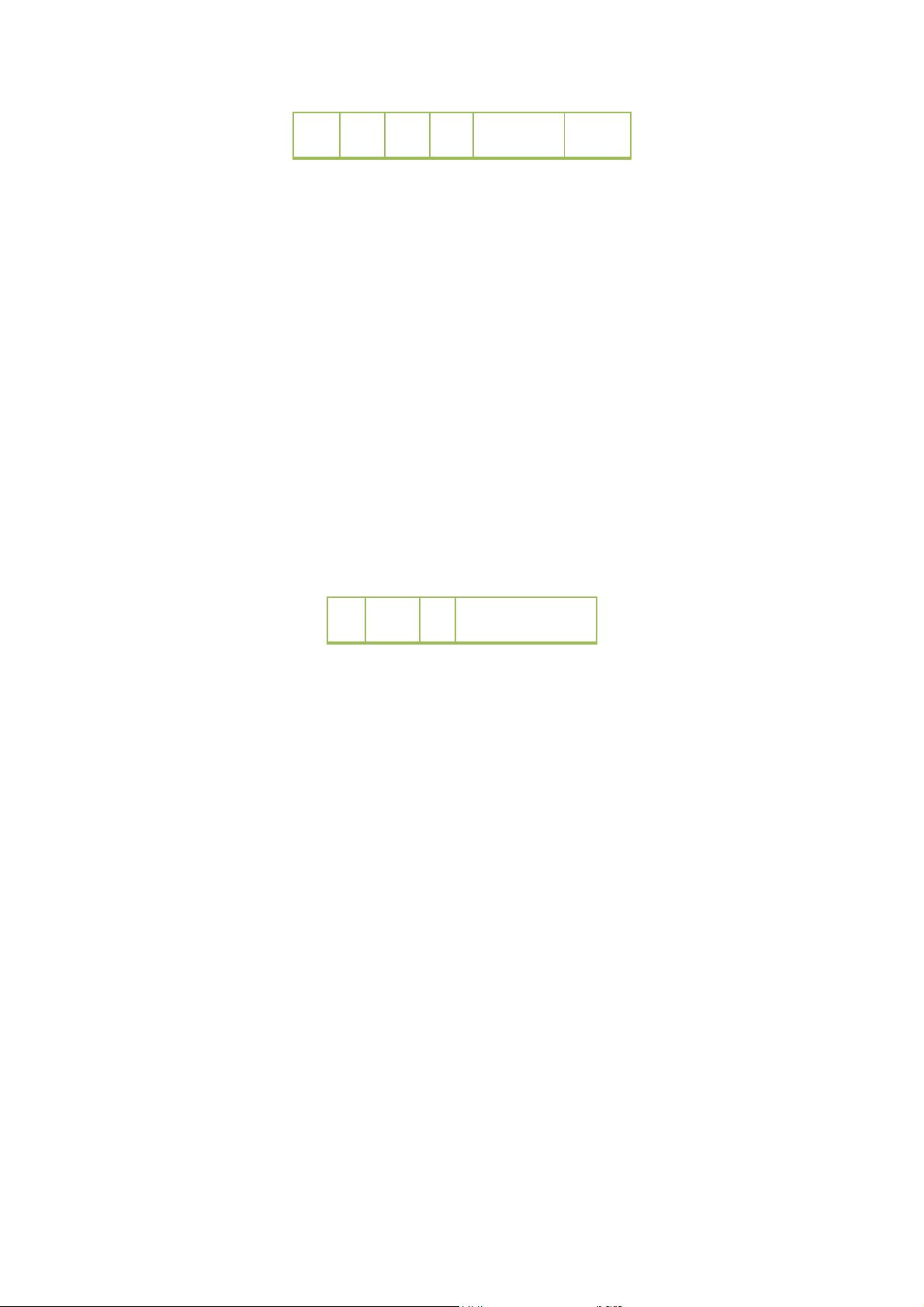

Op

Rx/0

Ry

Imm16/Offset/0

6 位 5 位 5 位 16 位

J 型指令

条件分支指令(包括相等跳转 BO,不等跳转 BNO,有符号大于跳转 BGT,

有符号小于等于跳转 BLET,BGTU,BLETU)本来计划的是设为 I 型指令,即对 Rx

和 Ry 进行比较后,根据标志寄存器 flag 条件跳转到 Addr,但这样一来一条指令要

用两次 ALU,一次用来比较,一次用来计算跳转地址,造成了延时;另外很多情

况下前面的 ALU 指令已经更改了 flag,不需要再进行比较了。因此将条件分支指令

设为 J 型指令,这样一来也扩大了跳转范围。老师给的提示中有符号跳转分为大

于跳转和小于跳转,细思之觉此分法不妥,因为这样大于等于跳转就无法表示

了。

子程序调用指令CALL与跳转指令很相似,都是跳转,但 CALL 需要保存当前

PC 值以便返回。这里参考 MIPS,在跳转的同时将 PC 存入寄存器$ra。为此 CPU 中

设置了专用通路。

与 CALL 类似,系统中断指令 SYSINT 也需要存 PC 并跳转,不同的是这里假

设在程序内存中有一个从 0 号内存开始的、每个表项为 4 个字节的中断向量表,因

此 SYSINT 的参数并不是地址偏移量,而是编号。实际上跳转到参数左移 2 位(乘 4)

的绝对地址。

- 1

- 2

- 3

- 4

- 5

- 6

前往页