EDA各种程序

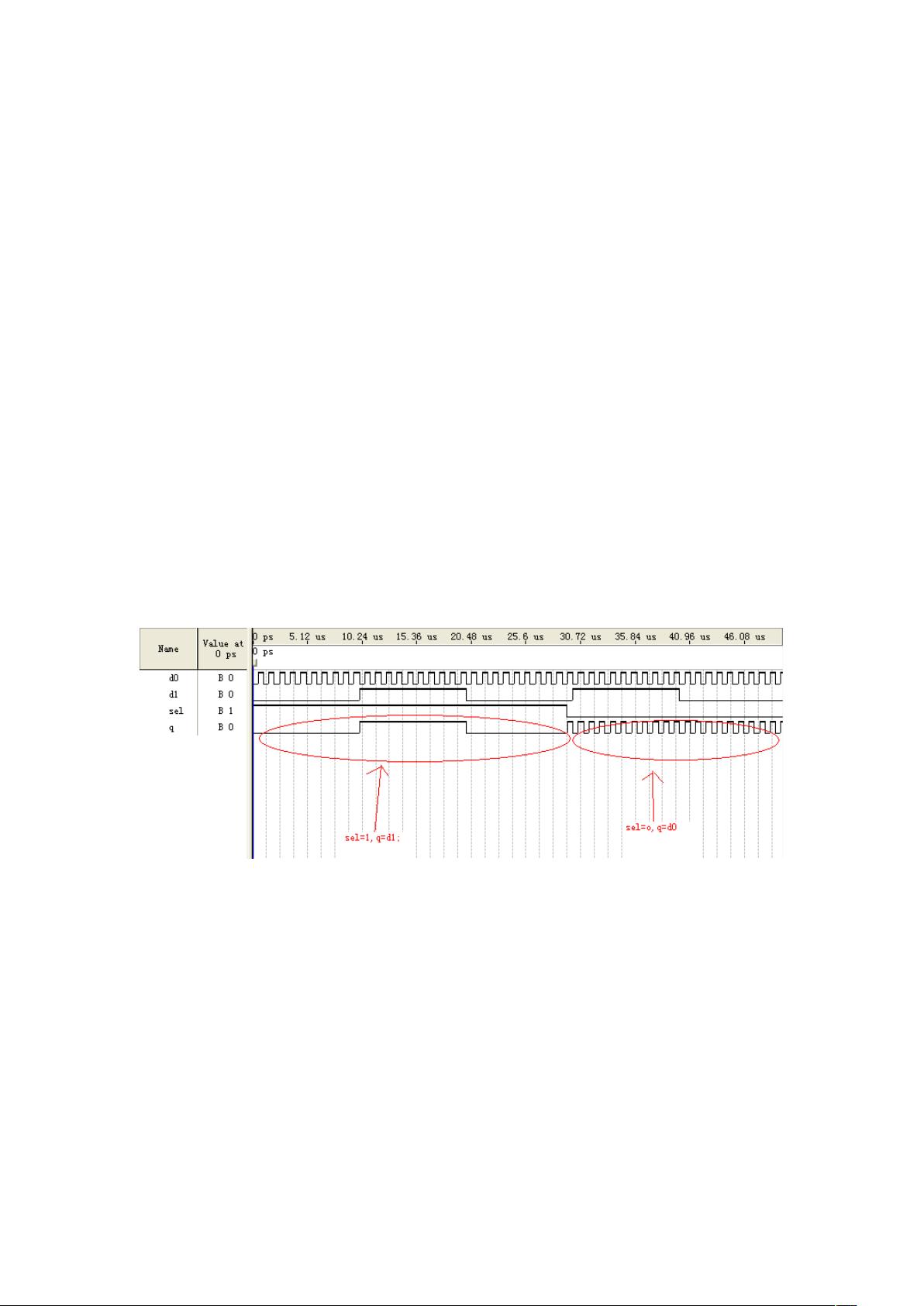

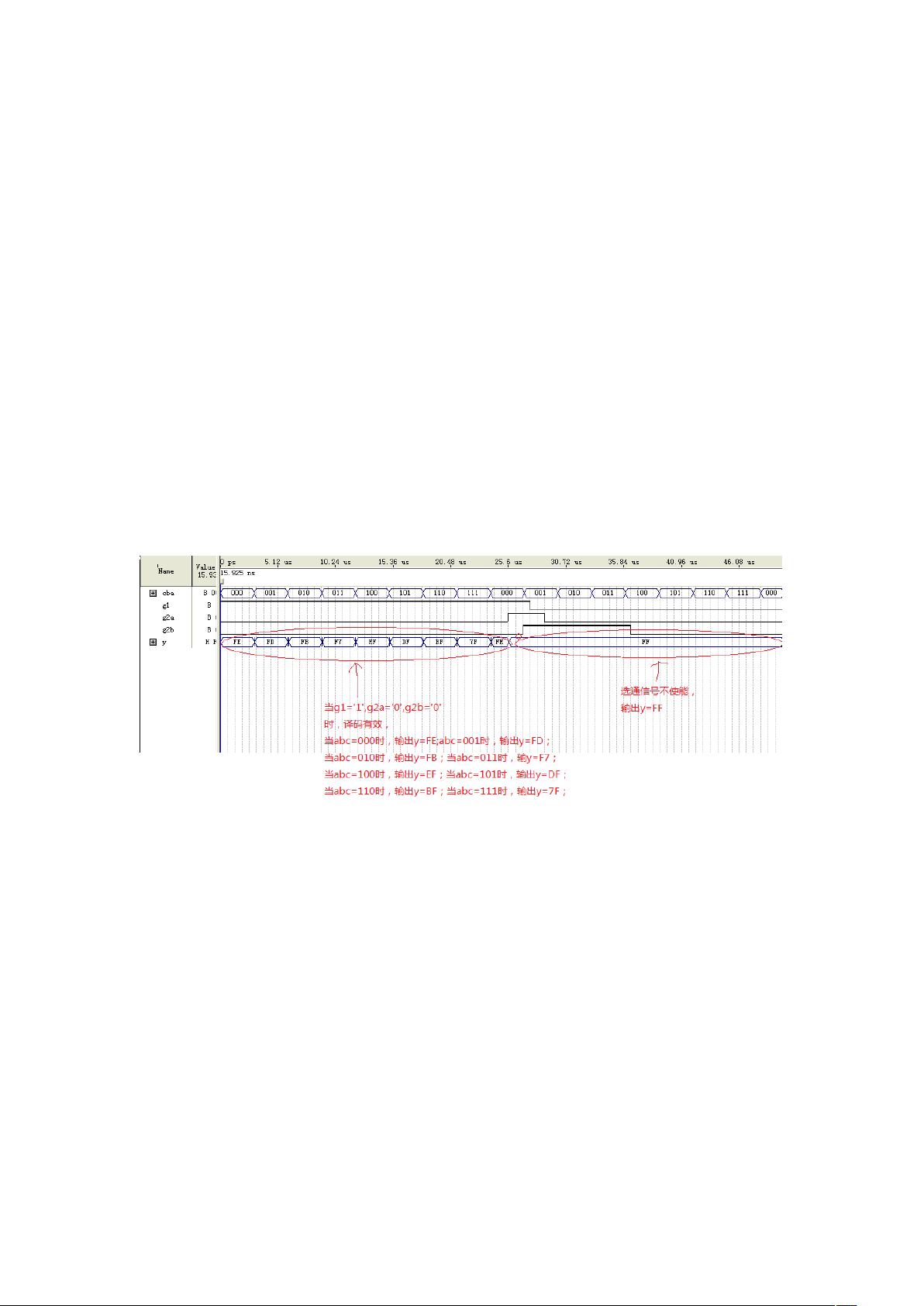

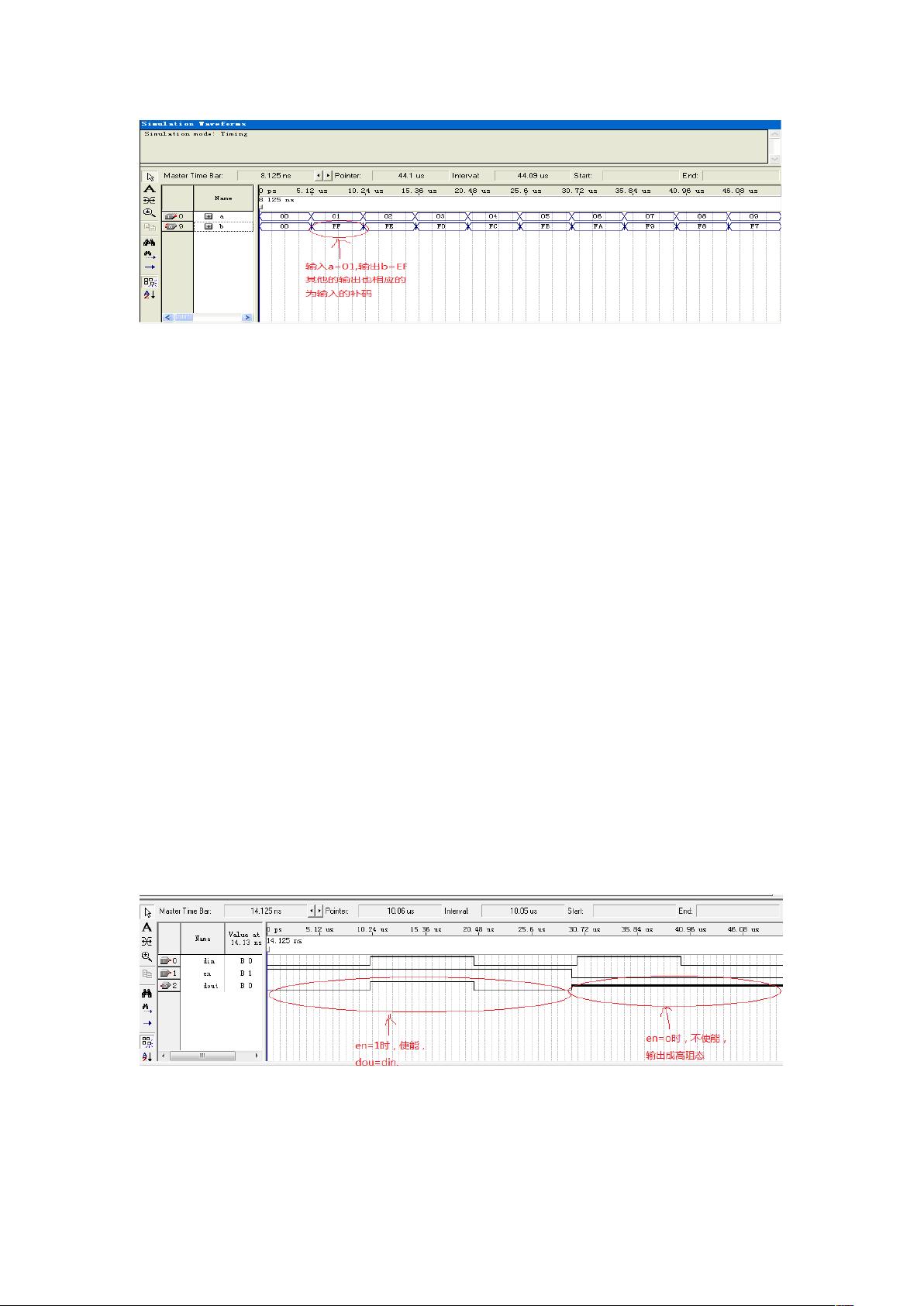

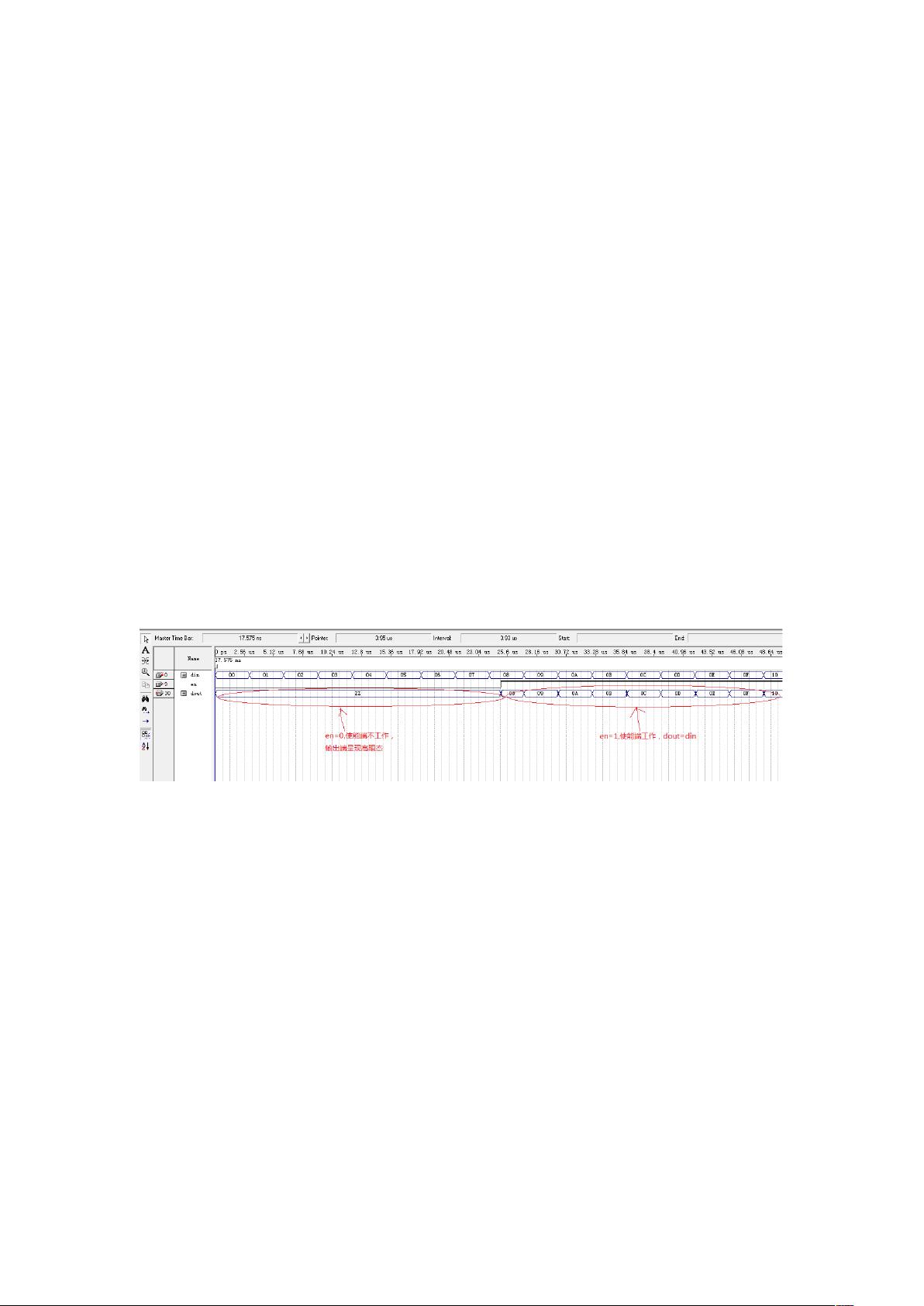

EDA的各种程序EDA设计的技术与方法 简述Quartus II 设计流程 (结合具体例子来阐述) 传统电子电路设计与EDA设计之比较 VHDL 的状态机设计方法 EDA技术的发展与应用 IP核简介及应用 比较CPLD和FPGA 漫谈EDA技术的“综合” 硬件描述语言VHDL之我见 理解阻塞型及非阻塞型过程赋值语句 Quartus ii 的功能仿真与时序仿真之比较 VHDL 行为仿真研究 EDA(Electronic Design Automation)是电子设计自动化技术的缩写,它是现代集成电路设计中不可或缺的一部分。EDA工具涵盖了从概念设计到最终实现的整个流程,包括逻辑综合、布局布线、仿真验证等多个环节。以下是对给定文件中涉及的几个关键知识点的详细解释: 1. **Quartus II 设计流程**:Quartus II 是Altera公司开发的一款FPGA/CPLD设计软件,它提供了从高层次的HDL设计到硬件实现的完整流程。设计流程通常包括:创建工程、输入设计、编译、仿真、适配、时序分析和下载到硬件等步骤。 2. **传统电子电路设计与EDA设计之比较**:传统电路设计主要依赖手工绘制电路图和手动计算,而EDA设计则利用计算机辅助设计工具,提高了设计效率和准确性,支持大规模复杂系统的快速验证和优化。 3. **VHDL 状态机设计方法**:VHDL是一种硬件描述语言,可以用来描述状态机。状态机设计通常包括定义状态、状态转换条件和输出函数。在给定的例子中,通过`PROCESS`语句和`IF-ELSIF-ELSE`结构实现了一个简单的状态机。 4. **EDA技术的发展与应用**:随着半导体技术的进步,EDA技术不断发展,从早期的逻辑门级设计扩展到了系统级设计,应用于通信、计算、汽车电子、医疗设备等多个领域。 5. **IP核简介及应用比较**:IP核( Intellectual Property Core)是指可重用的硬件模块,如微处理器、数字信号处理器等。它们可以加速设计进程,降低风险,提高设计质量。不同IP核之间的比较主要关注性能、功耗、面积和兼容性等因素。 6. **CPLD与FPGA的区别**:CPLD(Complex Programmable Logic Device)和FPGA(Field-Programmable Gate Array)都是可编程逻辑器件。CPLD适合小规模、固定功能的应用,配置速度快,功耗低;而FPGA更适合大型、灵活多变的设计,具有更高的可配置性和性能。 7. **“综合”在EDA中的含义**:综合是EDA流程中的一个关键步骤,它将高级语言描述(如VHDL或Verilog)的逻辑功能转换成门级网表,以便于进一步的布局和布线。 8. **VHDL的阻塞型与非阻塞型过程赋值语句**:阻塞型赋值(例如`=`)会立即更新变量的值,而非阻塞型赋值(例如`<=`)则会在当前进程的所有赋值完成后才更新。在设计同步电路时,非阻塞型赋值通常用于寄存器驱动,以避免数据竞争。 9. **功能仿真与时序仿真**:功能仿真验证设计逻辑是否正确,不考虑时间因素;时序仿真则考虑了延迟和时序约束,更接近实际硬件行为。Quartus II 提供的功能仿真和时序仿真帮助设计师在硬件实现前发现潜在问题。 10. **VHDL行为空间仿真研究**:行为空间仿真是基于行为描述进行的仿真,它不关注具体实现细节,主要用于验证设计的逻辑功能,例如例子中的优先级编码器、二选一选择器、译码器和补码器。 以上就是对EDA程序设计中涉及的关键知识点的详细解释,这些知识点构成了电子设计自动化的基础,并在现代电子系统设计中扮演着核心角色。

剩余26页未读,继续阅读

qq_164840612014-06-13里面程序挺多的

qq_164840612014-06-13里面程序挺多的

- 粉丝: 0

- 资源: 1

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 《孙权劝学》教学设计与反思.docx

- 《土地的誓言》教学设计与反思.docx

- 《老山界》课程设计及反思.docx

- 《黄河颂》教学方案及反思.docx

- 基于java+springboot+vue+mysql的技术交流和分享平台 源码+数据库+论文(高分毕业设计).zip

- 《诫子书》教学设计.docx

- 《散步》教学设计.docx

- 《小圣施威降大圣》教学设计.docx

- 《狼》教学设计.docx

- 《我的白鸽》教学设计.docx

- 《大雁归来》教学设计及反思.docx

- 《猫》教学设计.docx

- 《秋天的怀念》教学设计.docx

- 《雨的四季》教学设计.docx

- 《春》教学设计.docx

- 《散步》教学设计及课堂流程.docx

信息提交成功

信息提交成功