没有合适的资源?快使用搜索试试~ 我知道了~

pci express design guide

需积分: 9 9 下载量 181 浏览量

2010-04-05

08:50:30

上传

评论

收藏 136KB PDF 举报

温馨提示

试读

4页

detailed design guide for pci express system

资源推荐

资源详情

资源评论

PCI Express 3.0

Frequently Asked Questions

PCI-SIG

1) What is PCI Express (PCIe®) 3.0? What are the requirements for this evolution of the PCIe

architecture?

PCIe 3.0 is the next evolution of the ubiquitous and general-purpose PCI Express® I/O standard. At

8GT/s bit rate, the interconnect performance bandwidth is doubled over PCIe 2.0, while preserving

compatibility with software and mechanical interfaces. The key requirement for evolving the PCIe

architecture is to continue to provide a doubling of the interconnect performance over the previous

generation of the technology with low cost, low power and minimal perturbations at the platform level.

One of the main factors in the wide adoption of the PCIe architecture is its sensitivity to high-volume

manufacturing materials and tolerances such as FR4 boards, low-cost clock sources, connectors and

so on. In providing full compatibility, the same topologies and channel reach as in PCIe 2.0 will be

supported for both client and server configurations. Another important requirement is the

manufacturability of products using the most widely available silicon process technology. For the

PCIe 3.0 architecture, the PCI-SIG believes a 65nm process or better will be required to optimize on

silicon area and power.

2) What is the bit rate for PCIe 3.0 and how does it compare to prior generations of PCIe?

PCI-SIG studied 10GT/s and 8GT/s as target bit rates for PCIe 3.0. After careful consideration of the

technical analysis that comprehended complex factors including manufacturability, cost, power and

compatibility, PCI-SIG decided to adopt 8GT/s as the acceptable and most beneficial direction for the

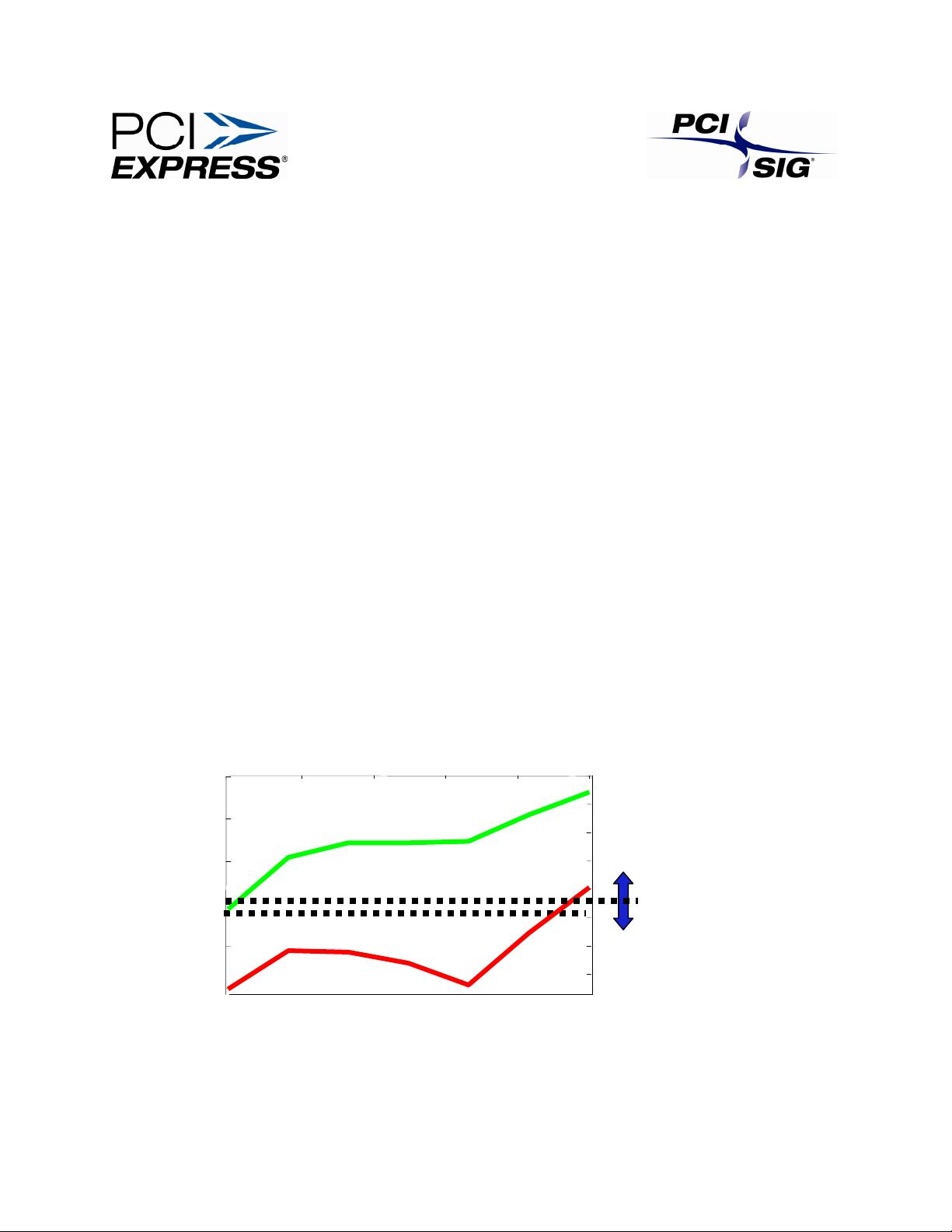

evolution of the PCIe PHY architecture. The following chart is a summary example of the extensive

study performed by the PCI-SIG technical workgroups showing feasibility for 8GT/s with low-cost

enablers for a typical client platform application such as graphics:

The PCI-SIG analysis covered multiple topologies and configurations, including servers, which are

omitted here due to space constraints. All of these studies confirmed the feasibility of 8GT/s signaling

with low-cost enablers and with minimal increases in power and silicon die size. These studies

showed, for instance, that power increased by a quadratic factor at 10GT/s.

Eye

Hei

ght

(V)

14-inch Client Channel

-0.02

0

0.0

0.0

4

0.0

0.08

8GT/s

10GT

Pass

Fail

资源评论

tom781019

- 粉丝: 0

- 资源: 5

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功