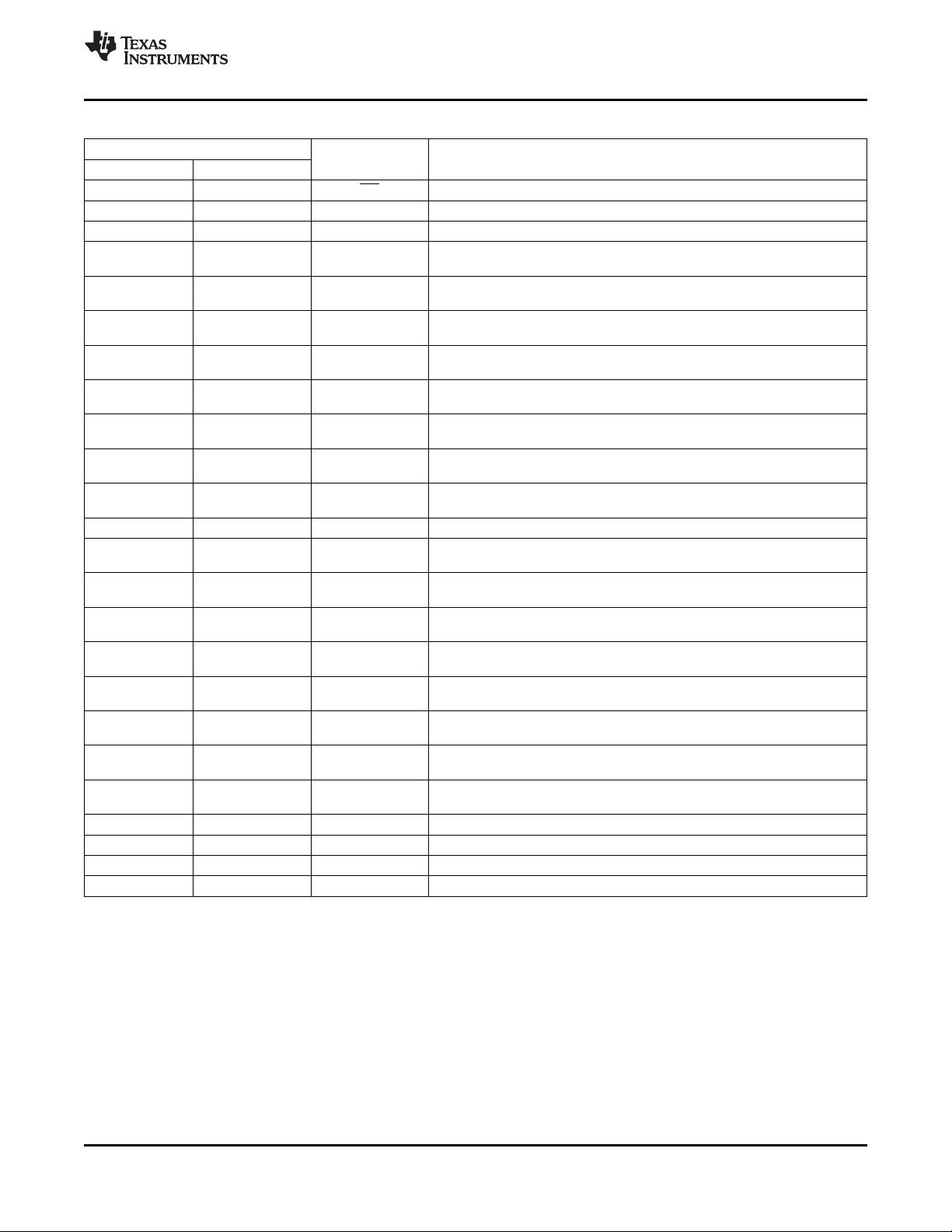

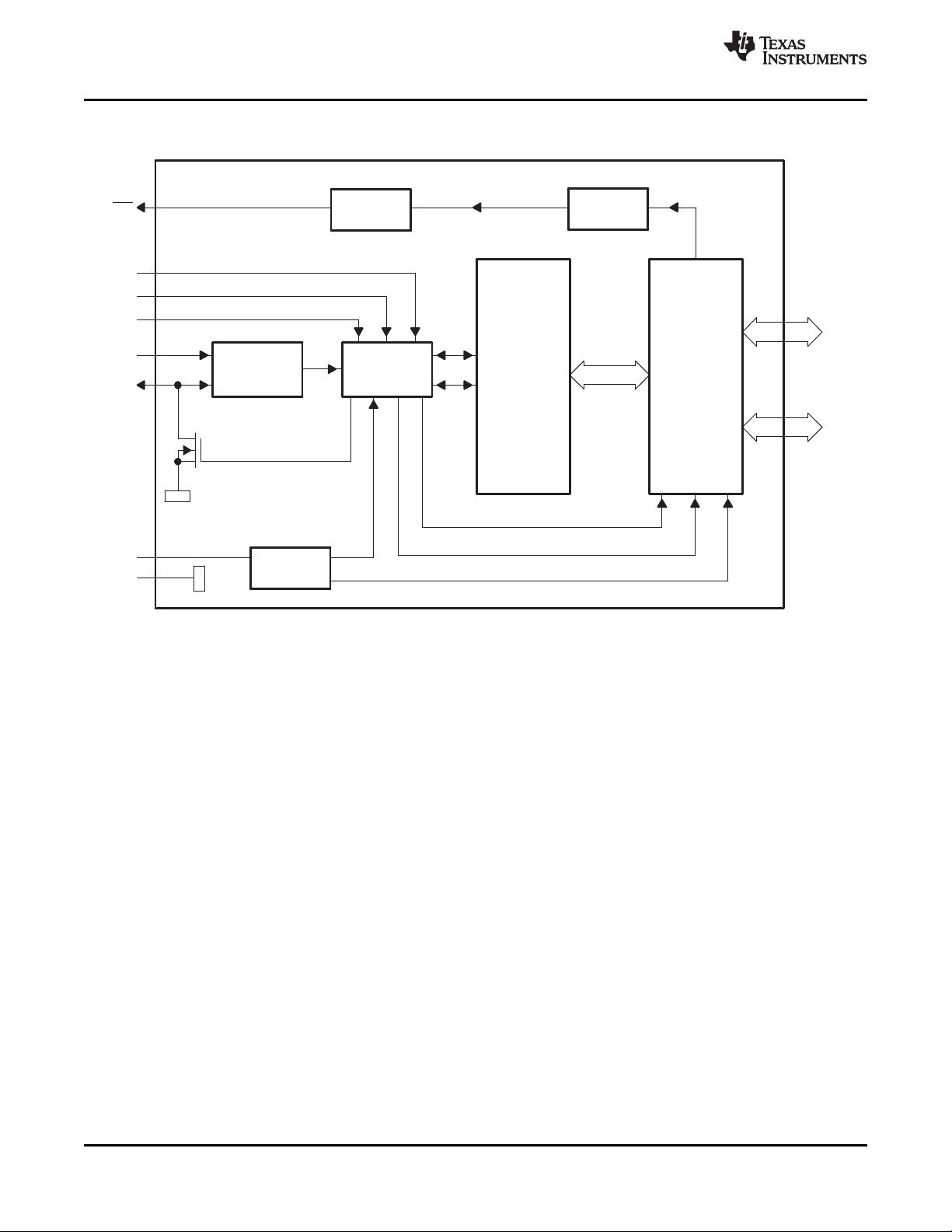

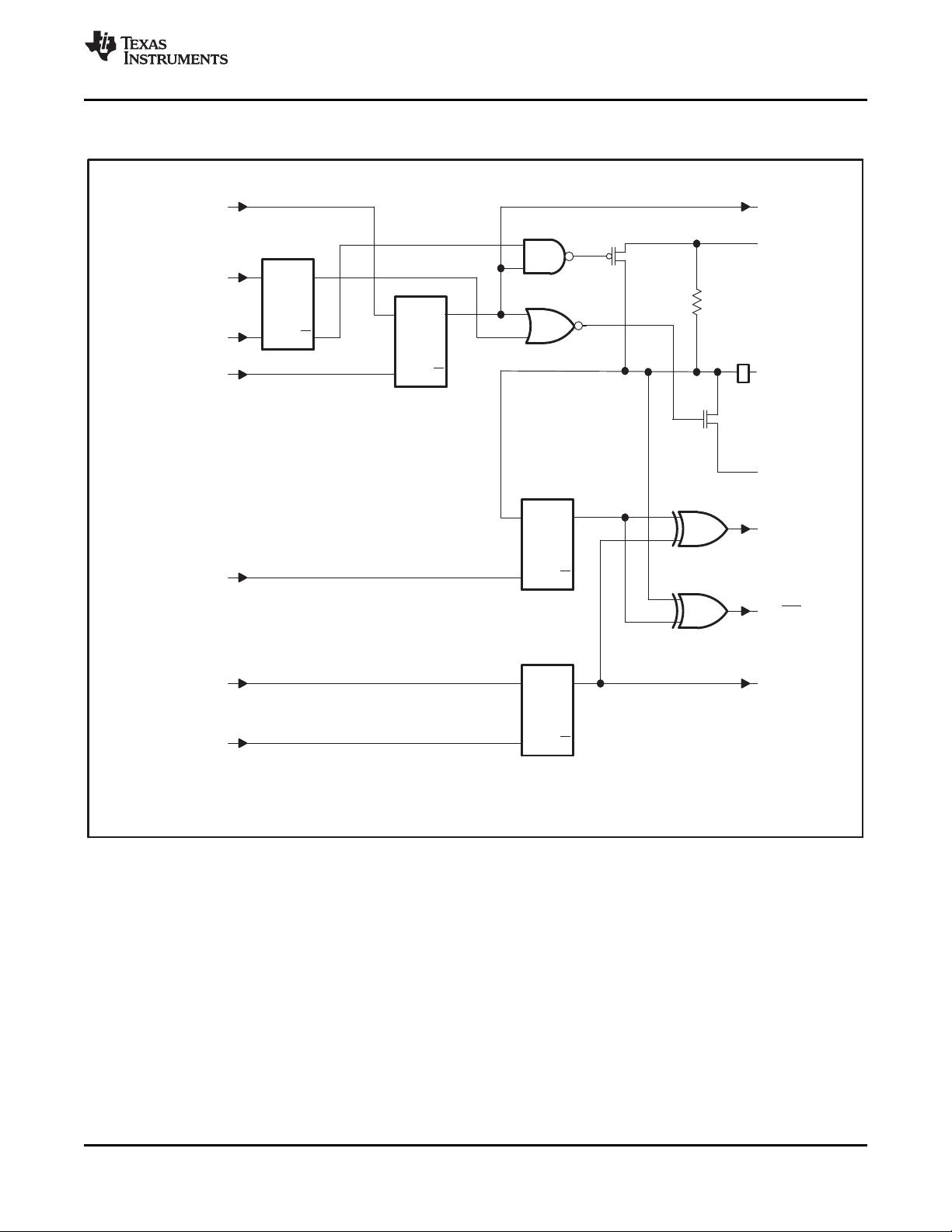

TCA9555是一款由德州仪器(Texas Instruments)生产的16位I2C和SMBus I/O扩展器。该器件通过I2C串行总线与微控制器(MCU)接口通信,用于在微控制器的I/O口不足时提供额外的I/O端口扩展。TCA9555具备多种功能,特别适用于需要I/O口扩展和中断输出的应用场景。 ### 主要特点 1. **低待机电流消耗**:最大值为3毫安,适合于电池供电的应用。 2. **中断输出**:带有开漏极、低电平有效的中断输出功能,可在输入状态发生变化时通知系统主控制器。 3. **5伏耐受性I/O端口**:允许与5伏逻辑电平兼容的设备通信。 4. **与大多数微控制器兼容**:提供广泛的兼容性,可以很容易地与各种微控制器配合使用。 5. **快速I2C总线**:支持高达400kHz的I2C总线操作,确保快速数据传输。 6. **地址硬件地址引脚**:通过三个硬件地址引脚,可实现多达八台TCA9555器件在同一总线上使用。 7. **极性反转寄存器**:能够反转输入端口寄存器的逻辑极性。 8. **锁存输出**:具有高电流驱动能力的锁存输出,适合直接驱动LED等。 9. **抗锁死性能**:超过100毫安的JESD78第二类的锁死电流性能。 10. **ESD保护**:超过了JESD22-2000伏人体模型(A114-A)、200伏机器模型(A115-A)和1000伏充电设备模型(C101)的静电放电(ESD)保护。 ### 封装类型 - **PW封装**:若暴露的中心焊盘被使用,必须作为第二地线连接或电气上保持开路。 - **RTW封装**:同上,中心焊盘用作次级接地或电气上开路。 ### 操作说明 TCA9555是为1.65伏到5.5伏的VCC操作设计的,提供16位双向I/O扩展功能。器件在上电时,所有的I/O端口默认配置为输入模式。系统主控制器可以通过写入I/O配置位,将I/O端口配置为输入或输出模式。每路输入或输出的数据均存储在相应的输入或输出寄存器中。通过极性反转寄存器可以反转输入端口寄存器的逻辑极性。系统主控制器可以读取所有寄存器。在超时或其他异常操作发生时,系统主控制器可以利用电源启动复位特性将寄存器复位到默认状态,并初始化I2C/SMBus状态机。 ### 应用领域 由于其具备诸多功能,TCA9555可以用于多种场合,例如: - **远程控制**:由于低功耗和I2C接口,非常适合于需要远程操作I/O的环境。 - **背光控制**:高电流驱动能力使得其可直接驱动LED背光。 - **状态指示**:开漏中断输出可用于指示状态变化,适用于需要监控多个传感器的系统。 - **通用I/O扩展**:对于需要更多通用I/O端口的微控制器系统,TCA9555提供了一种简单而有效的扩展方式。 使用TCA9555时,还应注意德州仪器发布的有关产品可用性、标准保修以及在关键应用中的使用注意事项的声明。由于文档部分内容可能存在OCR识别错误,建议查阅原厂产品文档获取最准确的信息。

剩余33页未读,继续阅读

- 粉丝: 0

- 资源: 1

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- (GUI框架)Matlab设计_口罩识别检测.zip

- (GUI框架)Matlab设计_垃圾分类系统.zip

- (GUI框架)Matlab设计_垃圾识别定位.zip

- (GUI框架)Matlab设计_疲劳检测GUI设计.zip

- (GUI框架)Matlab设计_疲劳专注度检测系统.zip

- (GUI框架)Matlab设计_苹果水果分级.zip

- (GUI框架)Matlab设计_脐橙水果分级.zip

- (GUI框架)Matlab设计_漂浮物识别.zip

- (GUI框架)Matlab设计_人脸门禁系统.zip

- java组件 敏感信息检测提高信息安全性

- (GUI框架)Matlab设计_人脸考勤设计.zip

- (GUI框架)Matlab设计_人脸购物系统.zip

- (GUI框架)Matlab设计_人脸识别.zip

- (GUI框架)Matlab设计_人脸识别系统.zip

- 永磁同步旋转电机发电并网控制仿真模型(可讲解) 联系本链接包括以下部分: 1. 仿真中含永磁同步发电机(PMSG)、三相整流桥、三相逆变桥、三相电网、整流桥控制模块(发电控制)、逆变桥控制模块(并网控

- (GUI框架)Matlab设计_手势控制系统.zip

信息提交成功

信息提交成功