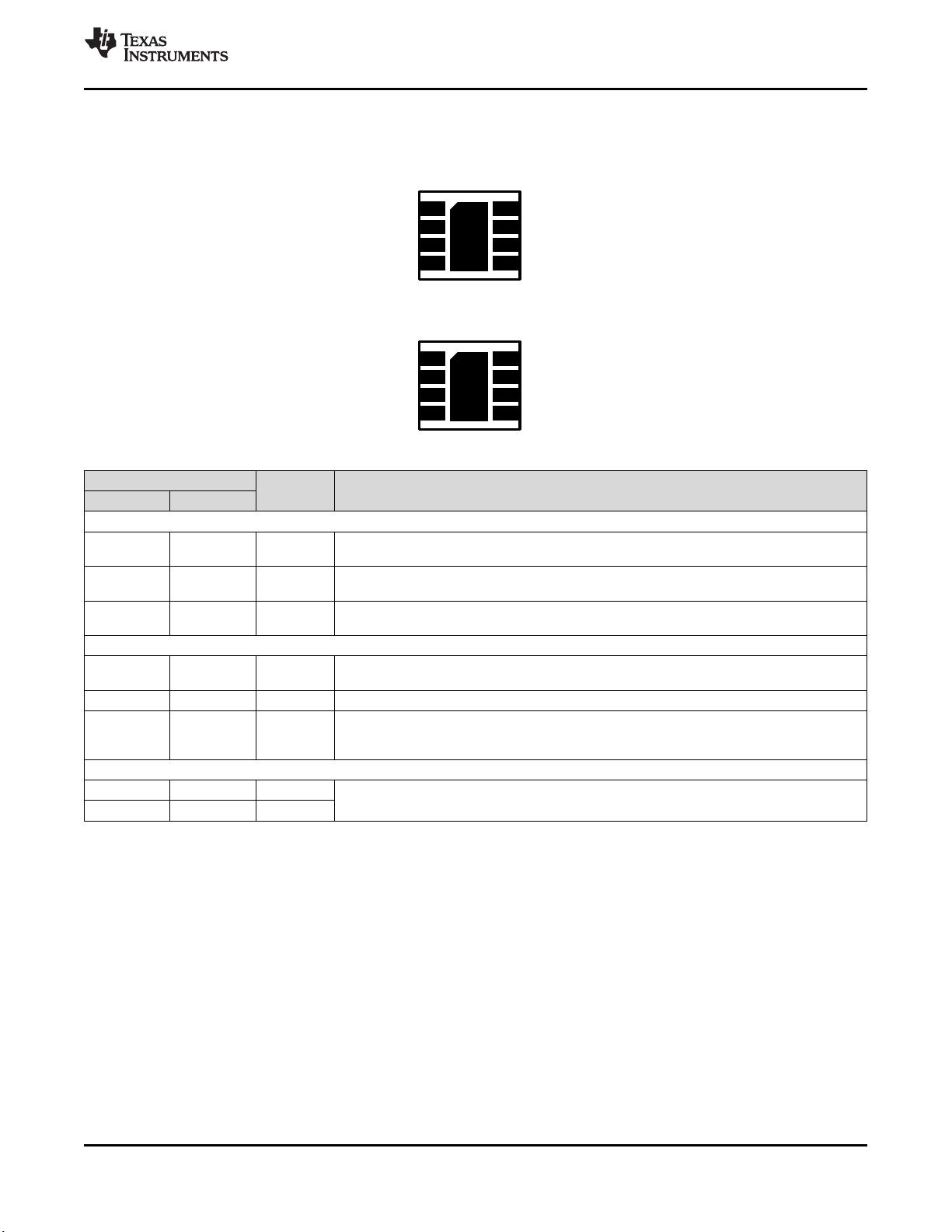

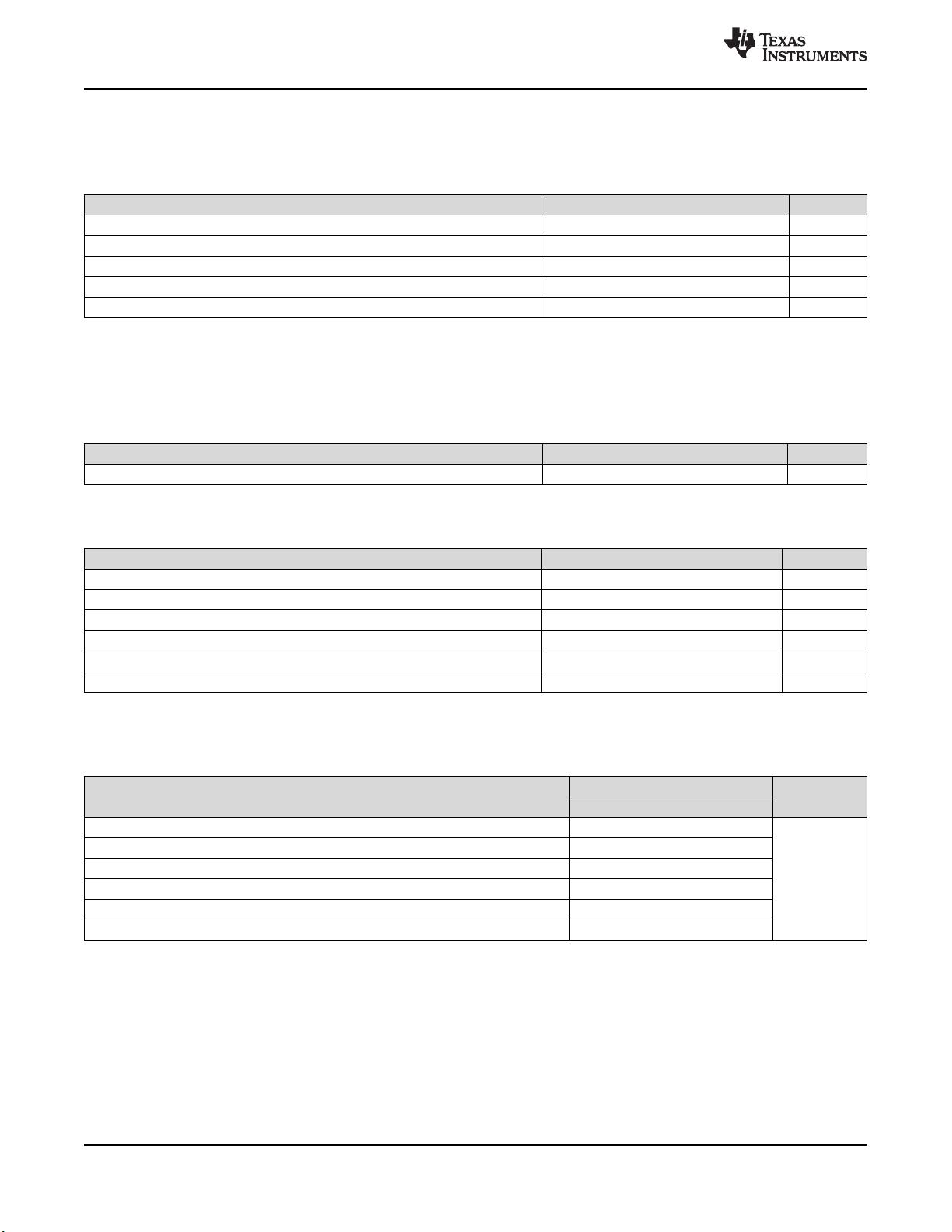

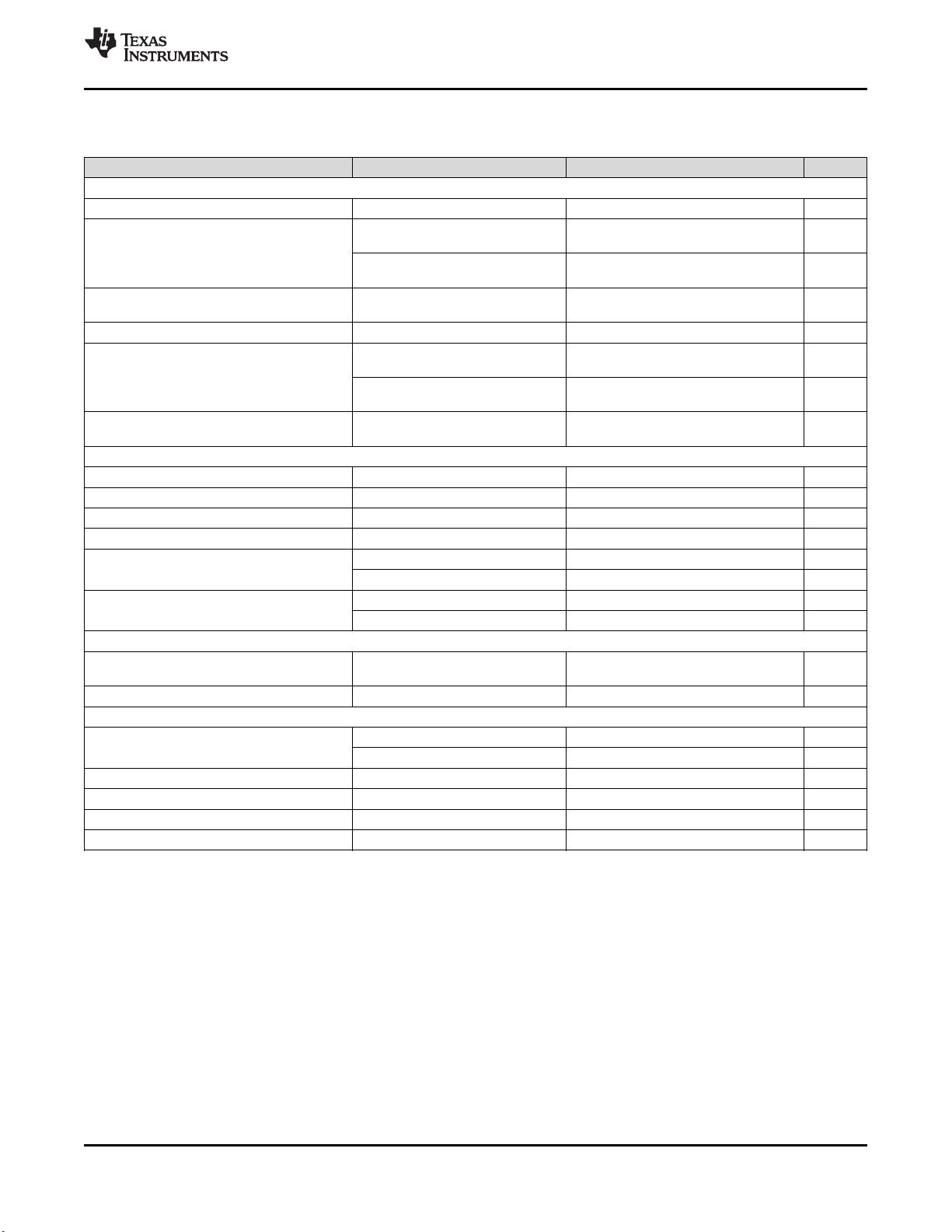

DRV8837是一款由德州仪器公司(Texas Instruments, 简称TI)生产的电机驱动芯片,它是一系列为驱动小型直流电机而设计的H桥驱动器之一,型号包括DRV8837和DRV8838。该芯片专为低电压或电池供电的应用而设计,比如摄像机、消费类电子产品、玩具以及机器人技术等。 DRV8837数据手册提供了该芯片的详细技术规范和应用指导,它在电机驱动器领域具有重要的技术参考价值。下面详细说明了该数据手册中包含的技术知识点: 1. H桥电机驱动器概念:H桥电机驱动器是一种电路配置,它可以改变电流的方向,进而控制电机的旋转方向。它由四个开关(通常是晶体管)组成,连接成桥状结构,输出端连接电机的两端。 2. MOSFET导通电阻:在DRV8837中,使用了金属氧化物半导体场效应晶体管(MOSFET)作为H桥的开关元件,具有280mΩ的导通电阻,这个参数指当MOSFET导通时,电流通过时的电阻值。 3. 电机和逻辑电源引脚:电机电源引脚(VM)允许从0到11V的电压输入,用于为电机提供动力;逻辑电源引脚(VCC)允许从1.8到7V的电压输入,用于芯片的控制逻辑部分。 4. PWM和PH/EN接口:DRV8837具备脉宽调制(PWM)控制输入,可以通过IN1/IN2引脚来控制;DRV8838则具备PH(脉冲)和EN(使能)接口,用于控制电机的速度和方向。两种接口设计符合行业标准,易于使用和接入控制系统。 5. 低功耗模式:该芯片具备低功耗睡眠模式,通过nSLEEP引脚来启用,睡眠模式下的电流消耗可降至120nA以下。 6. 封装尺寸:DRV8837和DRV8838采用WSON(超薄小外形尺寸封装)且带有PowerPAD™技术,封装尺寸为2.0mm×2.0mm,适合在空间有限的场合使用。 7. 保护特性:该驱动器具有过流保护(OCP)、热关断(TSD)以及VCC欠压闭锁(UVLO),确保在电流超载、过热或电源电压过低时,能够及时关闭输出,保护电机和驱动器本身不受损害。 8. 应用领域:由于其小巧的尺寸和低电压特性,DRV8837和DRV8838特别适合用于电池供电、低电压运动控制应用,如摄像机、DSLR镜头、消费类产品、玩具、机器人技术、医疗设备等。 9. 设备功能模式:手册描述了该芯片的不同工作模式,例如正常模式、低功耗睡眠模式以及保护模式,这些模式的切换使得设备能够根据工作状态和外围条件灵活调整能耗和运行状态。 10. 电源推荐:手册还提供了关于如何选择和配置电机电源以及逻辑电源的指导,以确保驱动器的稳定工作。 11. 布局指导:为了确保电路板的信号完整性和电磁兼容性,数据手册提供了布局指导和布局示例,帮助设计者在PCB设计中合理布局相关元件。 12. 设备和文档支持:提供相关的技术支持链接、商标信息和数据表,方便用户和技术人员查找进一步的信息和帮助。 在设计包含DRV8837或DRV8838的电机驱动电路时,了解和应用上述知识点是十分重要的,这有助于确保电路的稳定、高效和安全运行。

剩余27页未读,继续阅读

- 粉丝: 2

- 资源: 8

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 自考数据库系统原理04735真题含答案(2011.1-2017年)

- YOLO算法-有轨车辆数据集-2013张图像带标签-身体-联轴器-车轮.zip

- YOLO算法-火车-轨道数据集-2164张图像带标签-火车-轨道.zip

- 05-大数据概论(1).zip

- WebSocketB/S前后端链接通信-simple-Chat实现(应用)

- YOLO算法-瓶纸盒合并数据集-3161张图像带标签-纸张-纸箱-瓶子.zip

- YOLO算法-检测车数据集-2622张图像带标签-货车-发动机.zip

- YOLO算法-自卸卡车-挖掘机-轮式装载机数据集-2644张图像带标签-自卸卡车-挖掘机-轮式装载机.zip

- 离散数学课件全国自考02324

- YOLO算法-火灾和人员探测数据集-3039张图像带标签-人-烟-火.zip

- YOLO算法-产品识别数据集-5166张图像带标签-可口可乐.zip

- YOLO算法-数据集数据集-330张图像带标签-椅子-书桌.zip

- SwinTransformer 改进:添加SelfAttention自注意力层

- YOLO算法-可回收垃圾检测数据集-1142张图像带标签-纸张-纸箱-瓶子.zip

- YOLO算法-锡罐-牙罐-盖子打开数据集-179张图像带标签-锡罐-牙罐-盖子打开.zip

- YOLO算法-汽车数据集-5000张图像带标签-.zip

信息提交成功

信息提交成功