adjacent series FET is off (high resistance state) and

vice-versa.

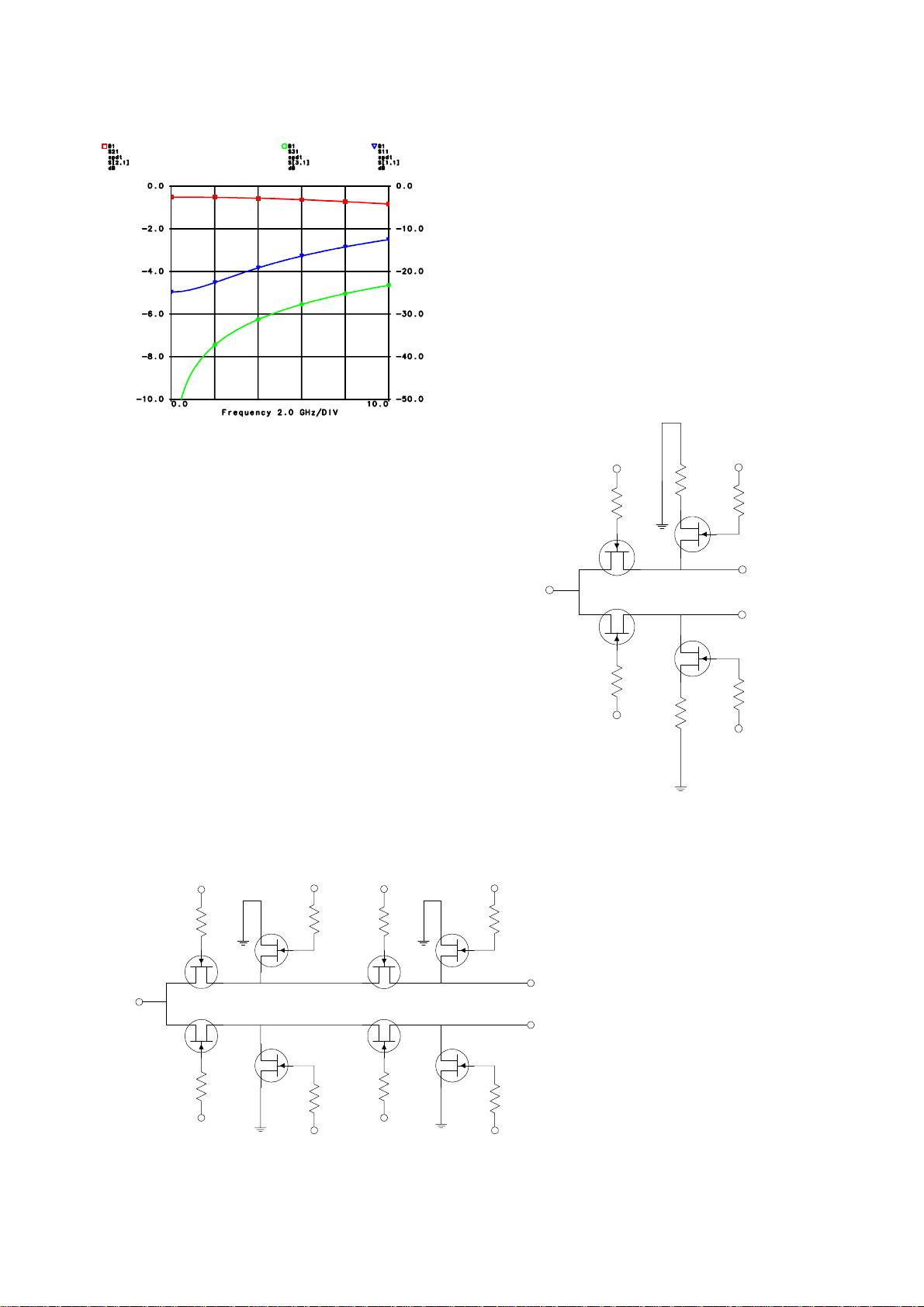

Figure 6 is a plot of the simulated performance of a

series/shunt switch. The isolation has increased by

around 10dB compared to the simple series FET design

but the insertion loss has increased very little. It should

be noted that the simulations have assumed ideal

grounding for the shunt FETs. Very low inductance

grounding can be achieved on many GaAs processes by

the use of low inductance, through-substrate vias.

However, in order to keep processing costs down, many

switch IC manufacturers tend not to make use of through

GaAs via holes and grounding must be provided using

bond-wires. The inductance of the bond-wire will

obviously degrade the switch isolation, as will any

additional packaging parasitics. It should also be noted

that the use of shunt FETs can degrade the power

handling capability of the design, as explained later.

The two switch topologies presented above are both

reflective designs, that is the return loss of the off-arm

is low. Terminated switches can be easily realised by

including a shunt FET and resistor (Rt) at each output,

as shown in Figure 7. In the off case Rt will be

connected to the output by the shunt mounted FET.

Choosing the combined resistance of the FET and Rt

to be 50Ω provides a well matched off-case output,

this is known as a terminated switch design.

If more isolation is required, than can be provided by a

single series/shunt design, cascading pairs of

series/shunt FETs, as shown in Figure 8, can achieve

this. The extra switch isolation

is provided at the expense of

increased insertion loss.

The simulated performance of

this double series/shunt design is

shown in Figure 9. Very good

isolation is achieved all the way

up to 10GHz, however the input

return loss is degrading with

frequency and the insertion loss

is gradually increasing. As with

the single series/shunt design,

the use of bond-wires for

grounding the shunt FETs will

degrade the isolation.

Figure 6: Simulated performance of

series/shunt SPDT

Rg

V2

V1

Rg

RFin

V1

Rg

Rg

V2

RFout_1

RFout_2

Rt

Rt

Figure 7: Terminated series/shunt SPDT

Rg

V2

V1

Rg

RFin

V1

Rg

Rg

V2

RFout_1

RFout_2

V1

Rg

Rg

V2

Rg

V2

V1

Rg

Figure 8: Double series/shunt SPDT

评论0

最新资源