Firmware Design Document

Firmware

Design

Document

Author: Paul

Project Leader: Zheng Cao

Date: 5

th

November 2005

Module Name: transmit engine

Firmware Design Document

This page is left intentionally blank.

Firmware Design Document

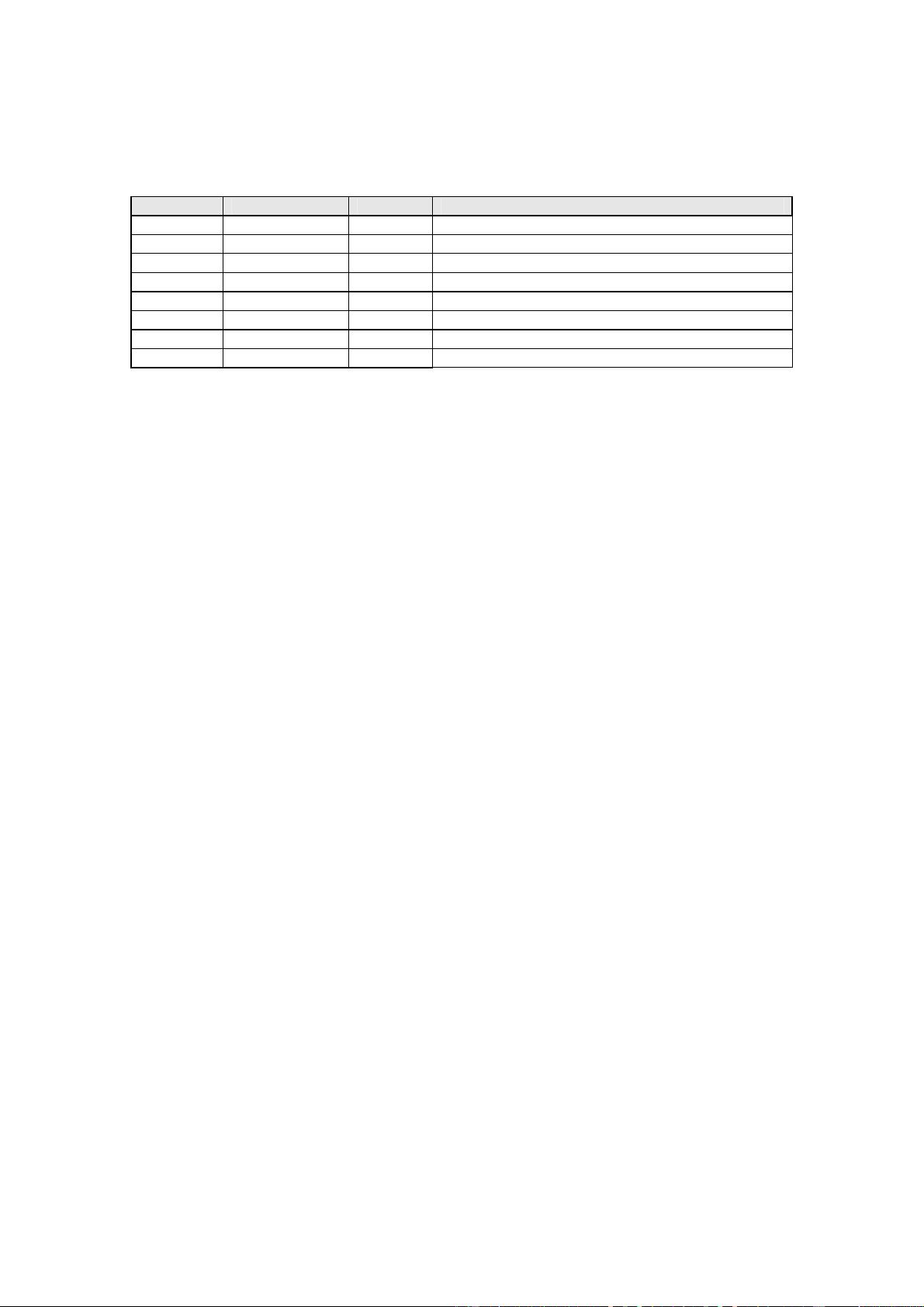

Revision History

Date Author Issue Comment

05/11/2005 P.L. 1.0 First Version

Firmware Design Document

Page 2 5/31/2006

Reference

[1] 10G Ethernet Mac System Design Issue 1.0

[2] Xilinx LogiCORE 10-Gigabit Ethernet MAC User Guide

[3] IEEE 802.3ae Media Access Control (MAC) Parameters, Physical Layers,

and Management Parameters for 10 Gb/s Operation

Firmware Design Document

Page 3 5/31/2006

Contents

1 Introduction...............................................................................1

2 Detailed Design........................................................................1

2.1 Module Description................................................................................................... 1

2.2 Module Interface....................................................................................................... 1

2.3 Module Design ......................................................................................................... 1

2.4 Block Diagram.......................................................................................................... 1

2.5 Code Listing ............................................................................................................. 1

3 Traceability Matrix ....................................................................1

4 Abbreviation .............................................................................1

Appendix A .....................................................................................1

List of Tables

Table 2-1 Client-side interface................................................................................................... 1

Table 2-2 Physical-side interface .............................................................................................. 1

Table 2-3 Flow control interface ................................................................................................1

Table 2-4 MDIO interface .......................................................................................................... 1

Table 2-5 Receiver interface ..................................................................................................... 1

Table 2-6 Transmitter Configuration Word................................................................................ 1

Table 2-7 Control Characters ....................................................................................................1

List of Figures

Figure 2-1 Diagram of the Transmit Block................................................................................. 1

Figure 2-2 IEEE 802.3x Frame.................................................................................................. 1

Figure 2-3 PAUSE Frame..........................................................................................................1

Figure 2-4 Virtual LAN Frame....................................................................................................1

Figure 2-5 Block diagram of the transmit process..................................................................... 1

Figure 2-6 Code Listing ............................................................................................................. 1

Figure 3-1 Traceability Matrix.................................................................................................... 1

Figure 0-1 Frame Transmission Across Client-Side interface [Ref. 2]...................................... 1

Figure 0-2 Frame Transmission with Client-supplied FCS [Ref. 2]........................................... 1

Figure 0-3 Aborting a frame transmission [Ref. 2]..................................................................... 1

Figure 0-4 Back-to-Back Frame Transmission, no back pressure [Ref. 2] ............................... 1

Figure 0-5 Back-to-Back Frame Transmission with Back Pressure from MAC [Ref. 2]............ 1

Figure 0-6 Inter Frame Gap Adjustment [Ref. 2]....................................................................... 1

Figure 0-7 Transmission of a VLAN Tagged Frame [Ref. 2]..................................................... 1

Figure 0-8 Normal frame transmissions [Ref. 3]........................................................................ 1

Figure 0-9 Transmit Error Propagation [Ref. 3]......................................................................... 1