单片机数字频率计设计.doc

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

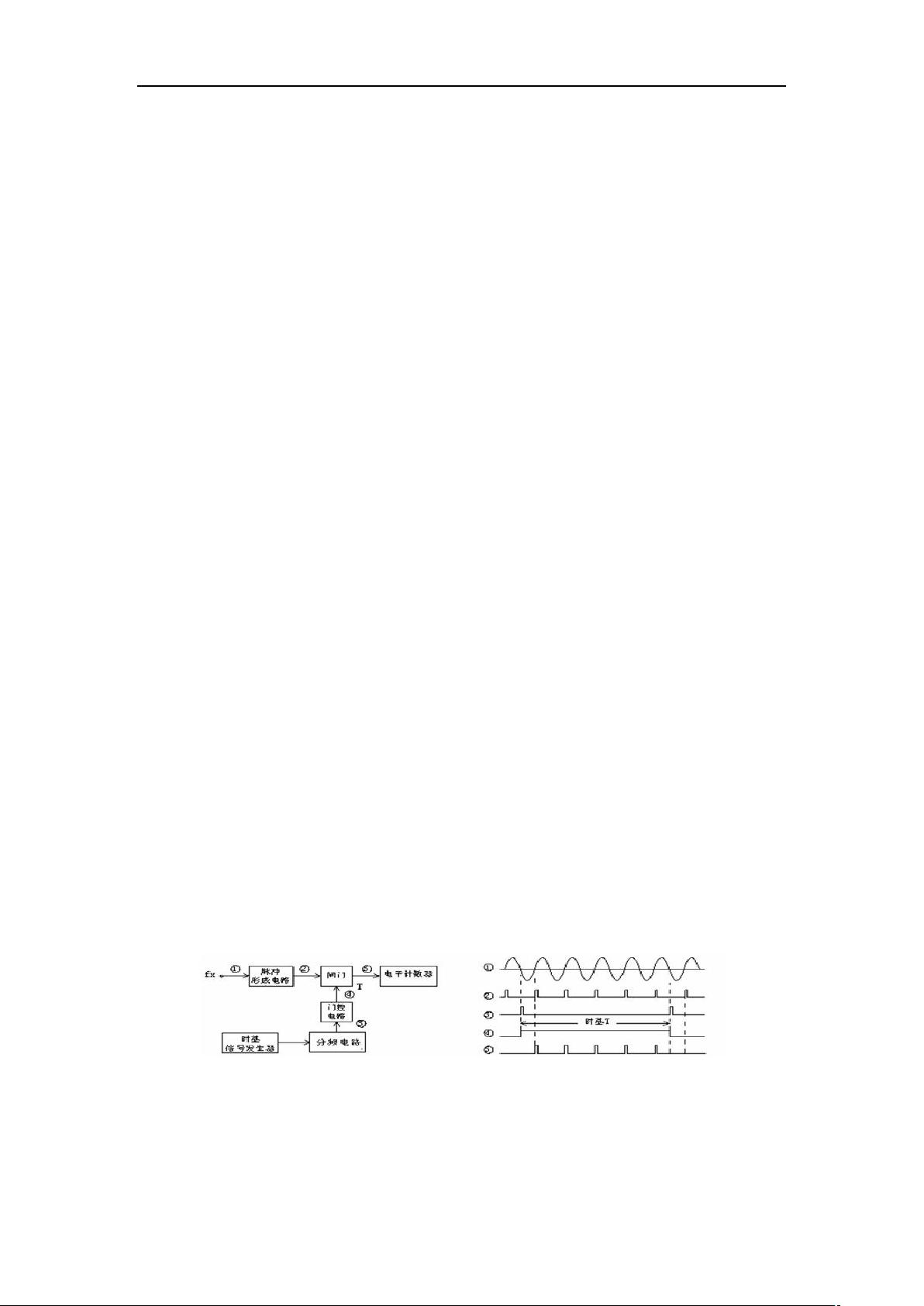

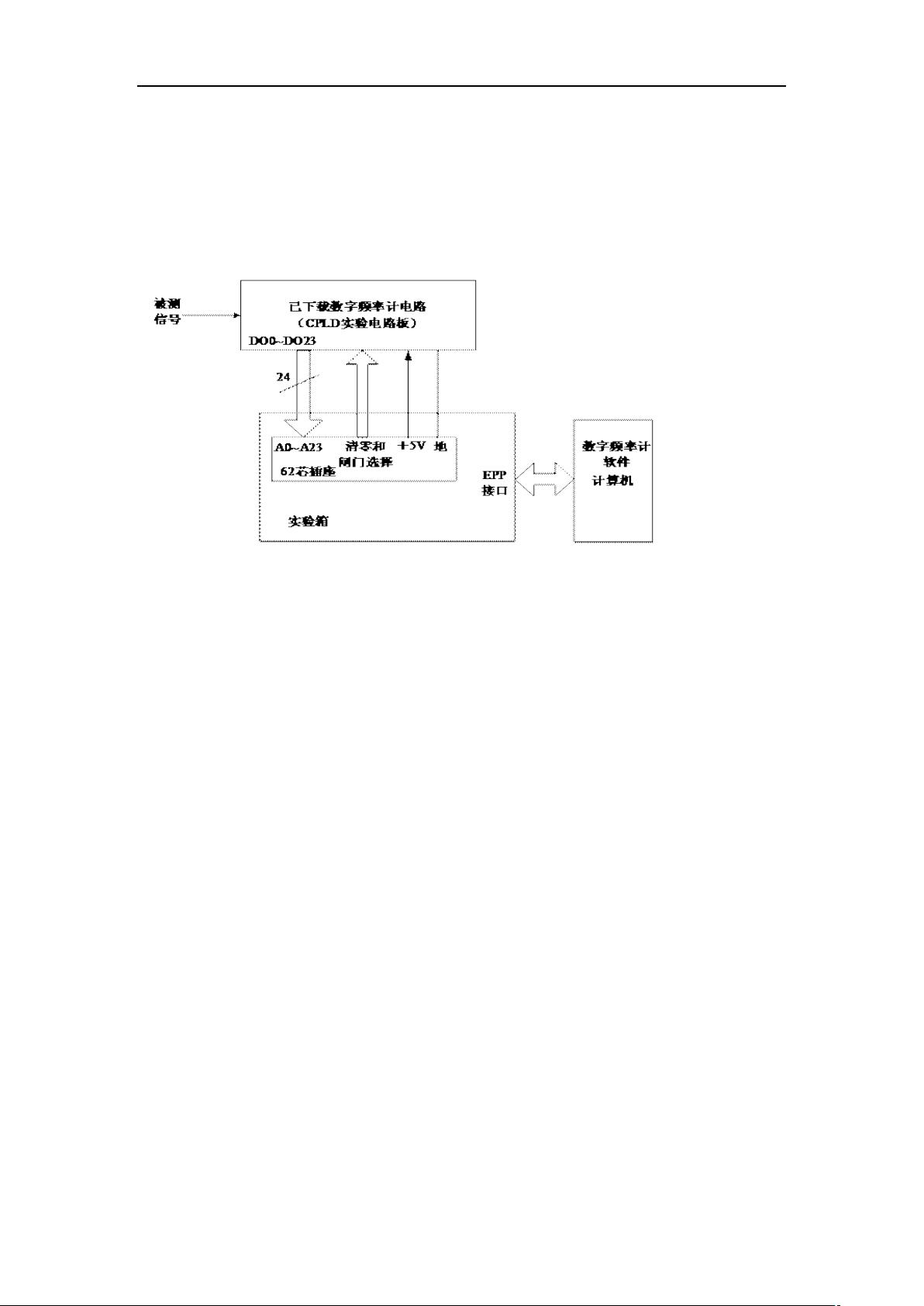

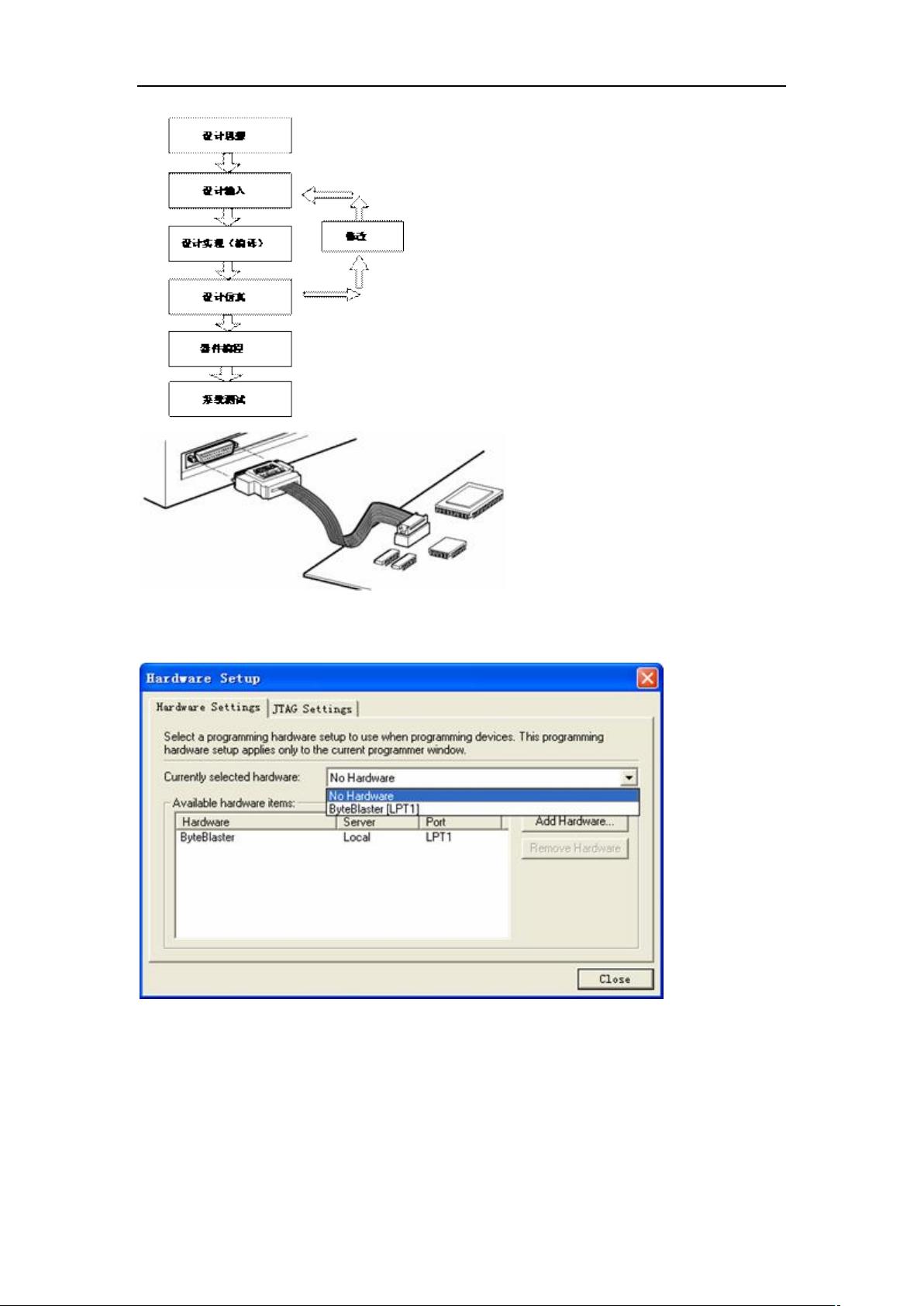

数字频率计设计 一、实验目的 1.熟悉CPLD的开发软件的基本使用。 2.理解频率计的测量原理。 3.掌握CPLD逻辑电路设计方法。 4.掌握虚拟数字频率计的软件设计。 二、实验任务和内容 1. 在CPLD中设计一个数字频率计电路,设计要求为: 测量范围:1Hz~1MHz, 分辨率<10-4>, 数码管动态扫描显示电路的CPLD下载与实现。 2.使用LabVIEW进行虚拟频率计的软件设计。要求设计软件界面,闸门时间为4档,1s,1 00ms,10ms,1ms,频率数字显示。 3.使用设计虚拟逻辑分析仪软件和CPLD电路,进行软硬件调试和测试 三、实验器材 1. SJ-8002B电子测量实验箱 1台 2.计算机(具有运行windows2000和图形化控件的能力) 1台 3.函数发生器 1台 4.SJ-7002 CPLD实验板 1块 5.短接线若干 四、实验原理 4.1.测频原理 所谓"频率",就是周期性信号在单位时间变化的次数。电子计数器是严格按照f=N/T的 定义进行测频,其对应的测频原理方框图和工作时间波形如图1 所示。从图中可以看出测量过程:输入待测信号经过脉冲形成电路形成计数的窄脉冲, 时基信号发生器产生计数闸门信号,待测信号通过闸门进入计数器计数,即可得到其频 率。若闸门开启时间为T、待测信号频率为fx,在闸门时间T内计数器计数值为N,则待 测频率为 fx = N/T (1) 若假设闸门时间为1s,计数器的值为1000,则待测信号频率应为1000Hz或1.000kHz,此 时,测频分辨力为1Hz。 本实验的闸门时间分为为4档:1s,100ms,10ms,1ms。 图1 测频原理框图和时间波形 4.2 数字频率计组成 本实验要求的数字频率计组成如图2所示,频率计的硬件电路(图1所示)在CPLD芯片中 实现,测量结果通过实验箱提供的EPP通信接口送给计算机,频率计的软件和人机界面由 计算机完成,同时计算机还可输出清零和闸门选择的控制信号给电路。 本实验的任务一是在提供的CPLD实验板上设计和实现频率计测量电路,二是在计算机上 使用LabVIEW软件设计频率计界面和程序。 图2 数字频率计组成框图 4.3 CPLD特点和设计流程 CPLD器件是由用户配置以完成某种逻辑功能的电路,本CPLD实验电路板选用ALTERA公司 的EPM7128SLC84器件,其特点为:84引脚Pin,内部有128个宏单元、2500个等效逻辑门 、15ns的速度、PLCC84封装形式。除电源引脚、地线引脚、全局控制引脚和JTAG引脚外 ,共提供了64个可用I/O脚,这些引脚可以任意配置为输入、输出和双向方式。 CPLD的设计流程如图3所示,本实验采用的设计软件为ALTERA公司的Quartus ,下载方式采用的是并口电缆ByteBlaster。下载时的硬件设置操作如图4所示。 图3 CPLD设计流程和并行电缆下载示意图 图4 下载时的硬件设置选ByteBlaster 4.4 CPLD实验电路板 1)数字信号输入:8个ON~OFF(K1~K8)开关 2) 数字信号输出(显示):8个LED灯(LED1~LED8),低电平点亮 3) 6个LED 7段数码管,采用动态扫描方式,L1、L2、L3为位选信号,低有效,A、B、……、G为7段码 ,DP为小数点,均为低有效。 4) 时钟晶振:频率为1MHz,已连接到CPLD的时钟引脚 注:使用CPLD板的1.000MHz的晶振时钟,需放置CPLD板上S1短路块位置在右面。 图5 CPLD实验板电路板照片和组成框图 4.5 CPLD实验电路板原理和与实验箱62芯插座连接关系 图6 为CPLD板的详细电路图。 CPLD可供用户自定义的引脚见表1,共有25个引脚,均可根据需要定义为输入或输出。 CPLD与实验箱62芯插座定义表见表2,可使用3个8位的数字I/O口作为频率计的输入计数 结果,1个5位的单向数据输出口为频率计的控制口。 表1 用户可用的CPLD自定义I/O引脚 " "P5 "P6 "P8 " "P4 " " " " "00H "D7-D"全局清零信号(在读"EPP初始化时发清零 " " "0 "数、采集、启动信 "信号 " " " "号源之前都必须)? " " " " "(00H?00) " " "01H "D2-D"小板控制使能(U019"在本实验中需使能 " " "0 ",U020,U021片选)," " " " " " " " " "0:禁止 " " " " "1:使能 " " "02H "D2-D"DO0-DO23数据方向 "在本实验中都设为输" " "0 "控制 "入 " " " "0:输入(外部à主板" " " " ") " " " " "1:输出(主板à外部" " " " ") " " "03H 【单片机数字频率计设计】的实验旨在深入理解和应用复杂可编程逻辑器件(CPLD)进行电子设备设计,特别是在构建数字频率计方面。实验的主要目标包括掌握CPLD开发软件的使用、理解频率测量的基本原理、学习CPLD逻辑电路设计方法以及虚拟数字频率计的软件设计。 实验内容涉及在CPLD中设计一个测量范围从1Hz到1MHz,分辨率达到10^-4的数字频率计。设计中需利用动态扫描的数码管显示测量结果,并通过CPLD实现电路下载。此外,实验还要求利用LabVIEW软件创建虚拟频率计的用户界面,设置4种不同的闸门时间(1s、100ms、10ms和1ms),并能够以数字形式显示频率。 测频原理基于信号的周期性,即在单位时间内信号变化的次数。电子计数器通过计算在固定时间间隔内接收到的信号周期数来确定频率。本实验中,闸门时间分为4档,改变闸门时间可以适应不同频率的测量需求。例如,当闸门时间为1s,计数器计数1000次,则频率为1000Hz。 数字频率计的组成包括CPLD实现的硬件电路和计算机上的软件部分。硬件电路处理输入信号,通过CPLD进行计数和处理,然后将测量结果通过EPP接口传输到计算机。计算机则负责显示和控制,提供人机交互界面,同时输出控制信号以选择闸门时间和清零计数器。 CPLD器件,如ALTERA的EPM7128SLC84,拥有丰富的I/O资源和高速处理能力,适合用于这种实时频率测量应用。设计流程包括使用Quartus II软件进行逻辑设计、仿真和下载。下载工具是ByteBlaster,并口电缆,硬件设置需遵循特定的步骤。 CPLD实验板提供了各种输入和输出接口,包括8个ON/OFF开关作为数字输入,8个LED灯和6个7段数码管用于显示,以及1MHz时钟晶振。实验板上的62芯插座与CPLD的I/O引脚对应,允许灵活配置和连接。 通过这个实验,学生不仅可以掌握CPLD硬件设计,还能了解虚拟仪器软件设计,提高在电子测量和信号处理领域的综合能力。实验要求的复杂性和实践性确保了学生在理论和实践两方面都能得到充分的锻炼。

剩余12页未读,继续阅读

- 粉丝: 192

- 资源: 3万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功