1

多功能数字钟的 FPGA 的设计与实现

专业: 电子信息工程

班级: 1 5

电子一班

组员:周景 1 5 0 5 01 1 0 4 3

蒋晓东 1 5 0 5 01 1 03 0

王鹏 1 5 0 5 01 1 0 2 7

指导老师: 黄慧

2

2018.12.25

目录

设计要求.........................................................................................................3

一. 设计实现功能........................................................................................3

二. 各个设计模块描述................................................................................4

(一) 计时模块............................................................................................4

(二) 设置时间模块....................................................................................9

(三) 整点报时模块..................................................................................13

(四) 显示时间模块..................................................................................14

(五)分频模块................................................................................. ..........19

(六)闹钟模块................................................................................. ..........20

三. 整体电路图..........................................................................................22

四. 心得和体会..........................................................................................22

五.参考文献....................................................................................... ........22

3

设计要求

1.进行正常的时、分计时功能,二十四小时制计时

2.由数码管显示 24h、60min

3.设置时间

4.整点报时

5.闹钟功能

一.设计实现功能

该数字电子钟能够实现时、分计时功能;闹钟开、闹钟关功能闹钟就

绪灯亮,蜂鸣器响;整点报时的功能;

4

二.各个设计模块描述

(一)计时模块

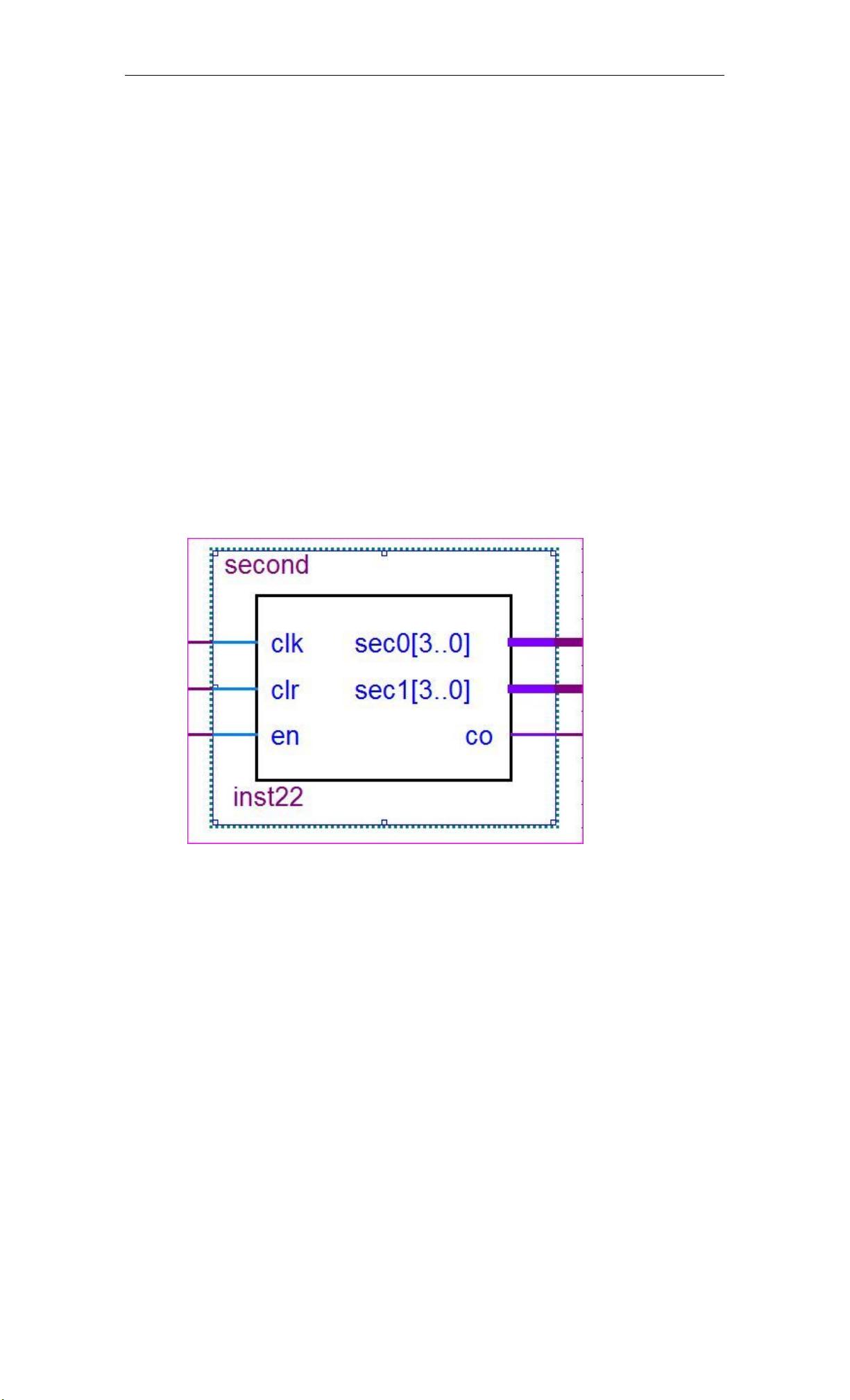

1. 秒计数是由一个六十进制的计数器构成,生成元器件如下

Clk:驱动秒计时器的时钟信号

Clr:校准时间时清零的输入端

En:使能端

Sec0[3..0] sec1[3..0]:秒的高位显示,低位显示

Co:进位输出端,作为分的 clk 输入

5

代码如下:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity second is

port (clk,clr,en:in std_logic;

sec0,sec1:out std_logic_vector(3 downto 0);

co:out std_logic);

end second;

architecture sec of second is

SIGNAL cnt1,cnt0:std_logic_vector(3 downto 0);

begin

process(clk)

begin

if(clr='0')then

cnt0<="0000";

cnt1<="0000";

elsif(clk'event and clk='1')then

if(en='1')then

if cnt1="0101" and cnt0="1000" then

co<='1';

cnt0<="1001";

elsif cnt0<"1001" then

cnt0<=(cnt0+1);

else

cnt0<="0000";

if cnt1<"0101"then

cnt1<=cnt1+1;

else

cnt1<="0000";

co<='0';

end if;

end if;

end if;

end if;

sec1<=cnt1;

sec0<=cnt0;

end process;

end sec;

仿真图如下: