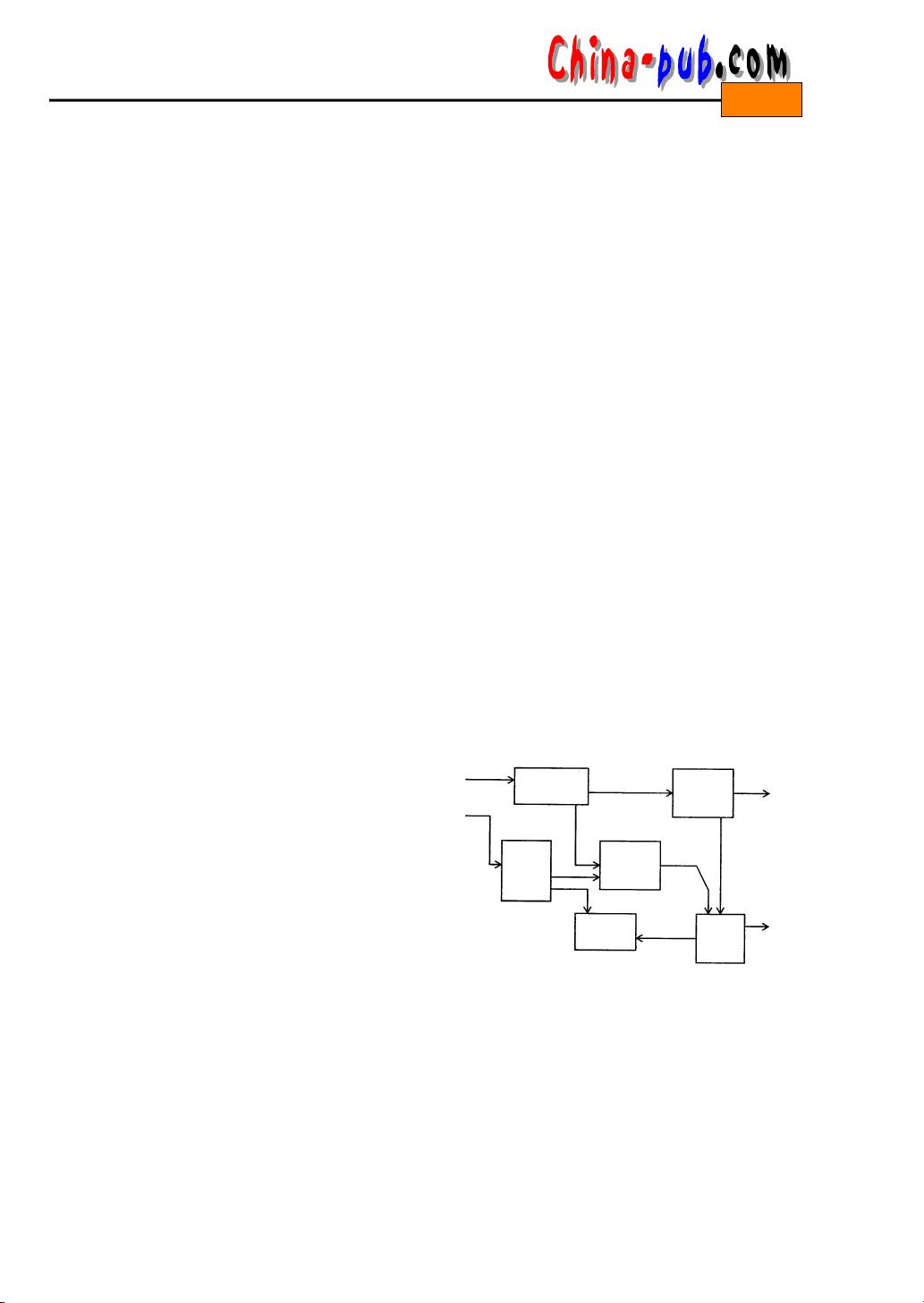

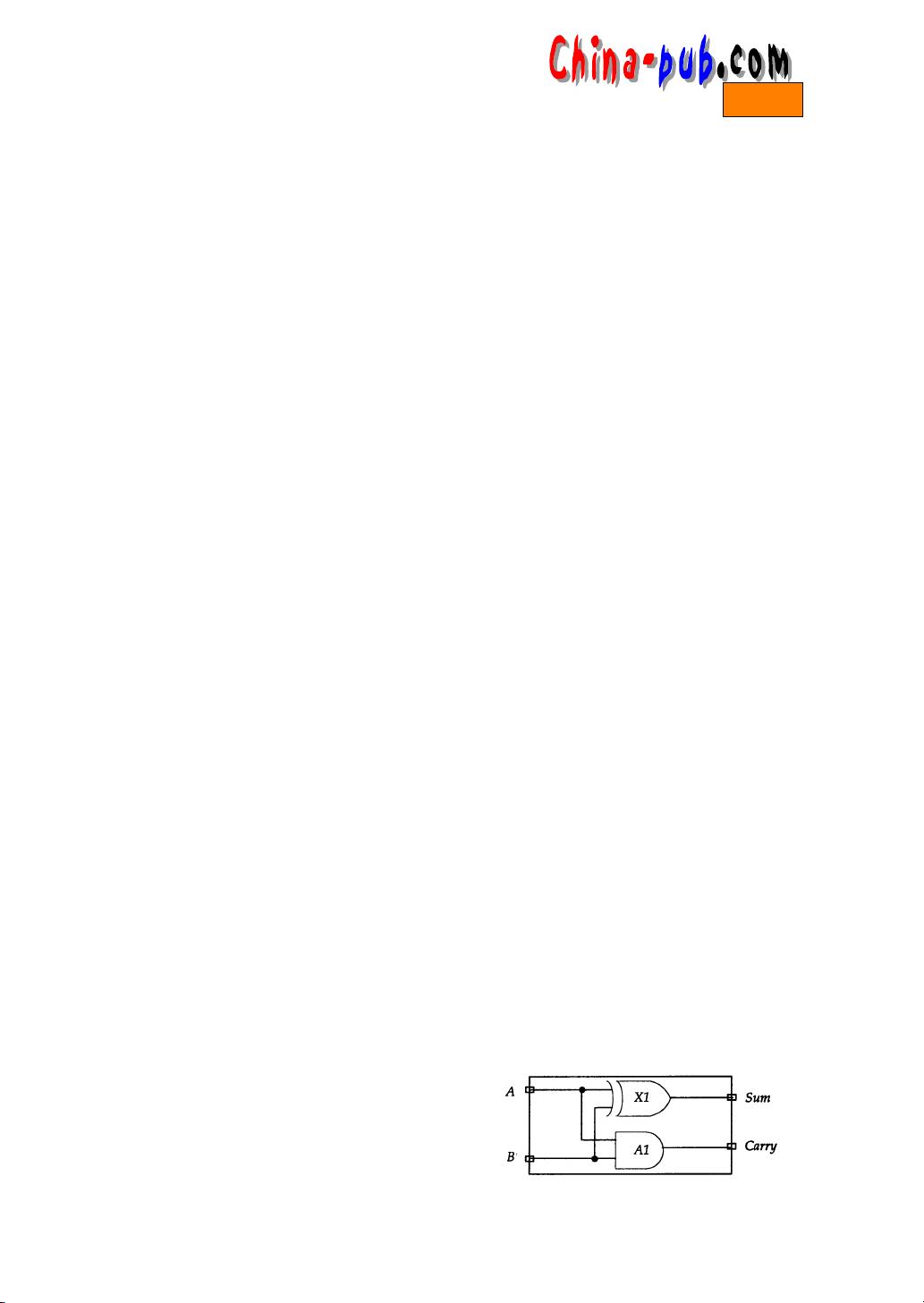

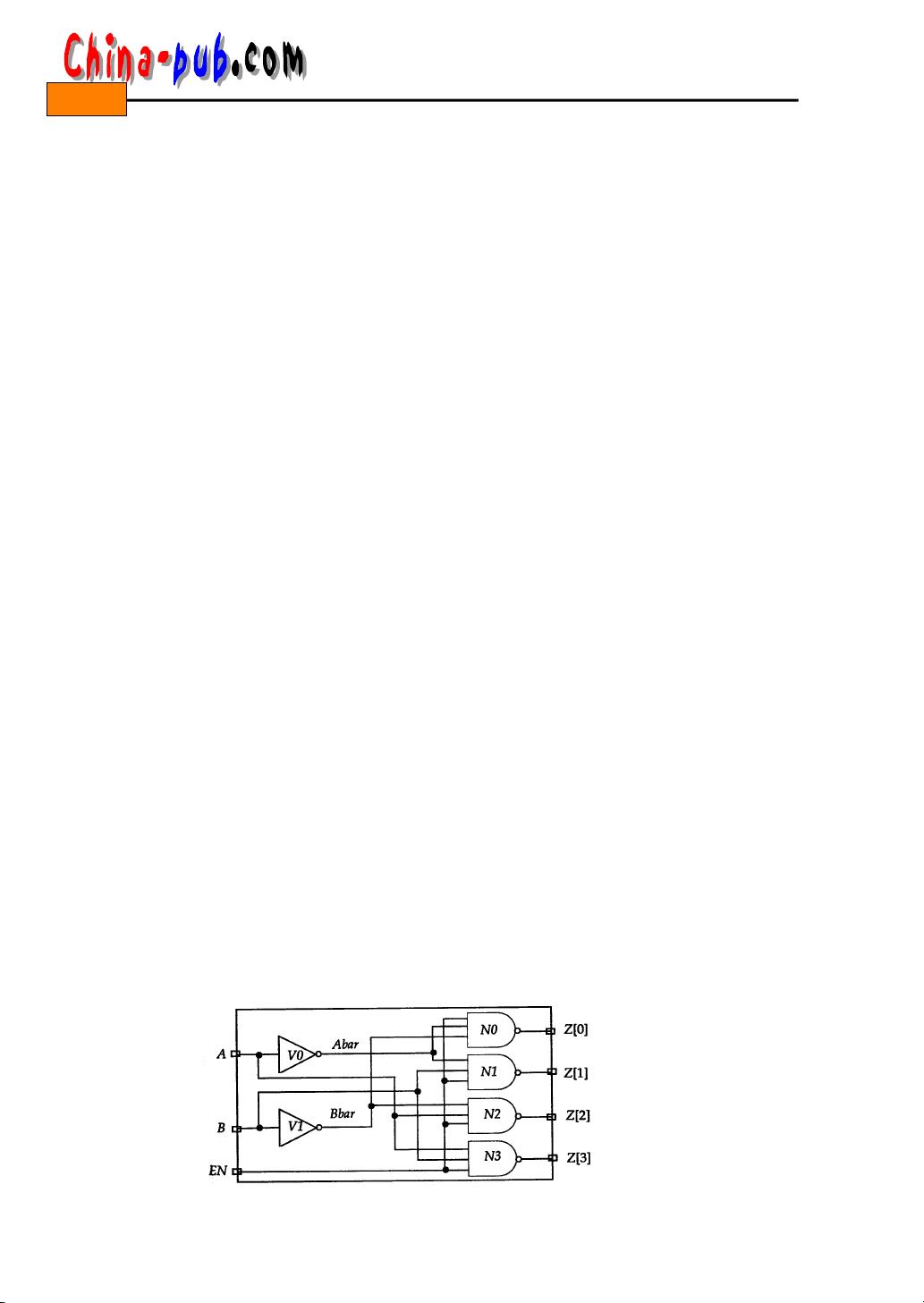

Verilog是一种用于电子系统级设计的硬件描述语言(HDL),广泛应用于FPGA(现场可编程门阵列)和ASIC(应用特定集成电路)设计。Verilog可以用来对数字电路进行建模、模拟和综合。Verilog语言在1983年由Gateway Design Automation公司推出,1990年由Open Verilog International(OVI)接手管理,1995年被IEEE标准化为IEEE 1364标准。Verilog是模块化的,使得工程师可以分别对系统各个部分进行建模,并最终组合成完整的系统。 在Verilog中,有几个基本的构造块,它们分别是模块(module)、端口(port)、声明(declarations)和语句(statements)。模块是Verilog中的基本构建单元,它包含输入、输出、内部信号声明以及行为描述。端口列表定义了模块的接口。声明部分用于定义信号类型,如寄存器(reg)、连线(wire)、参数(parameter)等。语句部分包括初始块(initial block)和始终块(always block),它们用于描述硬件的行为。 在Verilog中,寄存器(reg)用于建模触发器和存储元件,而连线(wire)用于建模组合逻辑的信号。initial块用于仿真中的初始化和调试,而always块用来描述硬件行为,它会在敏感信号列表中的信号变化时触发。 为了提供时间延迟,Verilog提供了时间尺度声明(`timescale directive),这可以定义时间单位和时间精度,例如`timescale 1ns / 100ps表示时间单位是1纳秒,时间精度是100皮秒。 在给出的内容中,可以看到几个基本的Verilog构建的例子,例如组合逻辑的全加器(FA_Seq)和半加器(HalfAdder),以及组合逻辑的解码器(Decoder2x4)。在全加器的例子中,定义了输入A、B和进位Cin以及输出Sum和进位Cout。它使用了always块来描述全加器的行为。在半加器的例子中,则使用assign语句和延时来描述加法器的行为。 对于组合逻辑解码器(Decoder2x4),输入包括两个地址位A、B和使能信号EN,输出为4位向量Z。每个输出位都是通过一系列的assign语句以及逻辑运算得到的结果,并且可以配合延时来模拟硬件延迟。 仿真测试模块(Test)则是为了验证其他模块的功能而设计的,可以在仿真环境中测试不同模块的性能和功能。 Verilog还包括了用户定义的原语(UDP),它们是用户可以定义的逻辑功能块,以及模块实例化(module instantiation),允许设计者实例化模块作为更大电路的一部分。 Verilog具有描述数字电路的强大功能,并为FPGA和ASIC的设计提供了灵活性和效率。从基础语法到模块化设计,Verilog为数字设计人员提供了一个强大的工具集,以实现复杂的硬件设计和仿真。通过理解和掌握Verilog的语法,可以有效地进行硬件描述、设计验证、以及最终的硬件实现。

剩余171页未读,继续阅读

- 粉丝: 0

- 资源: 2

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功