Verilog HDL语言语法大全

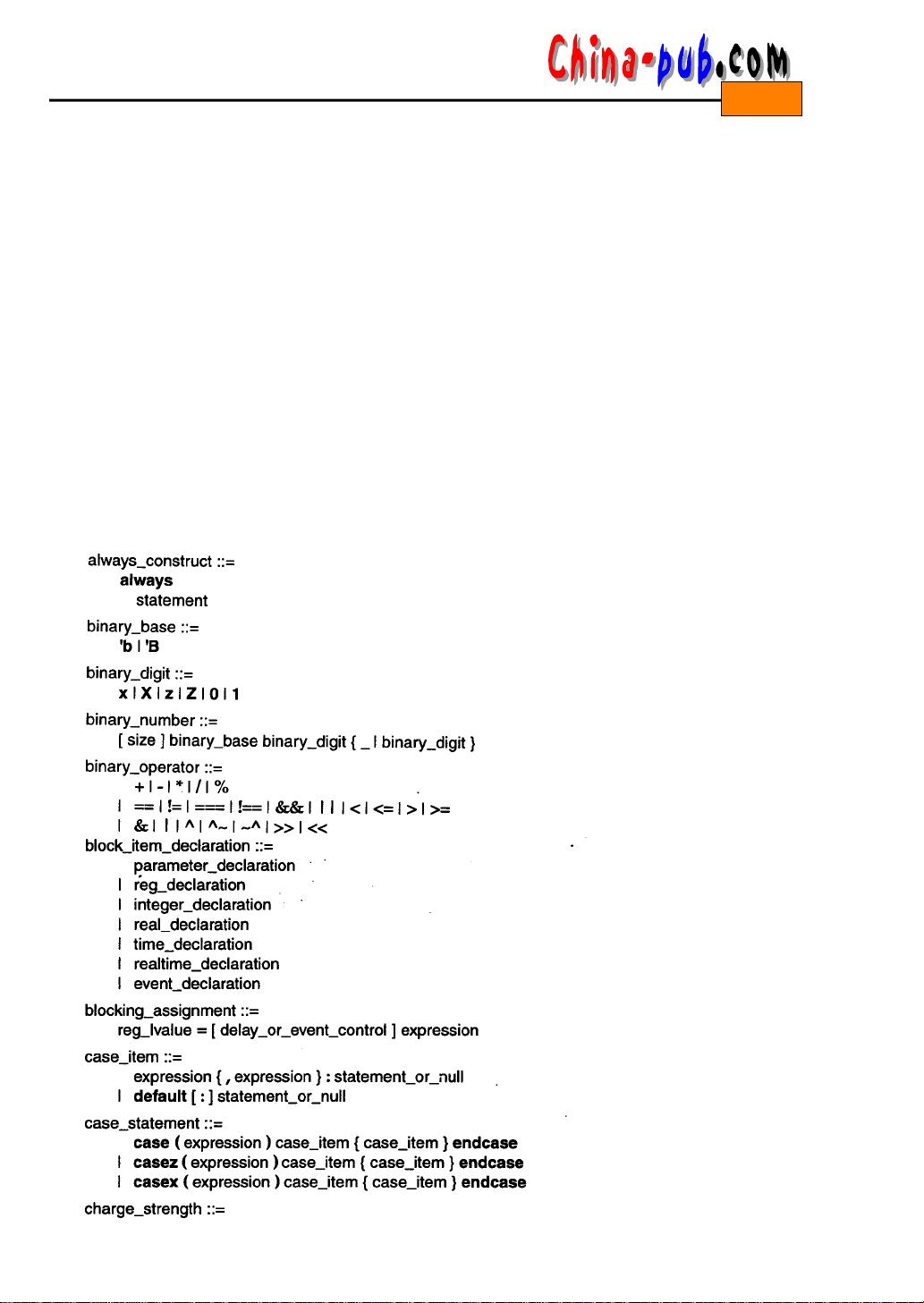

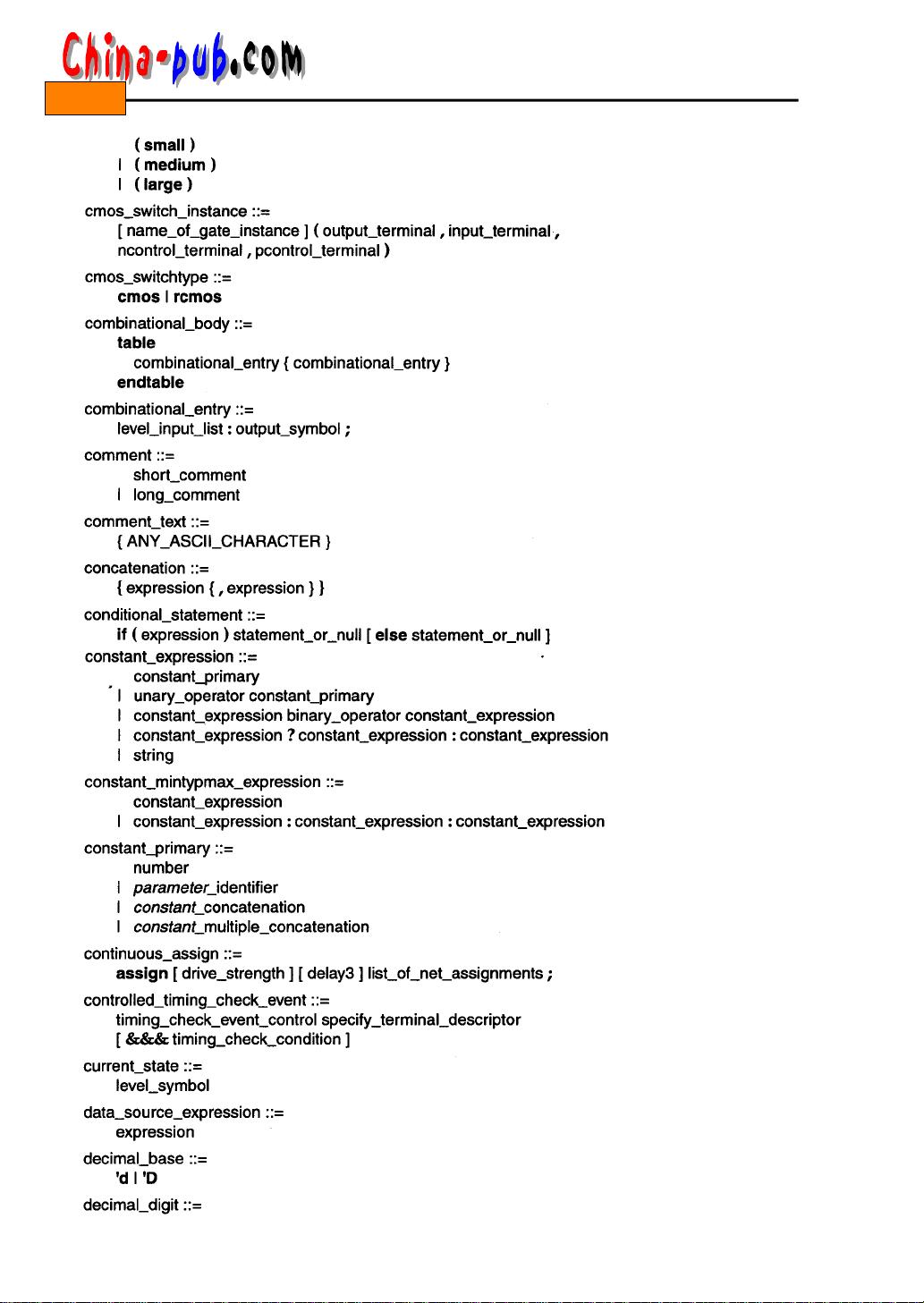

Verilog HDL是一种广泛使用的硬件描述语言,用于设计和建模数字系统,包括集成电路和嵌入式系统。本文档提供了一份全面的Verilog HDL语言语法大全,对初学者而言是一份宝贵的参考资料。 Verilog HDL的关键字是语言的基础,它们包括`always`、`and`、`assign`、`begin`、`buf`、`bufif0`、`bufif1`等多个关键字。这些关键字在编写Verilog代码时有着特定的含义和用途。例如,`always`块用于定义行为级的连续赋值或时序逻辑,`and`代表逻辑与操作,`assign`用于静态赋值,`buf`是一个单输入缓冲器,`bufif0`和`bufif1`则是条件缓冲器,根据条件决定是否执行缓冲功能。 语法规范遵循巴科斯—诺尔范式(BNF),这是一套用于定义上下文无关文法的形式化方法。规则中的非终结符和终结符通过特定的符号进行区分。例如,非终结符通常表示一个结构或概念,而终结符是基本的、不可分解的语言元素,如关键字、标识符、运算符和分隔符。非终结符前的斜体名字与其语义相关,垂直线(|)用于分隔可能的选项,方括号([ . . . ])表示可选项,大括号({ . . . })表示可重复0次或多次的元素。 在Verilog HDL中,设计可以被描述为模块,模块通过端口进行连接,可以包含变量声明、任务和函数定义、连续赋值、过程语句(如`always`块)以及结构体(如`case`语句)。例如,`module`关键字用于定义一个新的模块,`input`和`output`用来声明输入和输出端口,`reg`和`wire`分别用于声明寄存器型和线网型变量。 `case`语句用于多路选择,它可以是`case`、`casez`或`casex`,分别对应于全匹配、零或X匹配和任意值匹配。`if`和`else`语句则用于条件分支,`for`循环可用于迭代操作。`function`和`task`则允许定义自定义的操作或流程。 此外,Verilog支持各种数据类型,如`integer`、`real`、`realtime`、`time`等,它们在处理数值计算和时间操作时非常有用。还有布尔类型的`logic`、`bit`,以及各种强度指示器,如`strong0`、`strong1`、`weak0`、`weak1`,用于描述信号的驱动能力。 在时序控制方面,Verilog有`posedge`和`negedge`来检测信号边沿,`always @(posedge clk)`这样的语句会在时钟上升沿触发事件。`event`和`disable`则用于事件管理和控制。 `parameter`用于定义模块参数,允许在编译时进行参数化。`generate`语句则用于生成结构体的实例,根据参数或条件创建多个相同的模块实例。 Verilog HDL的语法非常丰富,涵盖了许多硬件设计的各个方面。这份语法大全不仅包含了所有的关键字,还提供了文法规则的详细解释,对于理解和学习Verilog HDL至关重要。通过深入学习和实践,设计师能够利用Verilog HDL高效地描述和验证复杂的数字系统。

剩余15页未读,继续阅读

- 粉丝: 1

- 资源: 3

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- AI绘画工具介绍(文档)

- pandas-2.2.2-cp311-cp311-musllinux-1-1-aarch64.whl

- 小程序开发基础与简单示例.pdf

- matlab:读取图像+显示图像+显示图像的直方图+直方图均衡

- pandas-2.2.2-cp311-cp311-manylinux-2-17-x86-64.manylinux2014.whl

- 如何充分运用ansys的HELP

- pandas-2.2.2-cp311-cp311-musllinux-1-1-x86-64.whl

- C语言可变长数组(VLA)详解与应用

- android-studio-2024.1.1.12-windows-zip.zip.001

- 辰光PHP客服系统多商户全开源V3.1版+安装教程

信息提交成功

信息提交成功

- 1

- 2

前往页