没有合适的资源?快使用搜索试试~ 我知道了~

SH1126驱动芯片规格书所能支持的最大分辨率为384*96以及16灰度级参数,增加型384*96*4bits的SRAM,支持8bits 6800-series parallel interface, 8bits 8080-series parallel interface, 3 wire/4 wire serial peripheral interface, 400KHZ fast I 2 C bus interface等等5种接口方式,以及各种寄存器的操作使用,大家学习研究可以参考一下。

资源推荐

资源详情

资源评论

SH1126

384 X 96 16 Grayscale

Preliminary Dot Matrix OLED/PLED Driver with Controller

1 V1.0

Features

n Support maximum 384 X 96 dot matrix panel with 16

grayscale

n Embedded 384 X 96 X 4bits SRAM

n Operating voltage:

- I/O voltage supply: VDD1 = 1.65V - 3.5V

- Logic voltage supply: VDD2 = 1.65V - 3.5V

VDD1 = VDD2

- DC-DC voltage supply: AVDD = 2.4V - 3.5V

- OLED Operating voltage supply: VPP = 7.0V -14V

n Maximum segment output current: 500mA

n Maximum common sink current: 192mA

n 8-bit 6800-series parallel interface, 8-bit 8080-series

parallel interface, 3 wire/4 wire serial peripheral interface

n 400KHZ fast I

2

C bus interface

n Programmable frame frequency and multiplexing ratio

n Row re-mapping and column re-mapping (ADC)

n Vertical scrolling

n On-chip oscillator

n Available internal DC-DC converter

n 256-step contrast control on monochrome passive OLED

panel

n Low power consumption

- Sleep mode: < 5mA

n Wide range of operating temperatures: -40 to +85°C

n Available in COG form

General Description

SH1126 is a single-chip CMOS OLED/PLED driver with controller for organic/polymer light emitting diode dot-matrix graphic

display system. SH1126 consists of 384 segments, 96 commons with 16 grayscale that can support a maximum display

resolution of 384 X 96. It is designed for Common Cathode type OLED panel.

SH1126 embeds with contrast control, display RAM oscillator and efficient DC-DC converter, which reduces the number of

external components and power consumption. SH1126 is suitable for a wide range of compact portable applications, such as

car audio, and calculator, etc.

SH1126

2

Block Diagram

I/O buffer circuit

Line address decoder

Initial display line

register

Line counter

Figure 1 SH1126 Block Diagram

SH1126

3

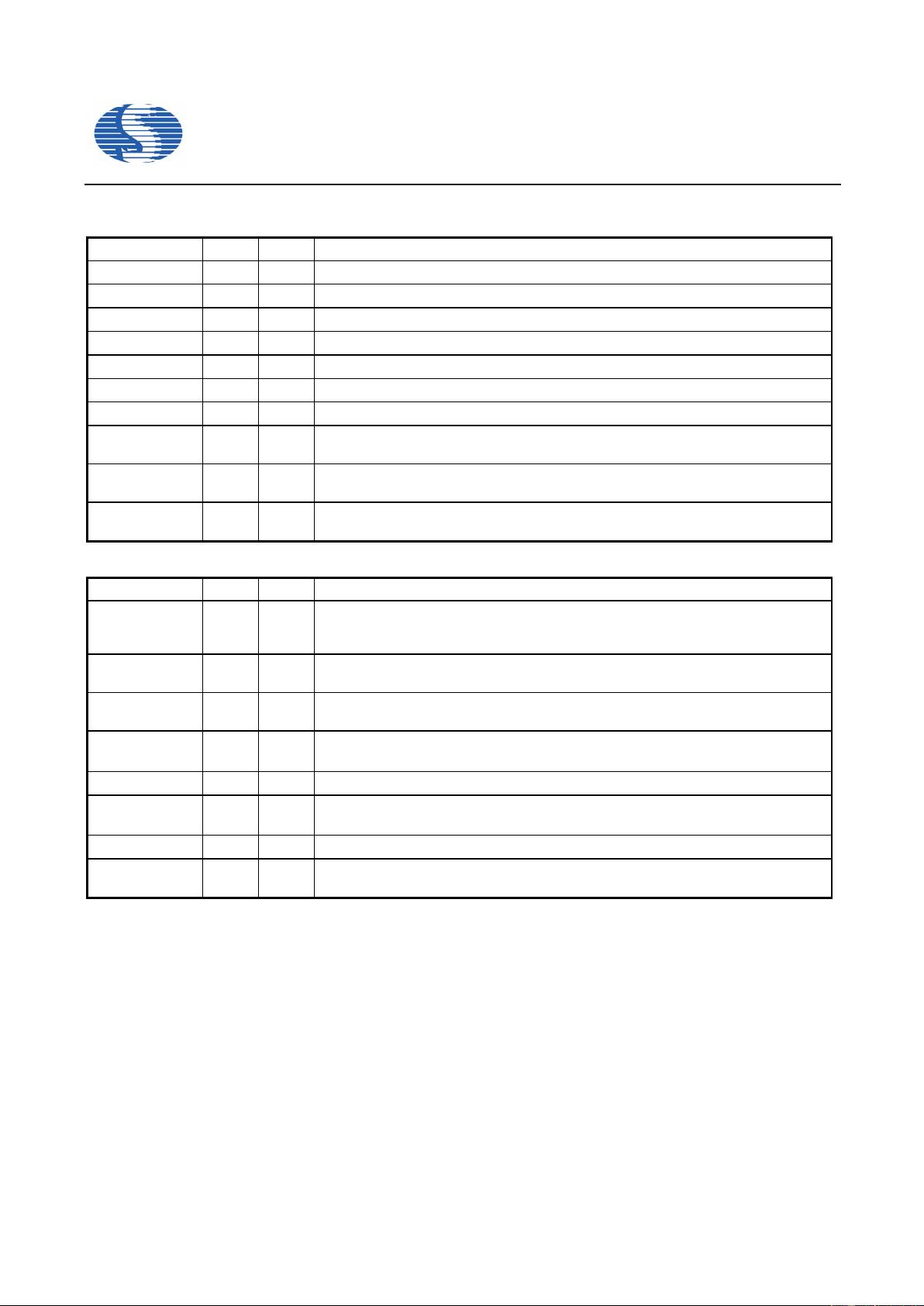

Pad Description

Power Supply

Pad No. Symbol

I/O Description

71,72 VDD2

Supply

1.65 - 3.5V power supply input pad for logic

78,79 VDD1

Supply

1.65 - 3.5V power supply input pad

74 VDD1

Supply

1.65 - 3.5V power supply output for pad option

66,67 AVDD

Supply

2.4 - 3.5V power supply pad for the internal buffer of the DC-DC voltage converter

54 VSSA

Supply

Ground for VSL.

55~57 VSS Supply

Ground for analog, logic&buffer respectively.

76,81 VSS Supply

Ground output for pad option

16~19,50~53,

100~103

VPP Supply

This is the most positive voltage supply pad of the chip

It should be supplied externally

40~42 VSL Supply

This is a segment voltage reference pad

A capacitor should be connected between this pad and VSS

58~64 VCL Supply

This is a common voltage reference pad

This pad should be connected to VSS externally

OLED Driver Supplies

Pad No. Symbol

I/O Description

43,44 VREF

I

This is a voltage reference pad for pre-charge voltage in driving OLED device.

Voltage should be set to match with th

e OLED driving voltage in current drive

phase. It can either be supplied externally or by connecting to VPP.

48,49 IREF O

This is a segment current reference pad

A resistor should be connected between this pad and VSS. Set the current at 15.625m

A

37~39 VCOMH

O

This is a pad for the voltage output high level for common signals

A capacitor should be connected between this pad and VSS

34~36 VSEGM

O

This is a pad for the voltage output level for segment pre-charge.

A capacitor should be connected between this pad and VSS.

70 SW O This is an output pad driving the gate of the external NMOS of the booster circuit

68 FB I

This is a feedback resistor input pad for the booster circuit

It is used to adjust the booster output voltage level, VPP

65 SENSE

I This is a source current pad of the external NMOS of the booster circuit

69 VBREF

O This is an internal voltage reference pad for booster circuit

SH1126

4

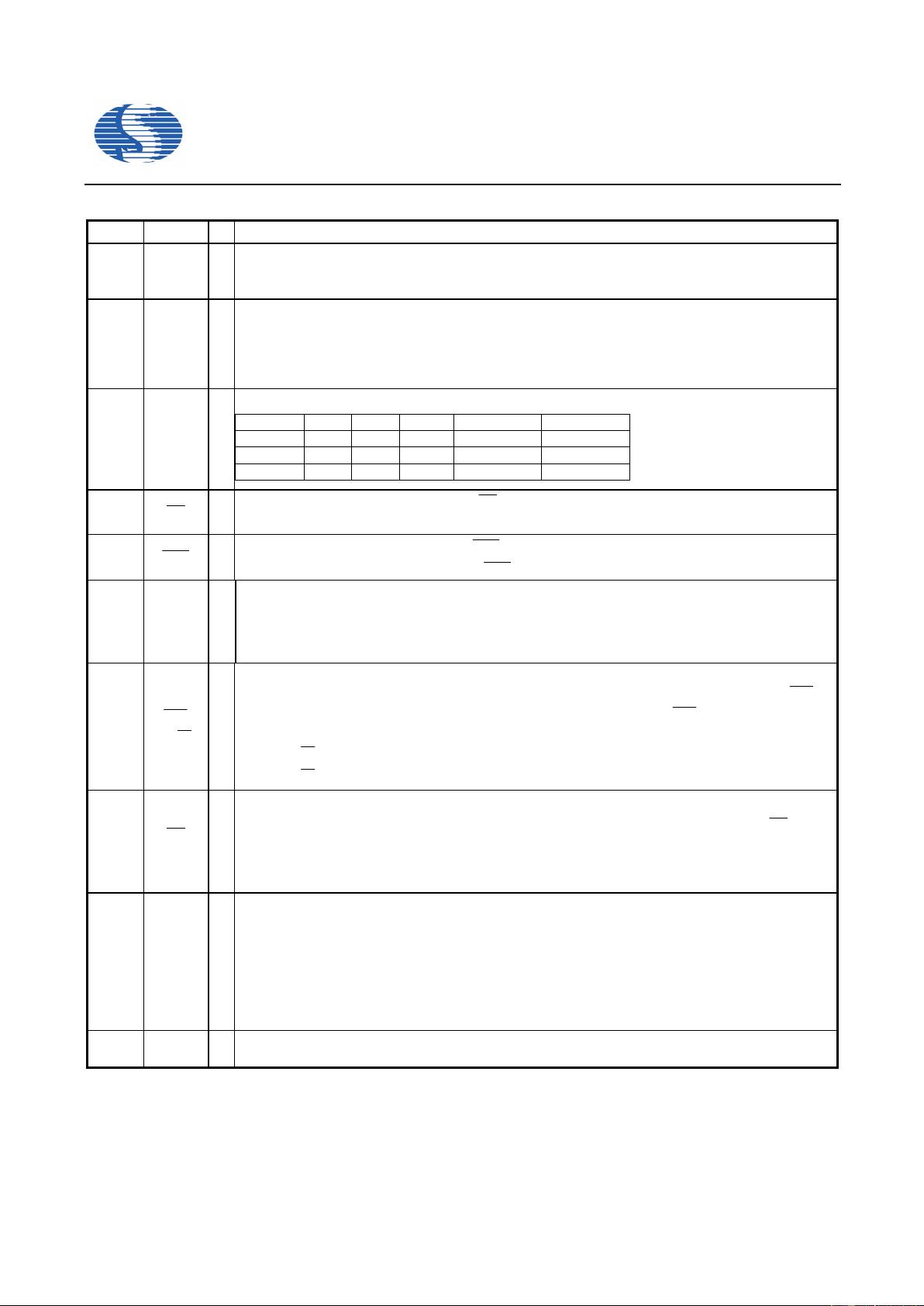

System Bus Connection Pads

Pad No.

Symbol

I/O

Description

87 CL I/O

This pad is the system clock input. When internal clock is enabled, this pad should be Left open.

The internal clock is output from this pad. When internal oscillator is disabled,

this pad receives display clock signal from external clock source.

73 CLS I

This is the internal clock enable pad.

CLS = “H”: Internal oscillator circuit is enabled.

CLS = “L”: Internal oscillator circuit is disabled (requires external input).

When CLS = “L”, an external clock source must be connected to the CL pad for normal operation.

75

77

80

IM0

IM1

IM2

I

These are the MPU interface mode select pads.

8080

I

2

C 6800 4-wire SPI 3-wire SPI

IM0 0 0 0 0 1

IM1 1 1 0 0 0

IM2 1 0 1 0 0

82

CS

I

This pad is the chip select input. When

CS

= “L”, then the chip select becomes active,

and data/command I/O is enabled.

83

RES

I

This is a reset signal input pad. When

RES

is set to “L”, the settings are initialized.

The reset operation is performed by the

RES

signal level.

84

A0

(SA0)

I

This is the Data/Command control pad that determines whether the data bits are a data or a

command.

A0 = “H”: the inputs at D0 to D7 are treated as display data.

A0 = “L”: the inputs at D0 to D7 are transferred to the command registers.

In I

2

C interface, this pad serves as SA0 to distinguish the different address of OLED driver.

85

WR

(

WR/

)

I

This is a MPU interface input pad.

When connected to an 8080 MPU, this is active LOW. This pad connects to the 8080 MPU

WR

signal. The signals on the data bus are latched at the rising edge of the

WR

signal.

When connected to a 6800 Series MPU: This is the read/write control signal input terminal.

When

WR/

= “H”: Read.

When

WR/

= “L”: Write.

86

RD

(E)

I

This is a MPU interface input pad.

When connected to an 8080 series MPU, it is active LOW. This pad is connected to the

RD

signal

of the 8080 series MPU, and the SH1126 data bus is in an output status when this signal is “L”.

When connected to a 6800 series MPU, this is active HIGH. This is used as an enable clock input

of the 6800 series MPU.

92~99

D0 - D7

(SCL)

(SI /SDA)

I/O

I

I

This is an 8-bit bi-directional data bus that connects to an 8-bit or 16-bit standard MPU data bus.

When the serial interface is selected, then D0 serves as the serial clock input pad (SCL) and

D1serves as the serial data input pad (SI). At this time, D2 to D7 are set to high impedance.

When the I2C interface is selected, then D0 serves as the serial clock input pad (SCL) and D1

serves as the serial data input pad (SDA). At this time, D2 to D7 are set to high impedance.

When the chip select is inactive, D0 to D7 are set to high impedance.

91 FRM O

This pad is No Connection pad. Its signal varies with the frame frequency. Its voltage is equal to

VDD1 when the last common output of every frame is active, and is equal to VSS

during other time.

SH1126

5

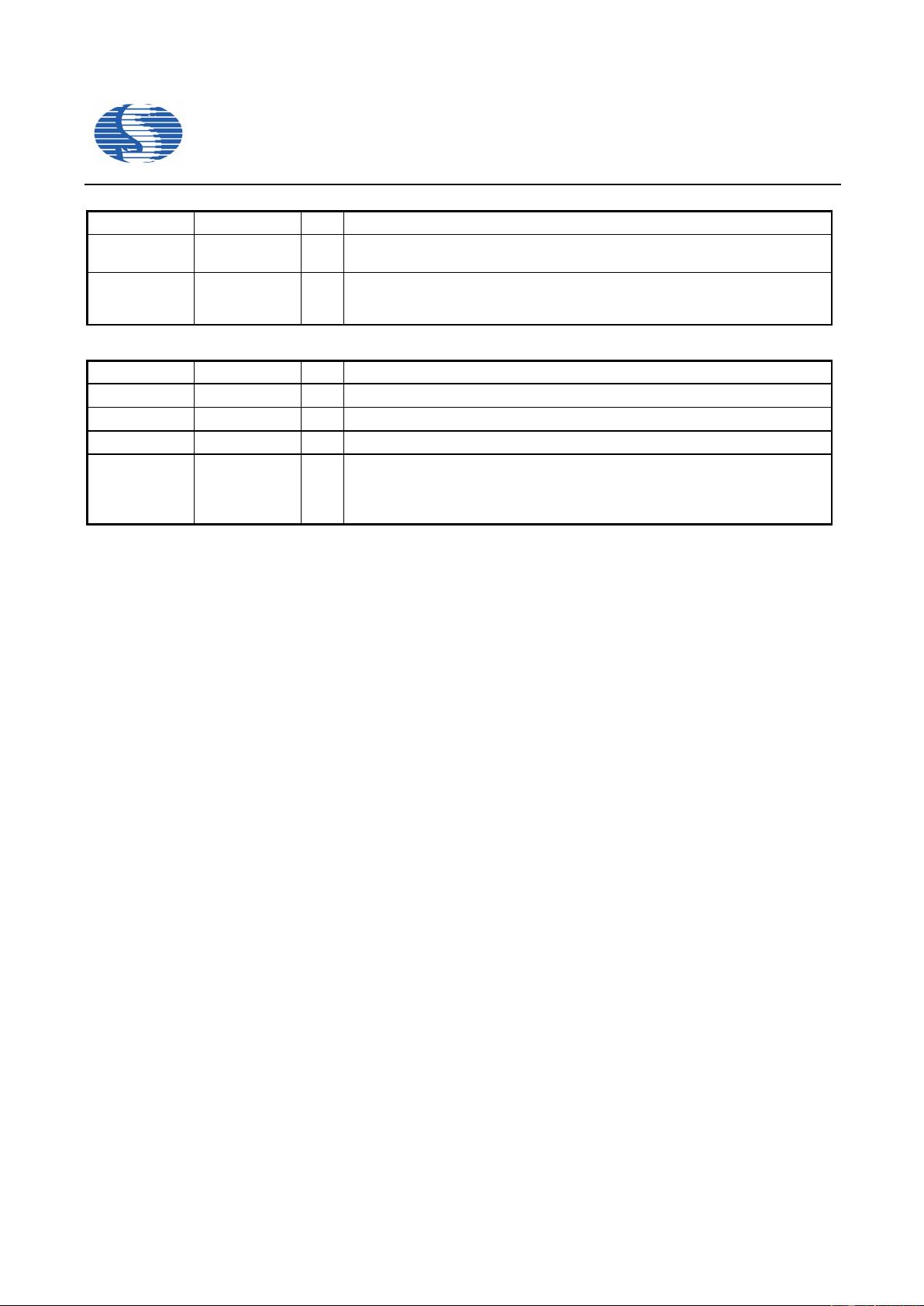

OLED Drive Pads

Pad No. Symbol I/O

Description

313~408 COM0 – 95 O These pads are Common signal output for OLED display.

120~311,

601~410

SEG0 – 383 O These pads are Segment signal output for OLED display.

Test Pads

Pad No. Symbol I/O

Description

88 TEST1 I Test pads, internal pull low, no connection for user.

89 TEST2 O Test pads, no connection for user.

90 TEST3 I Test pads, no connection for user.

1~15,20~33,45~

47,104~119,312,

409,602

Dummy - NC pads, no connection for user.

剩余50页未读,继续阅读

资源评论

create_jiang@

- 粉丝: 2

- 资源: 11

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功