A

B

C

D

E

4 4

3 3

2 2

1 1

Title

Size Document Number Rev

Date: Sheet

of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Homa

-1

Reference

A3

257Thursday, April 03, 2008

970

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Homa

-1

Reference

A3

257Thursday, April 03, 2008

970

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Homa

-1

Reference

A3

257Thursday, April 03, 2008

970

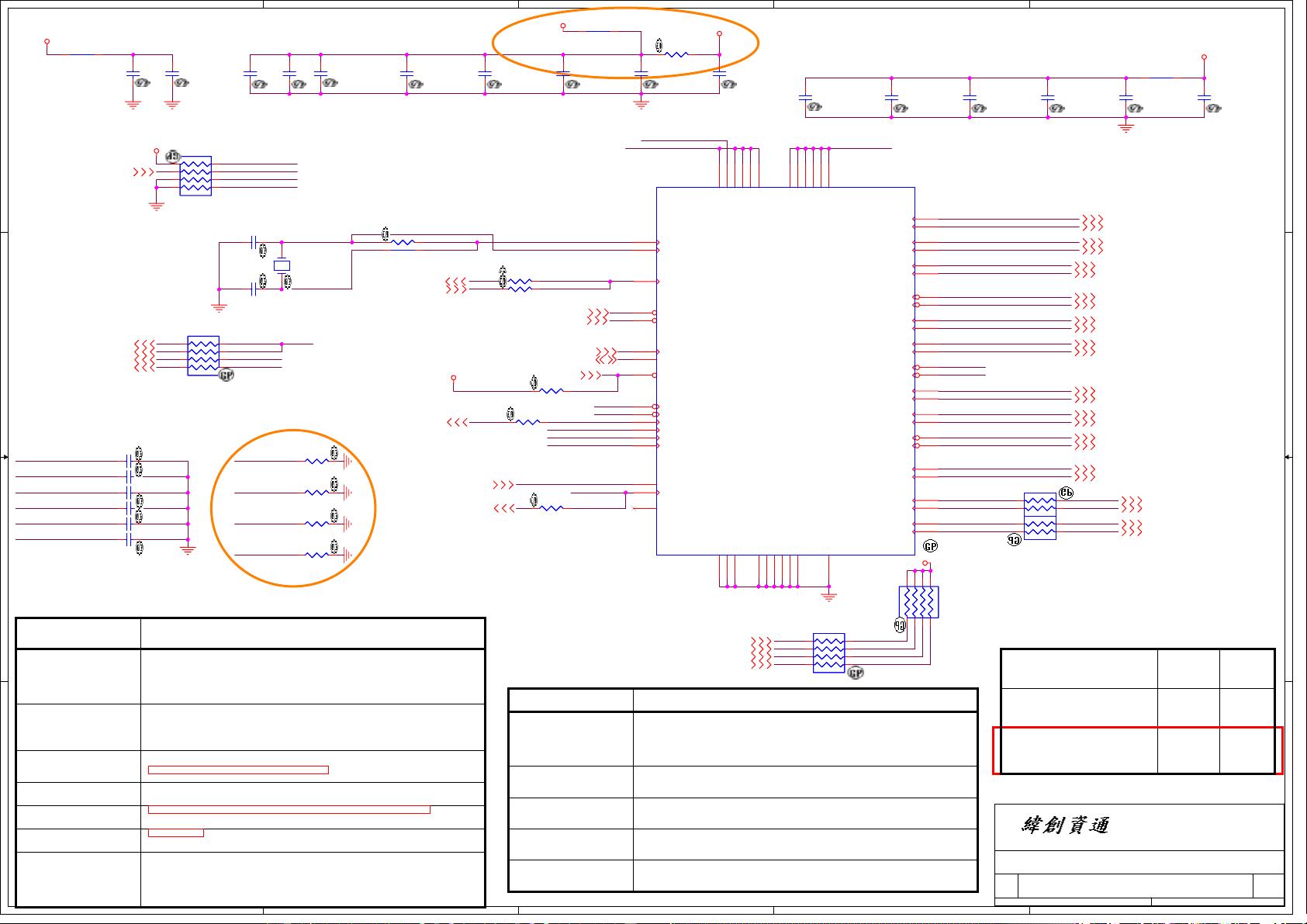

1 = TLS cipher suite with

confidentiality (default)

0 = Transport Layer Security (TLS) cipher

suite with no confidentiality

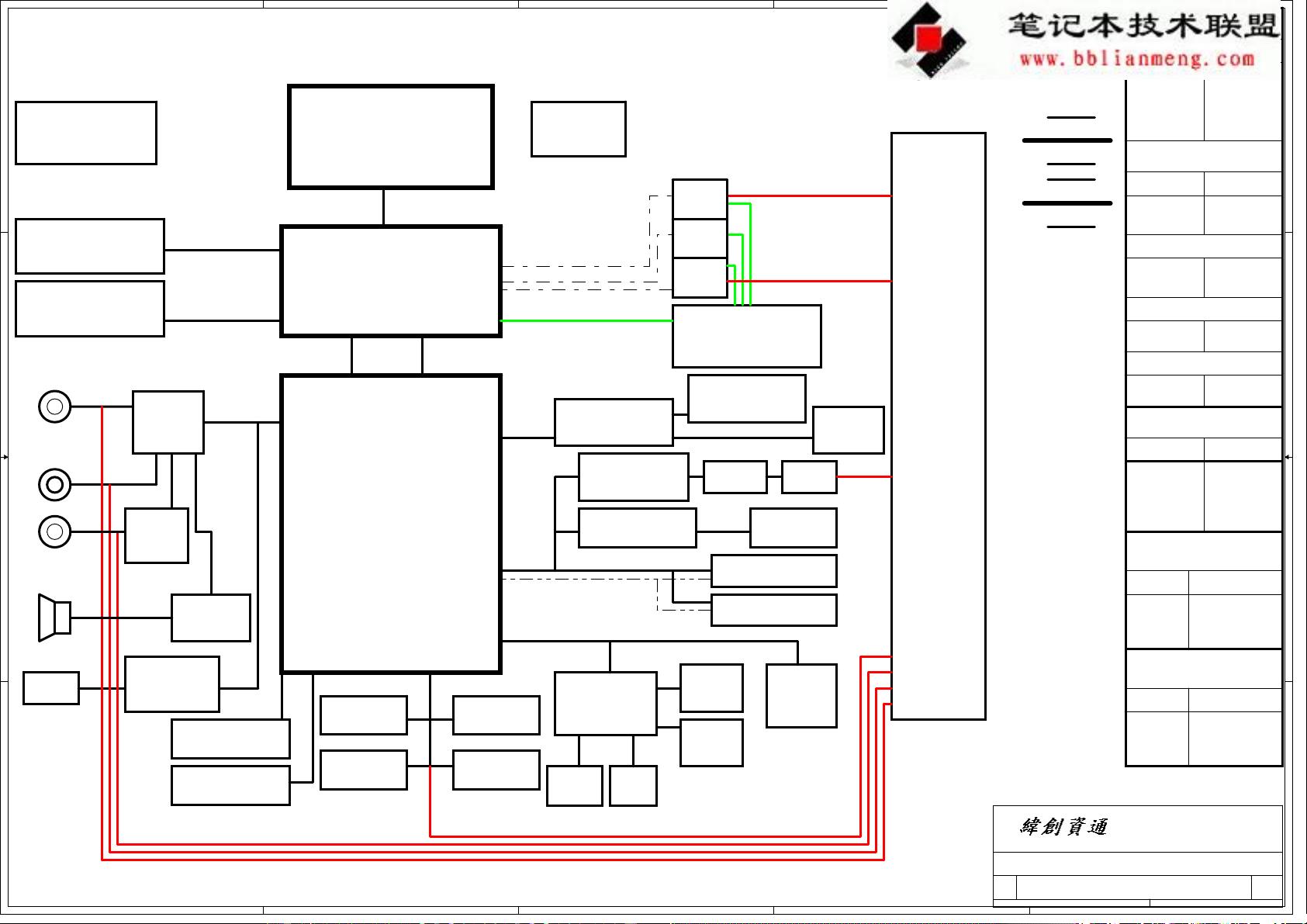

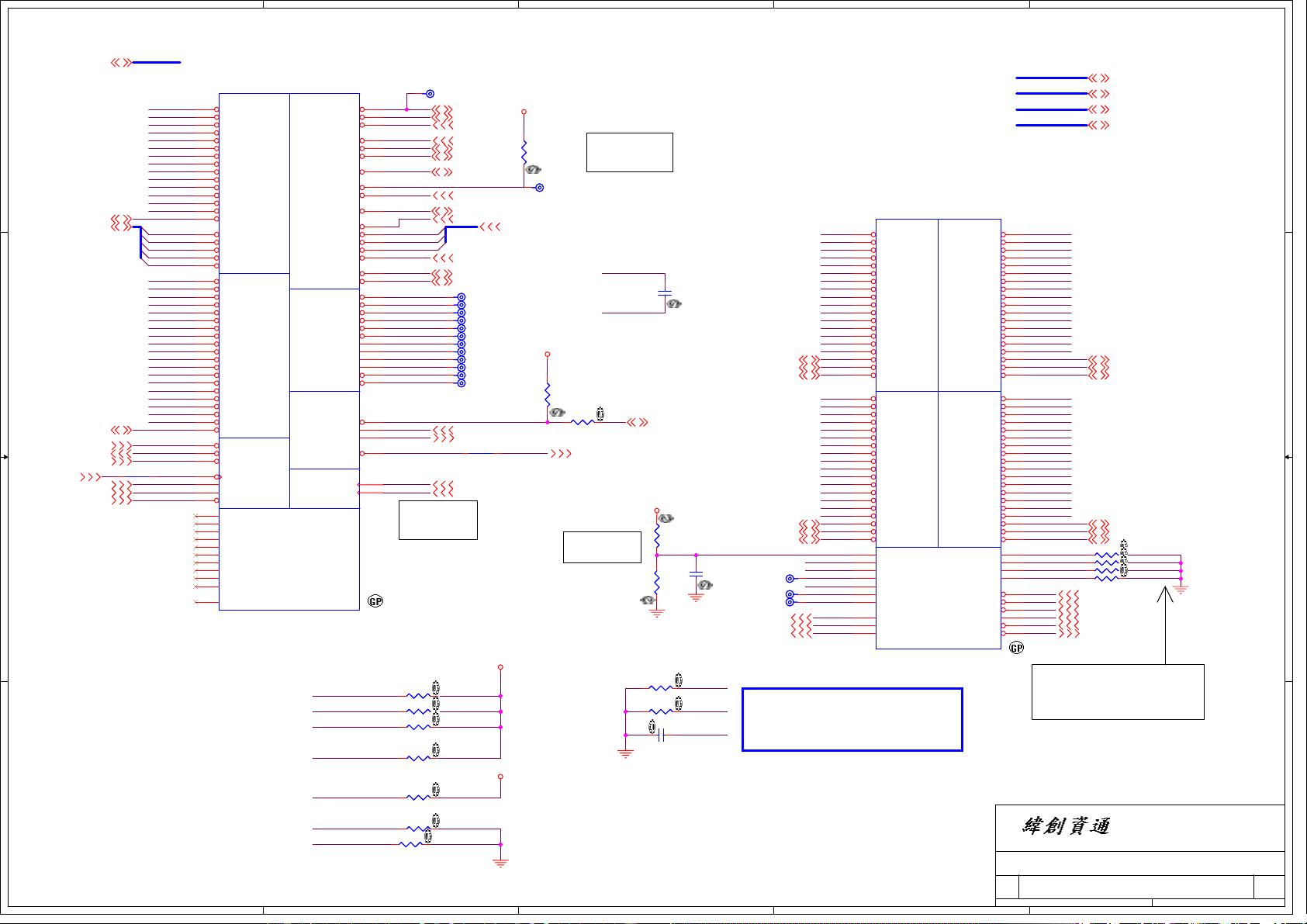

Cantiga chipset and ICH9M I/O controller

Hub strapping configuration

page 218

Intel Management

engine Crypto strap

CFG6

Reserved, Rising Edge

of PWROK.

This signal has a weak internal pull-down.

This signal should not be pulled high.

GPIO49

SPI_MOSI

GPIO33/

HDA_DOCK

_EN#

SATALED#

SPKR

TP3

CFG9

(Default)

CFG16

0 = LFP Disabled (Default)

Local Flat Panel

(LFP) Present

CFG19

CFG20

SDVO_CTRLDATA

1 = Dynamic ODT Enabled

0 = Dynamic ODT Disabled

1= LFP Card Present; PCIE disabled

L_DDC_DATA

FSB Dynamic ODT

DMI Lane Reversal

NOTE:

PCIE config2 bit2,

Rising Edge of PWROK.

GNT2#/

GPIO53

Sets bit0 of RPC.PC(Config Registers:Offset 224h)

Top-Block

Swap Override.

Rising Edge of PWROK.

GNT0#:

SPI_CS1#/

GPIO58

0 = Reverse Lanes,15->0,14->1 ect..

Boot BIOS Destination

Selection 0:1.

Rising Edge of PWROK.

Tying this strap low configures DMI for ESI-

compatible operation. This signal has a weak

internal pull up. ESI compatible mode is for

server platforms only.This signal should not

be pulled low for desttop and mobile.

HDA_SDOUT

HDA_SYNC

GNT3#/

GPIO55

Signal

Sampled low:Top-Block Swap mode(inverts A16 for

all cycles targeting FWH BIOS space).

Note: Software will not be able to clear the

Top-Swap bit until the system is rebooted

without GNT3# being pulled down.

This signal has a weak internal pull-up.

XOR Chain Entrance/

PCIE Port Config 1bit1,

Rising Edge of PWROK

1= Normal operation(Default):Lane

Numbered in order

Allows entrance to XOR Chain testing when TP3

pulled low.When TP3 not pulled low at rising edge

of PWROK,sets bit1 of RPC.PC(Config Registers:

offset 224h). This signal has weak internal pull-down

PCIE config 1 bit 0,

Rising Edge of PWROK.

GPIO20

Usage/When Sampled

ESI Strap (Server Only)

Rising Edge of PWROK

Comment

0 = Only Digital Display Port

or PCIE is operational (Default)

1 =Digital display Port and PCIe are

operting simulataneously via the PEG port

0 =No SDVO Card Present (Default)

1 = SDVO Card Present

page 31

DMI Termination Voltage,

Rising Edge of PWROK.

The signal is required to be low for desktop

applications and required to be high for

mobile applications.

Signal has weak internal pull-up. Sets bit 27

of MPC.LR(Device 28:Function 0:Offset D8)

CFG[2:0]

CFG[4:3]

CFG8

CFG[15:14]

CFG[18:17]

CFG5

Pin Name

011 = FSB667

FSB Frequency

Select

0 = DMI x2

others = Reserved

Reserved

(Default)

1 = DMI x4

Strap Description

DMI x2 Select

iTPM Host

Interface

Configuration

Sets bit2 of RPC.PC2(Config Registers:Offset 0224h)

This signal has a weak internal pull-down.

GNT1#/

GPIO51

Integrated TPM Enable,

Rising Edge of CLPWROK

Sample low: the Integrated TPM will be disabled.

Sample high: the MCH TPM enable strap is sampled

low and the TPM Disable bit is clear, the

Integrated TPM will be enable.

Flash Descriptor

Security Override Strap

Rising Edge of PWROK

PCI Express Lane

Reversal. Rising Edge

of PWROK.

No Reboot.

Rising Edge of PWROK.

XOR Chain Entrance.

Rising Edge of PWROK.

This signal should not be pull low unless using

XOR Chain testing. It has a weak internal pull up.

If sampled high, the system is strapped to the

"No Reboot" mode(ICH9 will disable the TCO Timer

system reboot feature). The status is readable

via the NO REBOOT bit.

ICH9M Functional Strap Definitions

Controllable via Boot BIOS Destination bit

(Config Registers:Offset 3410h:bit 11:10).

GNT0# is MSB, 01-SPI, 10-PCI, 11-LPC.

page 92

PCI Routing

Sampled low:the Flash Descriptor Security will be

overridden. If high,the security measures will be

in effect.This should only be enabled in manufacturing

environments using an external pull-up resister.

SDVO Present

Montevina Platform Design guide 22339 0.5

LAN BCM5764MKMLG

USB Table

0 0AD25RTS5158

INT REQ

G:CARDBUS

GNTIDSEL

LANE2

LANE1

MiniCard WLAN

PCIE Routing

010 = FSB800

000 = FSB1066

LANE3 MiniCard Roboson

ICH9 EDS 642879 Rev.1.5

ICH9M

BATTERY

KBC

Thermal

MXM

SMBC_G792

BAT_SCL

SMB_CLK

NEW Card

SMBC_ICH

CK505

DDR

CFG7

SMBus

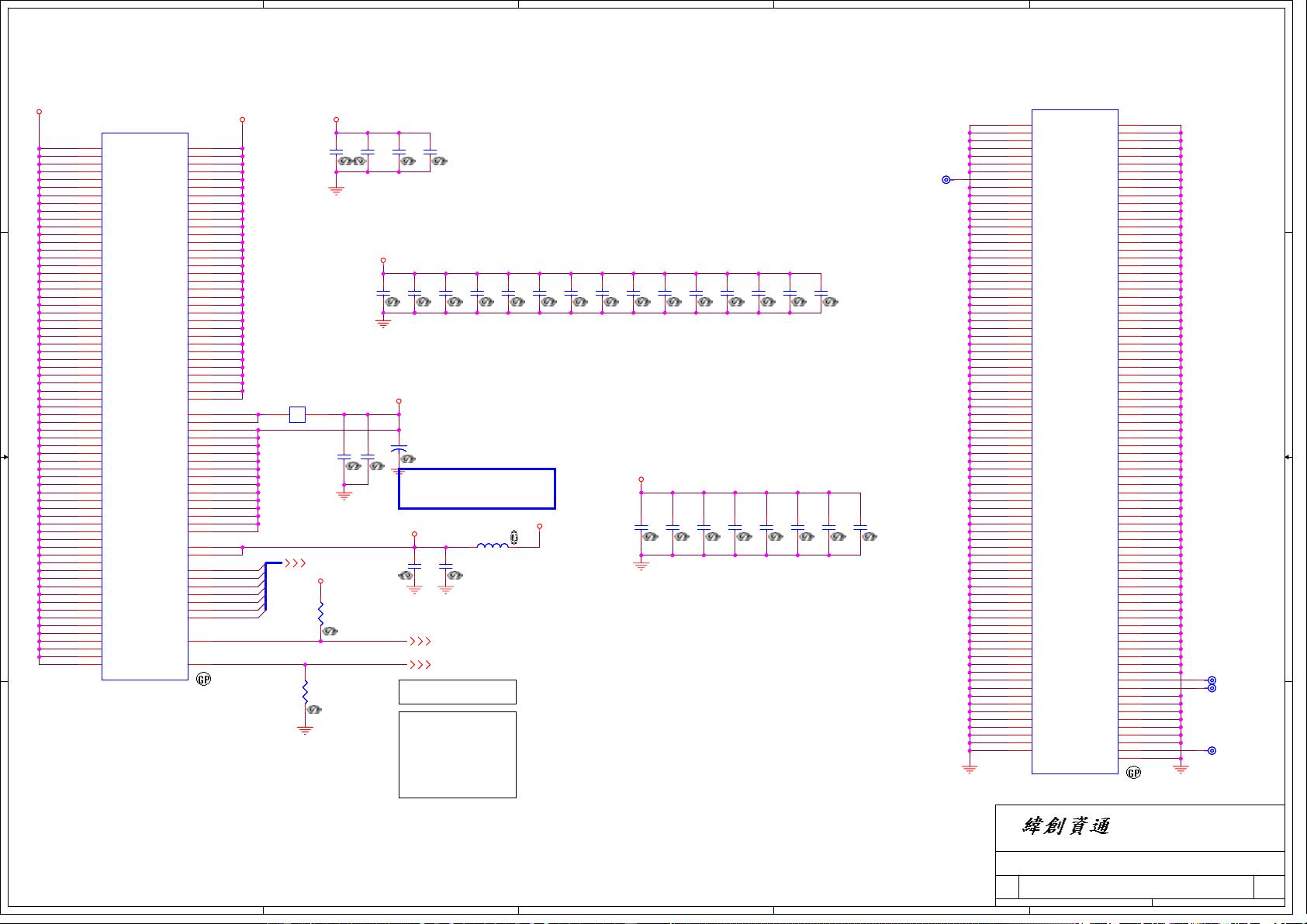

ICH9 EDS 642879 Rev.1.5 page 97

ICH9M Integrated Pull-up

and Pull-down Resistors

SIGNAL Resistor Type/Value

HDA_BIT_CLK

HDA_RST#

HDA_SDIN[3:0]

HDA_SDOUT

HDA_SYNC

GNT[3:0]#/GPIO[55,53,51]

GPIO[20]

LAD[3:0]#/FHW[3:0]#

LDRQ[0]

PME#

PWRBTN#

SATALED#

LAN_RXD[2:0]

LDRQ[1]/GPIO23

TP[3]

SPKR

GLAN_DOCK#

SPI_CS1#/GPIO58/CLGPIO6

USB[11:0][P,N]

CL_RST0#

SPI_MOSI

SPI_MISO

TACH_[3:0]

PULL-DOWN 20K

PULL-DOWN 20K

PULL-DOWN 15K

The pull-up or pull-down active when configured for native

GLAN_DOCK# functionality and determined by LAN controller

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 15K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-DOWN 20K

PULL-DOWN 20K

PULL-DOWN 20K

PULL-DOWN 20K

PULL-DOWN 20K

PULL-DOWN 20K

GPIO[49]

HDA_DOCK_EN#/GPIO33

CL_DATA[1:0]

CL_CLK[1:0]

DPRSLPVR/GPIO16

ENERGY_DETECT

PULL-DOWN 20K

PULL-UP 20K

PULL-UP 10K

PULL-UP 20K

PULL-UP 20K

0= The iTPM Host Interface is enabled(Note2)

1=The iTPM Host Interface is disalbed(default)

PCIE Graphics Lane

CFG10 PCIE Loopback enable

0 = Enable (Note 3)

1= Disabled (default)

1 = Reverse Lanes

DMI x4 mode[MCH -> ICH]:(3->0,2->1,1->2and0->3)

DMI x2 mode[MCH -> ICH]:(3->0,2->1)

0 = Normal operation(Default):

Lane Numbered in Order

Digital Display Port

(SDVO/DP/iHDMI)

Concurrent with PCIe

1. All strap signals are sampled with respect to the leading edge of

the (G)MCH Power OK (PWROK) signal.

2. iTPM can be disabled by a 'Soft-Strap' option in the

Flash-decriptor section of the Firmware. This 'Soft-Strap' is

activated only after enabling iTPM via CFG6.

Only one of the CFG10/CFG/12/CFG13 straps can be enabled at any time.

LANE4 NewCard

USB4

USB2

USB1

USB3

Pair

4

MINIC1

USB

5

0

2

3

1

Device

MINIC2

6

7

8

9 NEW1

Bluetooth

10

11

DOCK USB

FP

NC

WEBCAM

LAN MiniCard

WLAN

MiniCard

Roboson

CFG12 ALLZ

0 = ALLZ mode enabled (Note 3)

1 = Disabled (default)

CFG13 XOR

0 = XOR mode enabled (Note 3)

1 = Disabled (default)

3. Only one of the CFG10/CFG12/CFG13 straps can be enabled at any time.

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功