没有合适的资源?快使用搜索试试~ 我知道了~

MC9S12datesheet数据手册

需积分: 14 4 下载量 170 浏览量

2018-11-18

11:22:31

上传

评论

收藏 10.15MB PDF 举报

温馨提示

试读

797页

飞思卡尔单片机 MC9S12芯片系列 datesheet数据手册 开发技术文档

资源推荐

资源详情

资源评论

S12 MagniV

Microcontrollers

nxp.com

MC9S12ZVC-Family

Reference Manual and

Datasheet

MC9S12ZVCRMV1

Rev. 1.7

13-October-2016

The MC9S12ZVC family of microcontrollers is targeted at use in safety relevant systems and has been developed

using an ISO26262 compliant development system under the NXP Safe Assure Program. For more details of the

NXP Safe Assure program, refer to : NXP Safe Assure

For more details of how to use the device in safety relevant systems refer to the MC9S12ZVC Safety Manual at

nxp.com

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most

current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to

nxp.com/

A full list of family members and options is included in device overview section.

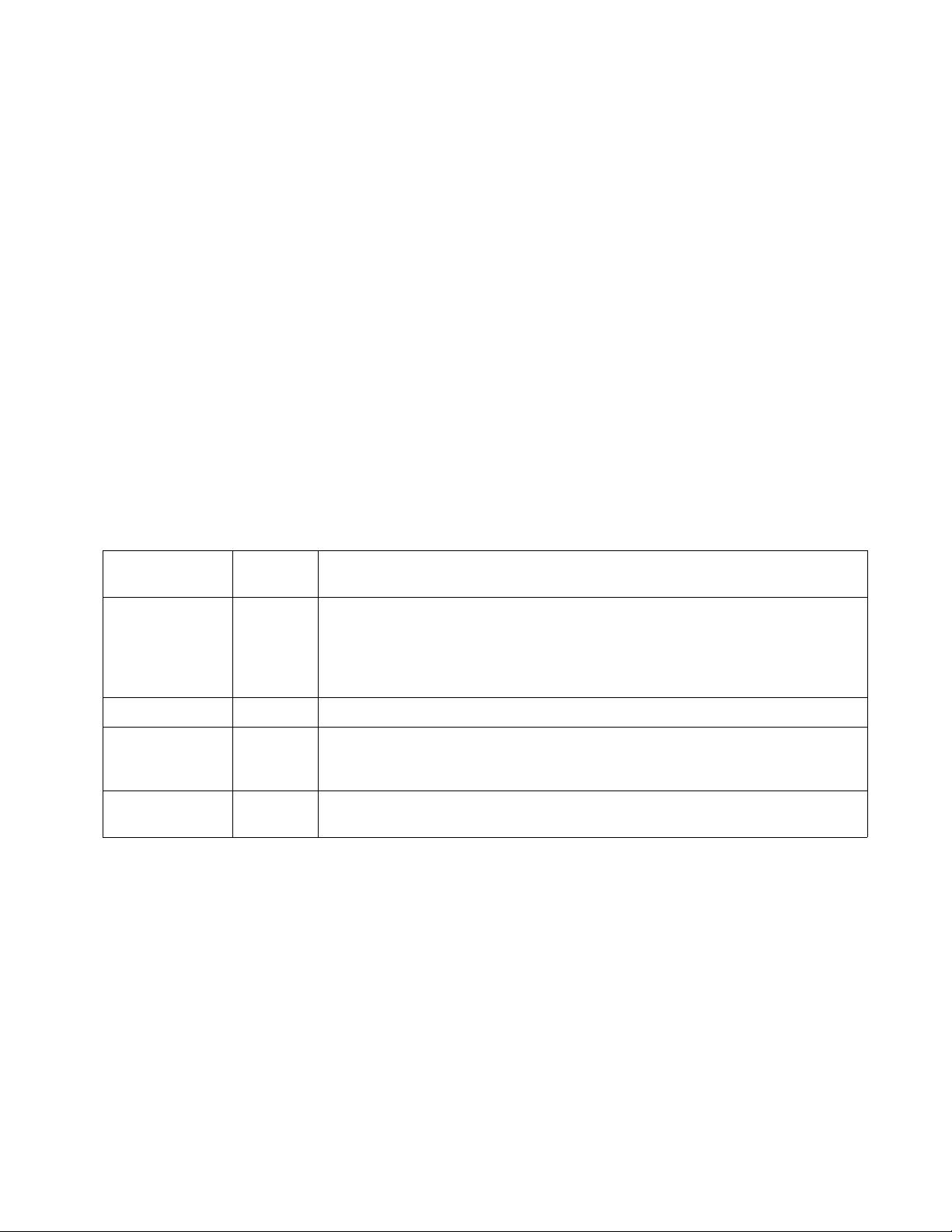

The following revision history table summarizes changes contained in this document.

This document contains information for all constituent modules, with the exception of the S12Z CPU. For S12ZCPU

information please refer to the CPU S12Z Reference Manual.

NXP reserves the right to make changes without further notice to any products herein. NXP makes no warranty, representation or guarantee regarding the suitability of its products

for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including

without limitation consequential or incidental damages. “Typical” parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications

and actual performance may vary over time. All operating parameters, including “Typicals”, must be validated for each customer application by customer’s technical experts. NXP

does not convey any license under its patent rights nor the rights of others. NXP products are not designed, intended, or authorized for use as components in systems intended for

surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the NXP product could create a situation

where personal injury or death may occur. Should Buyer purchase or use NXP products for any such unintended or unauthorized application, Buyer shall indemnify and hold NXP

and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or

indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that NXP was negligent regarding the design or

manufacture of the part.

Revision History

Date

Revision

Level

Description

14-January-2016 Rev 1.4

PAD3 pin 16 in LQFP-48 and pin 20 in LQFP-64 renamed from VRH to VRH_0

Added Note on page 605 with reference to VRH and VRL connectivity

Changed Temperature sensor slope and output voltage Table E-1 item 14 and 15

Added Stop IDD values for 85C and 105C to Table A14

Changed Item 7 R

P_PASS

in Table A-9 to 22ns

8-February-2016 Rev 1.5 Replaced Freescale logo with NXP logo

22-August-2016 Rev 1.6

Added item 18 and 19 Table E-1 Bandgap voltage and temperature dependency

Changed item 5 Table H-2 ACMP input offset

Added operating condition for C part to Table A-5

13-October-2016 Rev 1.7

Corrected Table 1-1 Two SCIs for 48pin packages

Corrected typo in table H-2 item 5

MC9S12ZVC Family Reference Manual , Rev. 1.7

NXP Semiconductors 3

Chapter 1 Device Overview MC9S12ZVC-Family. . . . . . . . . . . . . . . . . . . . . . . . 23

Chapter 2 Port Integration Module (S12ZVCPIMV1) . . . . . . . . . . . . . . . . . . . . 69

Chapter 3 Background Debug Controller (S12ZBDCV2) . . . . . . . . . . . . . . . . . 115

Chapter 4 Memory Mapping Control (S12ZMMCV1) . . . . . . . . . . . . . . . . . . . 153

Chapter 5 S12Z Interrupt (S12ZINTV0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165

Chapter 6 S12Z DebugLite (S12ZDBGV3) Module . . . . . . . . . . . . . . . . . . . . . . 179

Chapter 7 ECC Generation Module (SRAM_ECCV1) . . . . . . . . . . . . . . . . . . . 205

Chapter 8 S12 Clock, Reset and Power Management Unit (S12CPMU_UHV_V7)

217

Chapter 9 Analog-to-Digital Converter (ADC12B_LBA_V1) 283

Chapter 10 Supply Voltage Sensor - (BATSV3) . . . . . . . . . . . . . . . . . . . . . . . . . . 351

Chapter 11 Timer Module (TIM16B8CV3) Block Description. . . . . . . . . . . . . . 361

Chapter 12 Timer Module (TIM16B4CV3) Block Description. . . . . . . . . . . . . . 389

Chapter 13 Pulse-Width Modulator (S12PWM8B8CV2) . . . . . . . . . . . . . . . . . . 407

Chapter 14 Serial Communication Interface (S12SCIV6). . . . . . . . . . . . . . . . . . 437

Chapter 15 Serial Peripheral Interface (S12SPIV5). . . . . . . . . . . . . . . . . . . . . . . 477

Chapter 16 Inter-Integrated Circuit (IICV3) Block Description . . . . . . . . . . . . 503

Chapter 17 CAN Physical Layer (S12CANPHYV3) . . . . . . . . . . . . . . . . . . . . . . 531

Chapter 18 Scalable Controller Area Network (S12MSCANV3) . . . . . . . . . . . . 551

Chapter 19 Digital Analog Converter (DAC_8B5V_V2) . . . . . . . . . . . . . . . . . . . 605

Chapter 20 5V Analog Comparator (ACMPV2) . . . . . . . . . . . . . . . . . . . . . . . . . 617

Chapter 21 SENT Transmitter Module (SENTTXV1) . . . . . . . . . . . . . . . . . . . . 625

Chapter 22 192 KB Flash Module (S12ZFTMRZ192K2KV2) . . . . . . . . . . . . . . 643

Appendix A MCU Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 701

Appendix B ADC Electrical Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 717

Appendix C MSCAN Electrical Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . 723

Appendix D SPI Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 725

Appendix E CPMU Electrical Specifications (VREG, OSC, IRC, PLL). . . . . . . 729

MC9S12ZVC Family Reference Manual , Rev. 1.7

4 NXP Semiconductors

Appendix F BATS Electrical Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 733

Appendix G PIM Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 737

Appendix H ACMP Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 739

Appendix I S12CANPHY Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . 743

Appendix J DAC8B5V Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . 749

Appendix K NVM Electrical Parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 751

Appendix L Package Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 755

Appendix M Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 760

Appendix N Detailed Register Address Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 761

MC9S12ZVC Family Reference Manual , Rev. 1.7

NXP Semiconductors 5

Chapter 1

Device Overview MC9S12ZVC-Family

1.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

1.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

1.2.1 MC9S12ZVC-Family Comparison . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

1.3 Chip-Level Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

1.4 Module Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

1.4.1 S12Z Central Processor Unit (CPU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

1.4.2 Embedded Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

1.4.3 Clocks, Reset and Power Management Unit (CPMU) . . . . . . . . . . . . . . . . . . . . . . . . . . 25

1.4.4 Main External Oscillator (XOSCLCP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

1.4.5 Timer (TIM0 and TIM1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

1.4.6 Pulse Width Modulation Module (PWM0 and PWM1) . . . . . . . . . . . . . . . . . . . . . . . . . 27

1.4.7 Inter-IC Module (IIC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

1.4.8 CAN Physical Layer (CANPHY) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

1.4.9 Multi-Scalable Controller Area Network (MSCAN) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

1.4.10 SENT Transmitter (SENT_TX) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

1.4.11 Serial Communication Interface Module (SCI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

1.4.12 Serial Peripheral Interface Module (SPI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

1.4.13 Analog-to-Digital Converter Module (ADC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

1.4.14 Digital-to-Analog Converter Module (DAC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

1.4.15 Analog Comparator Module (ACMP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

1.4.16 Supply Voltage Sensor (BATS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

1.4.17 On-Chip Voltage Regulator system (VREG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

1.5 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

1.6 Family Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

1.6.1 Part ID Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

1.7 Signal Description and Device Pinouts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

1.7.1 Pin Assignment Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

1.7.2 Detailed Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

1.7.3 MODC — Mode C signal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

1.7.4 PAD[15:0] / KWAD[15:0] — Port AD, input pins of ADC . . . . . . . . . . . . . . . . . . . . . . 36

1.7.5 PE[1:0] — Port E I/O signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

1.7.6 PJ[1:0] — Port J I/O signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

1.7.7 PL[1:0] / KWL[1:0] — Port L input signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

1.7.8 PP[7:0] / KWP[7:0] — Port P I/O signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

1.7.9 PS[7:0] / KWS[7:0] — Port S I/O signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

1.7.10 PT[7:0] — Port T I/O signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

1.7.11 AN[15:0] — ADC input signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

1.7.12 ACMP Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

1.7.13 DAC Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

1.7.14 VRH_0, VRH_1, VRL_0, VRL_1 — ADC reference signals . . . . . . . . . . . . . . . . . . . . 38

1.7.15 ETRIG0 — External ADC trigger signal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

1.7.16 SPI signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

1.7.17 SCI signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

剩余796页未读,继续阅读

资源评论

JacksonQian

- 粉丝: 1153

- 资源: 10

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功