相位偏移 小至 156 皮秒(ps)的增量幅度

(2),(3)

可编程占空比

内部时钟输出数量 每个 PLL 两个输出

外部时钟输出数量

(4)

每个 PLL 一个输出

锁定端口可以输入逻辑阵列

PLL 时钟输出可以输入逻辑阵列

表 2 注释:

(1)M,N 和后 scale 计数器的值从 1 至 32

(2)最小的相位偏移量为压控振荡器(VCO)周期除以 8

(3) 对于角度调整,Cyclone FPGA 的偏移输出频率的增量至少为 45º。更小的角度增量可能取决于 PLL 时钟输出的倍频/分频系数。

(4) 100 脚的扁平四方封装(TQFP)的 EP1C3 器件不支持 PLL LVDS 输出或外部时钟输出。144 脚 TQFP 封装的 EP1C6 PLL2 不支持

外部时钟输出。

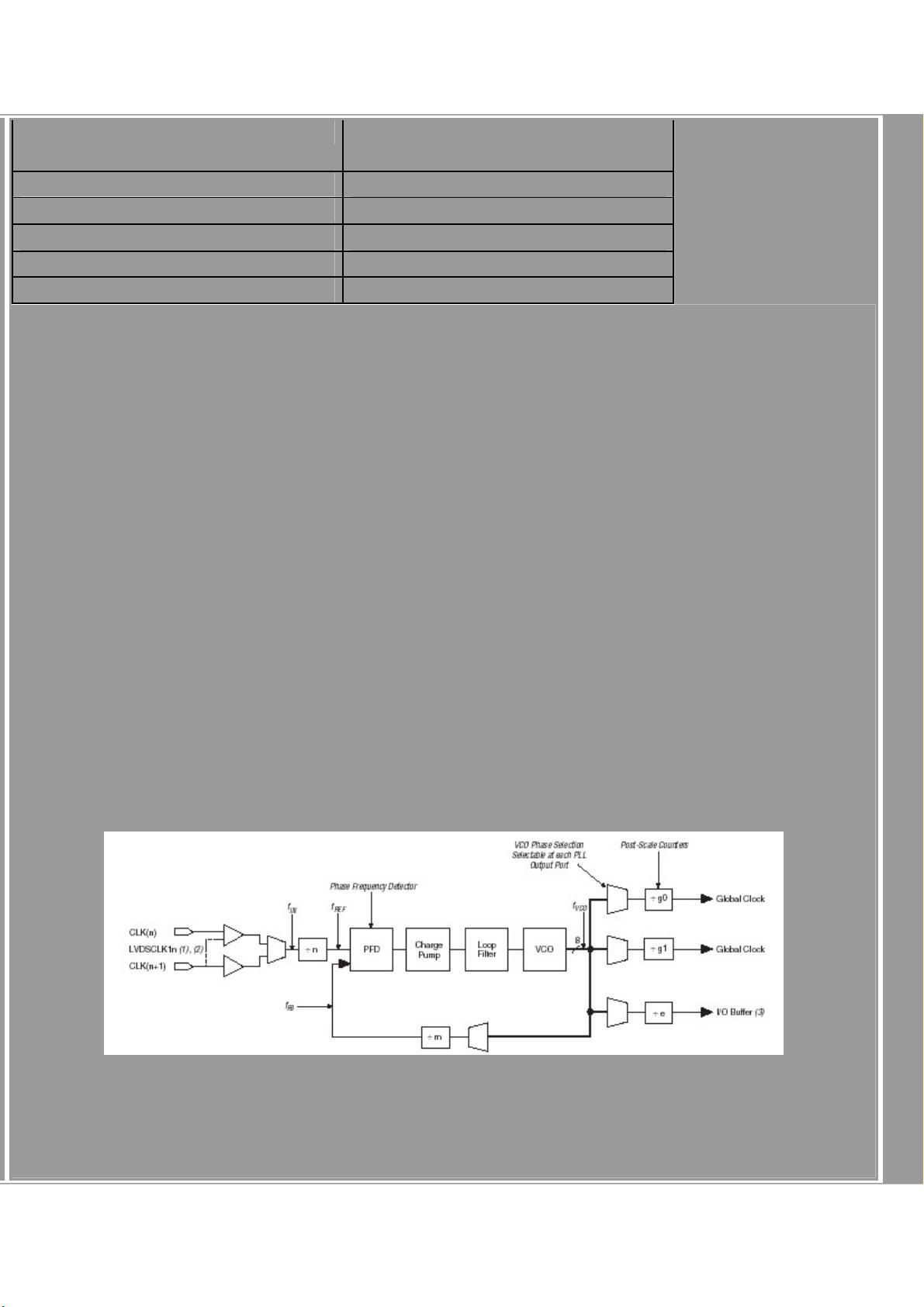

Cyclone PLL 区块

PLL 主要作用就是把内部/外部时钟的相位和频率同步于输入参考时钟。PLL 由许多部分组成,共同完成相位调整。

Cyclone PLL 采用一个相位频率检测器(PFD)把参考输入时钟的上升沿和反馈时钟对齐。根据占空比规定确定下降沿。PFD 产生一个上升

或下降信号,决定 VCO 是否需要以更高或更低的频率工作。PFD 输出施加在电荷泵和环路滤波器,产生控制电压设置 VCO 的频率。如果

PFD 产生上升信号,然后 VCO 就会增加。反之,下降信号会降低 VCO 的频率。

PFD 输出这些上升和下降信号给电荷泵。如果电荷泵收到上升信号,电流注入环路滤波器。反之,如果收到下降信号,电流就会流出环路滤

波器。环路滤波器把这些上升和下降信号转换为电压,作为 VCO 的偏置电压。环路滤波器还消除了电荷泵的干扰,防止电压过冲,这样就会

最小化 VCO 的抖动。

环路滤波器的电压决定了 VCO 操作的速度。VCO 是用四级差分环路滤波器实现的。反馈环路中的分频计数器增加输入参考频率以上的 VCO

频率,使得 VCO 频率(fVCO)等于输入参考时钟(fREF)的 M 倍。PFD 的输入参考时钟(fREF)等于输入时钟(fIN)除以欲 scale 计数

器(N)。因此,PFD 某个输入的反馈时钟(fFB)锁定于 PFD 的另一个输入的 fREF)。

VCO 的输出输入三个后 scale 计数器(G0、G1 和 E)。这些后 scale 计数器可以在 PLL 中产生许多谐振频率。

另外,PLL 有内部延迟单元补偿全局时钟网络的走线和外部时钟输出管脚的 I/O 缓冲器延迟。这些内部延迟是固定的,用户无法控制。

图 1 是 Cyclone PLL 主要部分的框架图

评论0

最新资源