没有合适的资源?快使用搜索试试~ 我知道了~

资源推荐

资源详情

资源评论

Hindawi Publishing Corporation

VLSI Design

Volume 2010, Article ID 213043, 11 pages

doi:10.1155/2010/213043

Research Article

FPGA Implementation of an Amplitude-Modulated

Continuous-Wave Ultrasonic Ranger Using Restructured

Phase-Locking Scheme

P. Sumathi

1

and P. A. Janakiraman

2

1

DA-IICT, Department of Information and Communication Technology, Gandhinagar, Gujarat 382007, India

2

Indian Institute of Technology Madras, Department of Electrical Engineering, Chennai 600036, India

Correspondence should be addressed to P. Sumathi, sumichan04@yahoo.co.in

Received 30 May 2009; Revised 9 September 2009; Accepted 8 December 2009

Academic Editor: Ethan Farquhar

Copyright © 2010 P. Sumathi and P. A. Janakiraman. This is an open access article distributed under the Creative Commons

Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is

properly cited.

An accurate ultrasonic range finder employing Sliding Discrete Fourier Transform (SDFT) based restructured phase-locked loop

(RPLL), which is an improved version of the recently proposed integrated phase-locking scheme (IPLL), has been expounded.

This range finder principally utilizes amplitude-modulated ultrasonic waves assisted by an infrared (IR) pilot signal. The phase

shift between the envelope of the reference IR pilot signal and that of the received ultrasonic signal is proportional to the range.

The extracted envelopes are filtered by SDFT without introducing any additional phase shift. A new RPLL is described in which

the phase error is driven to zero using the quadrature signal derived from the SDFT. Further, the quadrature signal is reinforced

by another cosine signal derived from a lookup table (LUT). The pulse frequency of the numerically controlled oscillator (NCO)

is extremely accurate, enabling fine tuning of the SDFT and RPLL also improves the lock time for the 50 Hz input signal to 0.04 s.

The percentage phase error for the range 0.6 m to 6 m is about 0.2%. The VHDL codes generated for the various signal processing

steps were downloaded into a Cyclone FPGA chip around which the ultrasonic ranger had been built.

1. Introduction

Ultrasonic sensors find applications generally in distance

measurement, indoor mobile robot control, for environment

information, gleaning, localization, and map building, vibra-

tion measurements, and safety systems like intelligent airbag

control [1–4]. Many range-finding techniques are found in

the literature, based on either the time of flight (TOF) or

the continuous wave method [5–7]. A variety of continuous

wave methods have been reported; notable among them

are based on the multifrequency and amplitude-modulated

(AM) schemes [8, 9]. The significant advantages of the AM

continuous-wave method over the TOF were presented in

[10]. The phase shift observed in the ultrasonic wave with

respect to the distance traveled can be used to measure the

range. For a 40 kHz sound wave, the maximum measurable

range using phase shift is only 8.6 mm. In the present

work, to enhance the measurable range to 6.86 m, the

ultrasonic signal is amplitude modulated by a 50 Hz signal,

which is more appropriate for mobile robot localization and

navigation in indoor applications.

In this scheme, a low-frequency-modulated Infrared (IR)

is used as a pilot signal. Another ultrasonic signal (US)

modulated by the same low-frequency signal is utilized for

estimating the range. A novel procedure using Sliding Dis-

crete Fourier transform (SDFT) can be employed to extract

the fundamental component of the envelope of the received

ultrasonic signal [11]. The sampling pulse frequency of the

SDFT block is tuned precisely by an integrated phase-locked

loop so that exactly one full period of the envelope signal

can be accommodated in a window of width 128 [12]. Two

such PLL’s, one for the extraction of the sinusoidal envelope

of the infrared pilot signal, and another for ultrasonic signal

are employed in the range-finding equipment. The PLL is

basically a feedback circuit minimizing the phase error by

correlating the given envelope signal with the quadrature

2 VLSI Design

signal derived from the SDFT block. The envelope of the IR

signal is the reference, against which the phase shift of the

extracted envelope of the amplitude-modulated ultrasonic

signal is compared. The integrated phase-locking scheme

discussed in [12] shows a steady residual error in the NCO

output frequency. The primary focus of the present paper

is to describe the restructured phase-locking scheme, which

makes use of a look up table to assist the quadrature signal

derived from the SDFT block mainly to reduce the residual

phase error. The hardware realization of the restructured

phase-locking scheme which is implemented in an FPGA

chip has also been described. The DSP builder tool, has been

applied extensively for simulation and practical realization of

an ultrasonic range finder.

The restructured phase locking scheme and its com-

ponents have been described in Section 2.Theproposed

ultrasonic range measurement scheme based on RPLL,

built using the DSP builder tool has been explicated in

Section 3. The simulation and experimental results obtained

using Cyclone FPGA have been presented in Section 4 and

Section 5, respectively. The major conclusions are drawn in

Section 6.

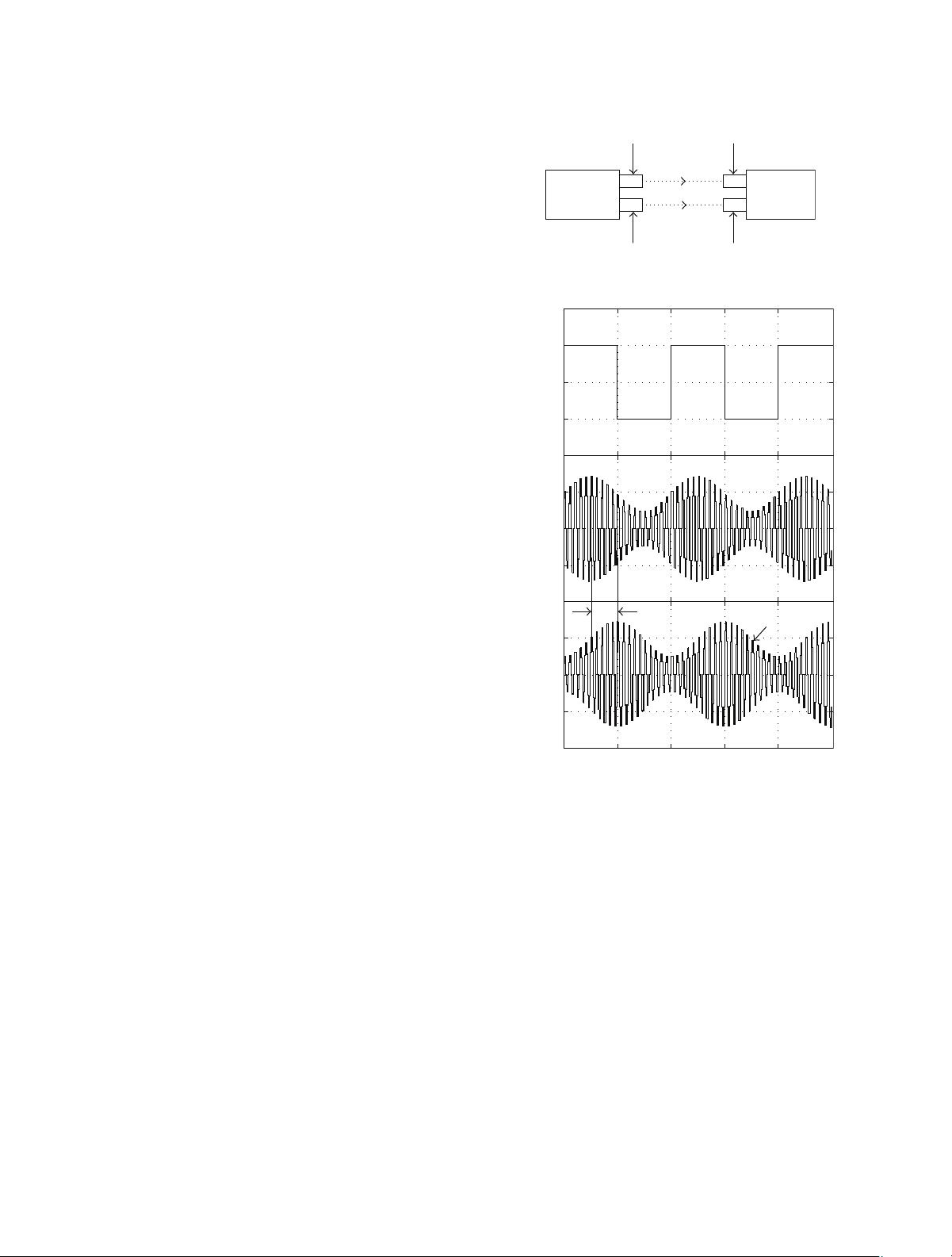

The schematic of the proposed ultrasonic range finder

is shown in Figure 1(a). This consists of a transmitter and

a receiver unit. The transmitter unit sends an IR pilot

signal as well as an ultrasonic signal, both simultaneously

modulated by a low-frequency sine wave. The receiver unit

contains an IR receiver and an ultrasonic receiver. On the

transmitter side a 40 kHz signal had been used to generate

the ultrasonic carrier and a 50 Hz sinusoidal signal for

amplitude-modulation. The 50 Hz sine wave is converted

into square wave using a limiter circuit for modulating the

IR pilot signal to serve as the instantaneous reference signal.

An ultrasonic transducer transmits the amplitude modulated

40 kHz signal. Figure 1(b) shows the transmitted reference IR

signal, ultrasonic signal, and the received ultrasonic signal.

On the receiver side, the ultrasonic signal is amplified,

rectified, and processed by an SDFT-based restructured

phase-locking scheme to extract the sinusoidal envelope.

The received reference IR signal is also processed using

another SDFT based RPLL for extracting the fundamental

component of the envelope. The detailed explanation of this

scheme is presented in the next section.

2. Restructured Phase-Locking Scheme

The operation of the restructured phase locked-loop (RPLL)

based on SDFT is briefly explained here. The detailed block

diagram of RPLL scheme is shown in Figure 2.Whena

periodic input signal is passed through a sliding DFT block

tuned to a particular frequency, two distinct output signals

are obtained. The first signal is basically the fundamental

component of the incoming periodic signal, which may,

however, be slightly shifted in phase, whenever the frequency

of the incoming signal deviates from the frequency for which

the SDFT block is tuned [12]. The SDFT block yields another

signal, which is in quadrature with the first output signal.

The correlation between the input signal and the quadrature

Tr an sm i tte r

unit

Receiver

unit

IR

transmitter

IR

receiver

Ultrasonic

transmitter

Ultrasonic

receiver

(a)

Amplitude

−0.5

0

0.5

Amplitude

−0.5

0

0.5

Amplitude

−1

0

1

Time (s)

00.01 0.02 0.03 0.04 0.05

Received ultrasonic signal

Transmitted ultrasonic signal

IR reference

Phase shift

Envelope

(b)

Figure 1: (a) Schematic of the proposed Ultrasonic Range Finder

and (b) IR reference signal, transmitted ultrasonic signal, and

received ultrasonic signal.

signal from the SDFT can be made use of, for adjusting the

frequency of the numerically controlled oscillator (NCO)

which provides the sampling pulses to the SDFT block,

resulting in the phase lock of the SDFT output [12]. Under

these conditions, the enabling or the sampling frequency

f

s

= fN,where f is the cyclic frequency of the periodic input

signal and N is the number of samples per cycle. Small phase

errors may still persist which can be greatly reduced by the

addition of an LUT-based pure quadrature signal. Essentially,

this scheme differs from the simple integrated phase-locking

scheme presented in [12]; in that, the quadrature signal

output of the SDFT block is supplemented by a cosine

wave from a lookup table accessed by an address counter

which in turn is driven by NCO pulses. The added cosine

剩余10页未读,继续阅读

资源评论

mahao007

- 粉丝: 7

- 资源: 20

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- comsol计算光子晶体平带合并BIC,复现包含二维能带,三维能带,品质因子和远场偏振计算

- 融合正余弦和柯西变异的麻雀搜索算法优化CNN-BiLSTM 仿真软件:matlab 主要内容:融合正余弦和柯西变异的麻雀搜索算法,对CNN-BiLSTM的学习率,正则化参数,BiLSTM隐含层神经元个

- 法兰内孔铣床sw18全套技术资料100%好用.zip

- 一维光子晶体超窄带滤波器 光学仿真,出模型文件,matlab代码以及说明文档

- 双馈惯量控制,下垂控制,减载控制,桨距角控制参与调频,四机两区域 三机九节点仿真建模

- 基于FPGA的FOC电流环实现 1.仅包含基本的电流环 2.采用verilog语言编写 3.电流环PI控制器 4.采用SVPWM算法 5.均通过处理转为整数运算 6.采用ADC采样,型号为AD7928

- 果蔬清洗机总体结构设计(step+exb+说明书)全套技术资料100%好用.zip

- VESC STM32F4磁链观测器,VESC磁链观测器 无感正弦FOC控制 vesc中使用的方法 已经移植到了自己的工程中,实现0速闭环启动 代码、文档、仿真是一一对应的,方便学习

- Dependency Walker 的新版本支持windows 10

- Python求解XDOJ平台三位整数各位置数字之和问题的技术实现与应用场景

- 滚动式不锈钢板材双面自动喷砂机sw14可编辑全套技术资料100%好用.zip

- 冲床平面送料程序,支持X轴和Y轴两个方向送料,PLC使用FX1S,触摸屏是昆仑通态,适用于绝大多数板材冲压冲裁自动送料

- 基于python实现的三维重建算法SFM源码(高分项目)

- 结合模型预测(MPC)的同步机控制(VSG)-MATLAB simulink仿真 等效直流电源,三相全桥逆变,LC型滤波器,并网运行 单步模型预测控制,同步机控制 用模型预测模块代替电压电流内环,取消

- 基于python的三维重建算法Structure from Motion(Sfm)实现代码.zip

- 基于FPGA的LDPC译码算法(提供ISE和Qii两个版本),包括MATLAB仿真,verilog程序,支持定制算法程序 从LDPC码的基础理论出发,在研究前人成果的基础上,针对CMMB标准,采取理论

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功