TPS552882-Q1-车规级.pdf

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

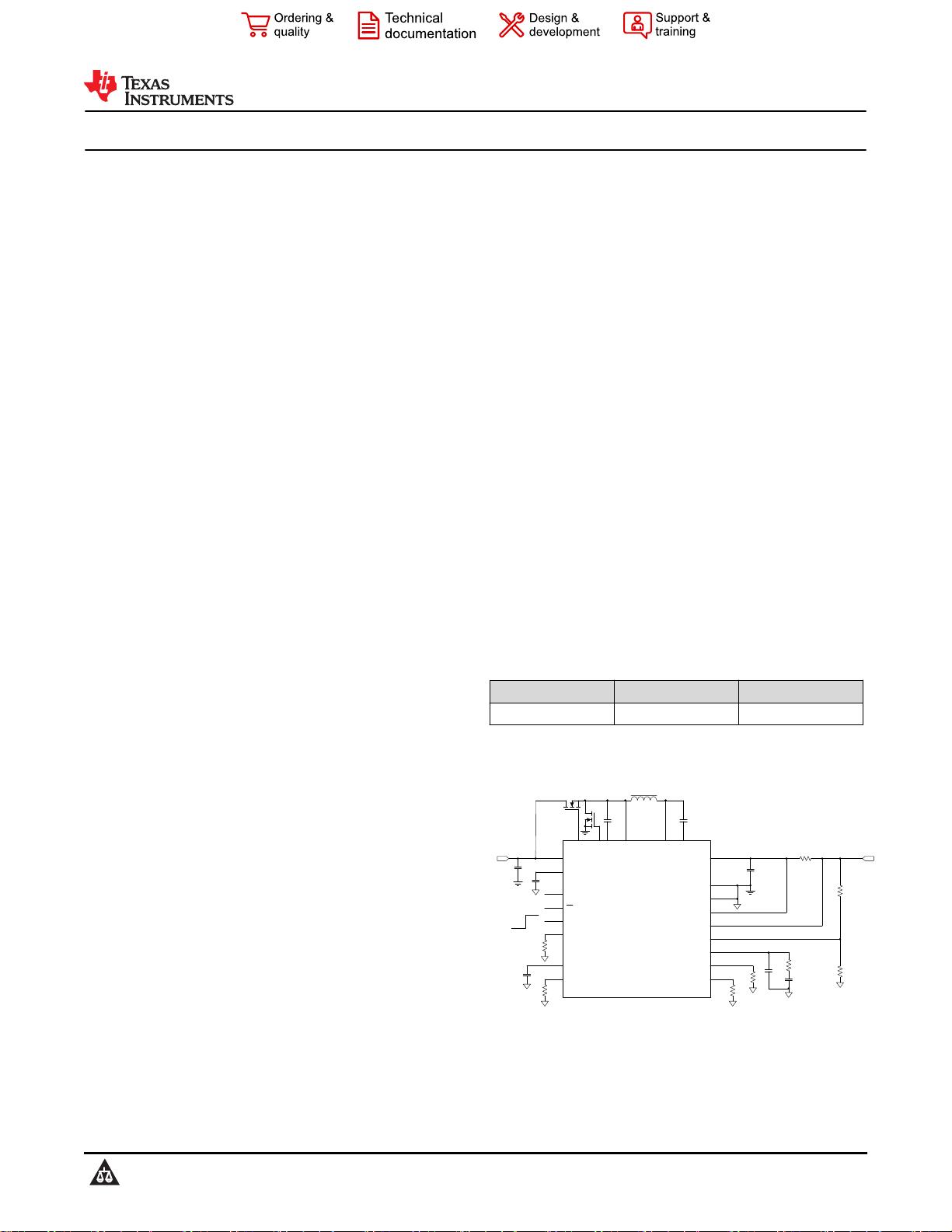

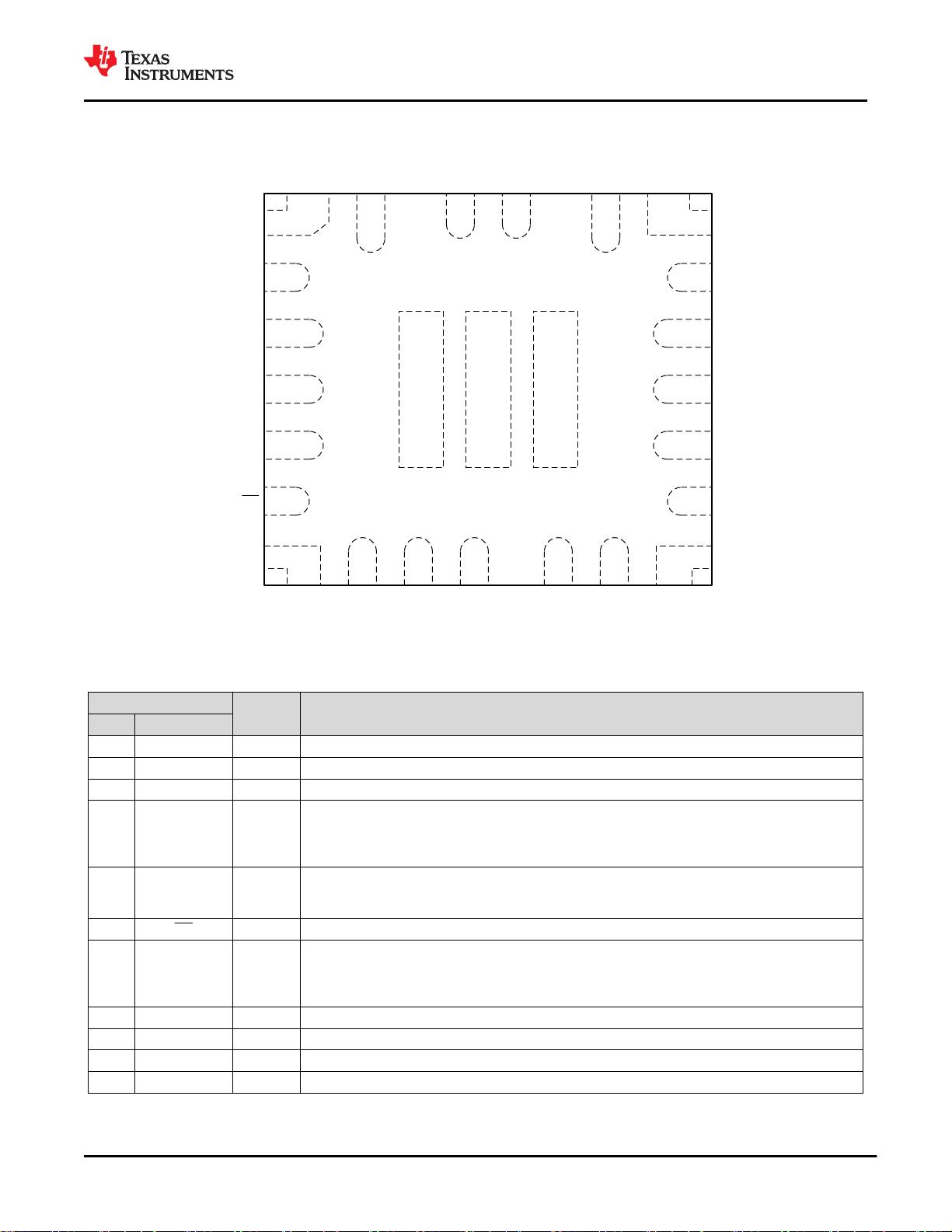

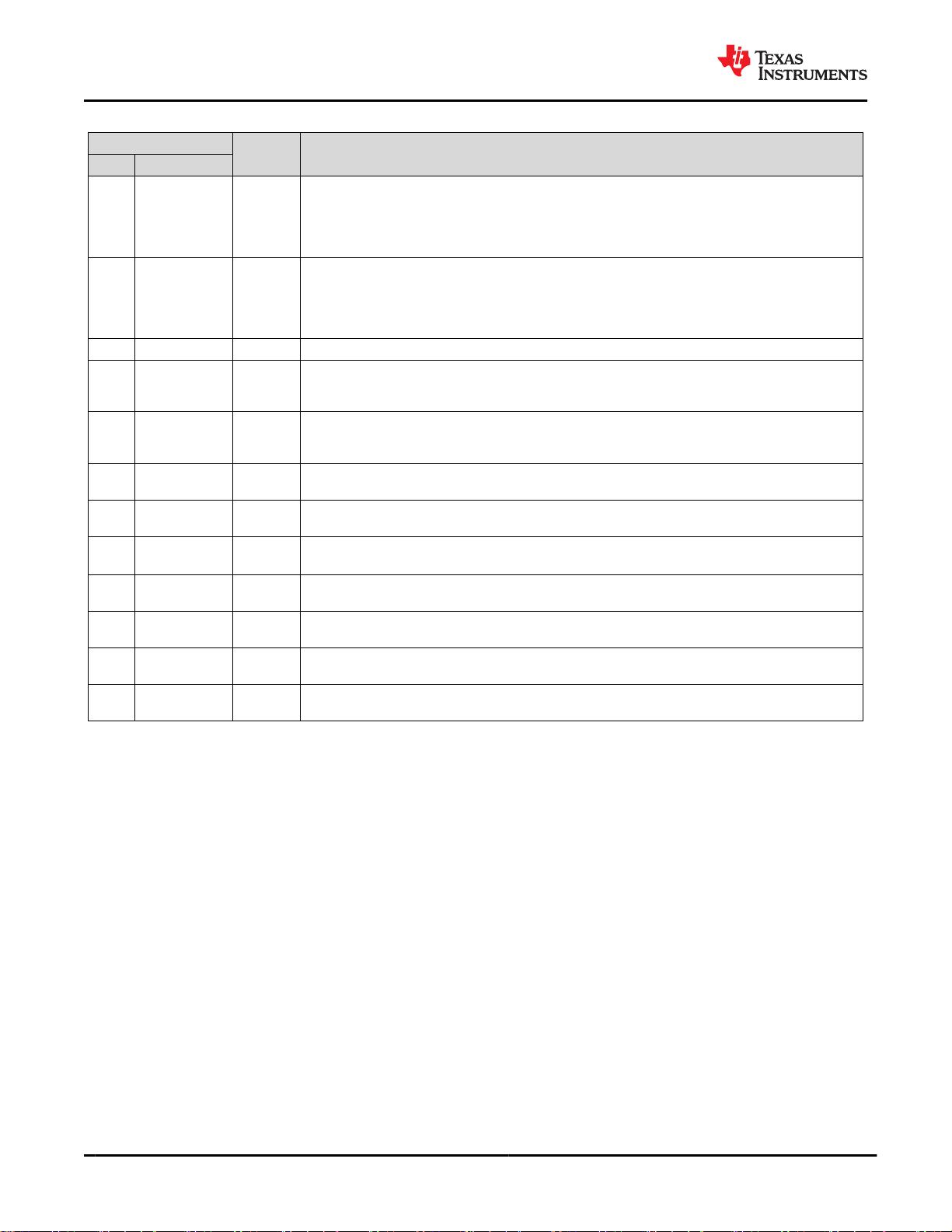

**TPS552882-Q1**是一款专为汽车应用设计的车规级**36V 16A**降压/升压转换器。该器件符合**AEC-Q100**标准,可在**-40°C 至 +125°C**的环境温度范围内稳定工作,确保了在严苛的汽车环境中的可靠性。 **关键特性**包括: 1. **宽输入和输出电压范围**:输入电压范围为**2.7V 至 36V**,输出电压范围则可在**0.8V 至 22V**之间调节,适应性强。 2. **高效率**:在**VIN = 12V、VOUT = 20V**且**IOUT = 3A**的条件下,转换效率达到**97%**,能有效降低能源损失。 3. **频率管理**:具备可选的**时钟同步**功能,以及**200kHz 至 2.2MHz**的**可编程开关频率**,有助于减少频率干扰和串扰。 4. **电磁干扰(EMI)降低**:支持可选的**可编程扩展频谱**,降低对外部组件的电磁影响。 5. **无引线封装**:采用**4.0mm × 3.5mm HotRod™ QFN**封装,减小了解决方案的体积。 6. **保护功能**:提供**输出过压保护**、**输出短路保护**、**热关断保护**及**可编程平均电感器电流限制**,确保系统安全。 7. **输出电压补偿**:可调整以补偿电缆上的压降。 8. **轻负载管理**:支持**可编程PFM(脉冲频率调制)**和**FPWM(强制脉宽调制)**模式,优化轻负载条件下的效率。 9. **感应电阻器的可编程输出电流限制**:允许用户根据应用需求设置电流限制。 10. **精确基准电压**:±1%的基准电压精度,确保了输出电压的稳定。 11. **软启动**:固定4ms的软启动时间,防止启动时的电流冲击。 **应用领域**广泛,涵盖了**USB PD**、**汽车信息娱乐系统**、**仪表组**和**汽车充电器**等。 **工作原理**:TPS552882-Q1内置两个**16A MOSFET**,通过同步四开关架构实现降压或升压转换。输出电压通过外部电阻分压器设定,利用内部1.2V基准电压。转换器采用**平均电流模式控制**,可编程开关频率和外部时钟同步功能提高了设计灵活性。此外,扩展频谱功能有助于降低EMI峰值。 **安全特性**方面,器件提供了多种保护机制,如输出过压保护、逐周期峰值电流限制、平均电感器电流限制和输出短路保护。在过载情况下,转换器可以切换到可选的输出电流限制和断续模式,以防止损害。 总体来说,TPS552882-Q1是一款高性能、高效率且具有全面保护功能的车规级电源转换器,适用于需要宽输入和输出电压范围以及小巧解决方案尺寸的应用。通过**WEBENCH® Power Designer**工具,设计者可以轻松创建基于TPS552882-Q1的定制电源设计方案。

剩余43页未读,继续阅读

- 粉丝: 57

- 资源: 2028

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功