1.掌握组合逻辑电路的分析方式与测试方式;

2.了解组合电路的冒险现象及消除方式;

3.验证半加器、全加器的逻辑功能。

二、预习要求

2.温习用与非门和异或门等组成的半加器、全加器的工作原理;

3.温习组合电路冒险现象(险象)的种类、产生原因,如何消除?

三、实验原理

由很多常常利用的门电路组合在一路,实现某种功能的电路,它在任意时刻的输出,

仅取决于该时刻输入信号的逻辑取值,而与信号作用前电路原来的状态无关。

2.组合逻辑电路的分析

是指按照所给的逻辑电路,写出其输入与输出之间的逻辑函数表达式或真值表,从而肯

定该电路的逻辑功能。其分析步骤为:

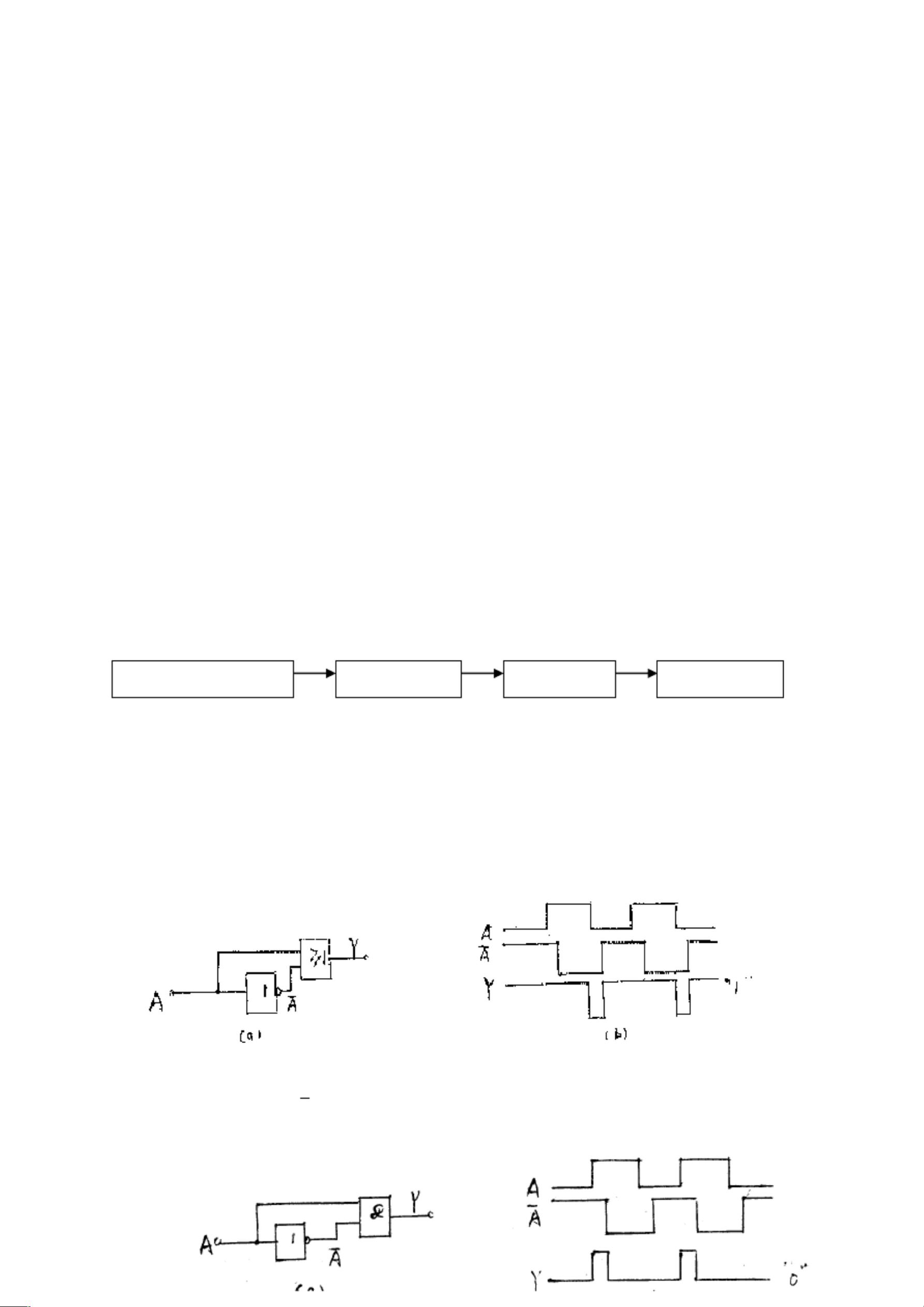

(1)实际情形下,由于器件的延时效应,在一个组合电路中,输入信号发生转变时,输出

出现瞬时错误的现象,把这现象叫做组合电路中的冒险现象,简称险象。这里研究静态险象,

即电路达到稳固时,出现的险象。可分为0 型静态险象(如图 4-1)和 1 型静态险象(如图

4-2):

其输出函数 Y=A+ ,在电路达到稳固时,即静态时,输出 Y 老是 1。但是在输入A 转变

时,输出 Y 的某些刹时会出现 0,Y 出现窄脉冲,存在有静态 0 型险象。