没有合适的资源?快使用搜索试试~ 我知道了~

教学大纲的实验内容,详细介绍了实验一的做法,VHDL的描述及电脑上机的具体操作步骤,及波形的仿真。。

资源详情

资源评论

资源推荐

实验一 组合逻辑电路的设计

一、 实验目的:

1.熟悉 QuartusⅡ 的 VHDL 文本设计流程全过程,学习简单组合电路的设计、

多层次电路设计、仿真和硬件测试。

2.加深 FPGA\CPLD 设计的过程,并比较原理图输入和文本输入的优劣。

二、 实验的硬件要求:

1.GW48EDA/SOPC+PK2 实验系统。

三、 实验内容及预习要求:

1.首先利用 QuartusⅡ 完成 2 选 1 多路选择器(如图 S1-1)的文本编辑输入

(mux21a.vhd)和仿真测试等步骤。最后在实验系统上进行硬件测试,验证本项

设计的功能。

图 S1-1

2.将此多路选择器看成是一个元件 mux21a,利用原理图输出法完成图 s1-2,

并将此文件放在同一目录中。

图 s1-2

编译、综合、仿真本例程,并对其仿真波形作出分析说明。最后在实验系统上

进行硬件测试,验证本项设计的功能。

3.以 1 位二进制全加器为基本元件,用例化语句写出 8 位并行二进制全加器的

顶层文件,编译、综合、仿真本例程,并对其仿真波形作出分析说明。最后在

实验系统上进行硬件测试,验证本项设计的功能。

4.七段数码管译码器(Decoder)

七段数码管译码器(Decoder)的输入为 4 位二进制代码,输出为 7 个

表征七段数码管代码的状态信号。下面为一个七段数码管译码器的 VHDL 源代

码模型:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY display IS

PORT(A:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

LED7S:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));

END;

ARCHITECTURE ONE OF display IS

BEGIN

PROCESS(A)

BEGIN

CASE A IS

WHEN "0000"=>LED7S<="0111111";--X"3F"->0

WHEN "0001"=>LED7S<="0000110";--X"06"->1

WHEN "0010"=>LED7S<="1011011";--X"5B"->2

WHEN "0011"=>LED7S<="1001111";--X"4F"->3

WHEN "0100"=>LED7S<="1100110";--X"66"->4

WHEN "0101"=>LED7S<="1101101";--X"6D"->5

WHEN "0110"=>LED7S<="1111101";--X"7D"->6

WHEN "0111"=>LED7S<="0000111";--X"07"->7

WHEN "1000"=>LED7S<="1111111";--X"7F"->8

WHEN "1001"=>LED7S<="1101111";--X"6F"->9

WHEN "1010"=>LED7S<="1110111";--X"77"->10

WHEN "1011"=>LED7S<="1111100";--X"7C"->11

WHEN "1100"=>LED7S<="0111001";--X"39"->12

WHEN "1101"=>LED7S<="1011110";--X"5E"->13

WHEN "1110"=>LED7S<="1111001";--X"79"->14

WHEN "1111"=>LED7S<="1110001";--X"71"->15

WHEN OTHERS=>NULL;

END CASE;

END PROCESS;

END;

编译、综合、仿真本例程,并对其仿真波形作出分析说明。最后在实验系

统上进行硬件测试,验证本项设计的功能。

四、 实验连线:

1.恰当选择电路结构,完成上述实验连线。

五、 实验报告要求

(1)对于原理图设计要求有源图。对于 VHDL 语言设计要求有源码。

(2)详细论述实验步骤。

(3)详细论述仿真步骤,并作出仿真结果。

一、数据选择器(2 选 1)

1、源文件

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY mux21a IS --二选一的数据选择器

PORT( a,b,s : INSTD_LOGIC;

y : OUT STD_LOGIC);

END mux21a;

ARCHITECTURE one OF mux21a IS

BEGIN

y<=a when s='0' else b;

END one;

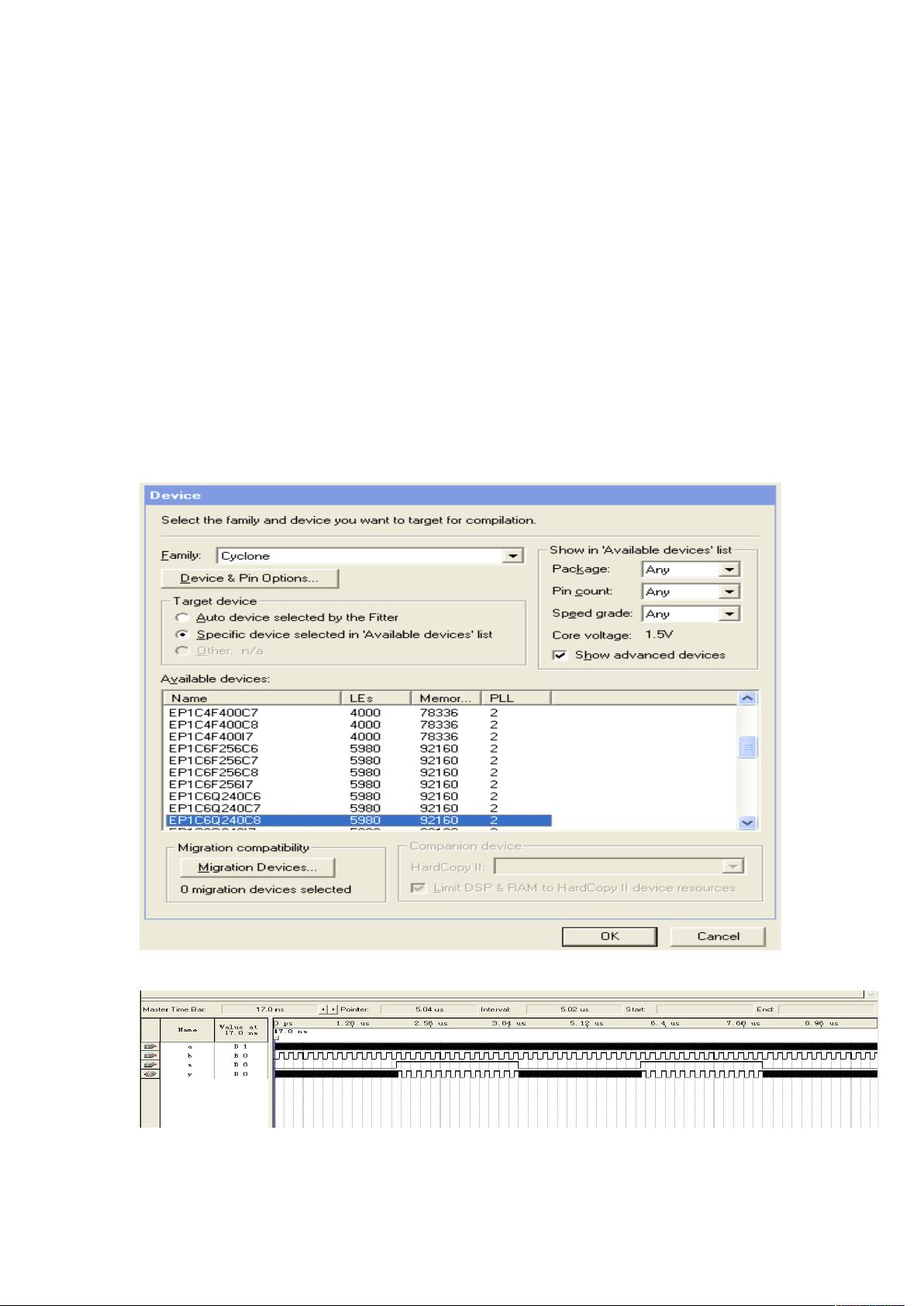

!!!!注意:编译前要根据具体芯片在 Assignments----Device 选择具体器件。此系统的器件是:

2、仿真波形(检查电路方法之一,或者查看 RTL 级电路)

3、管脚锁定

思路一:通过 a,b 与 s 三个结高低电平,输出用一个 led 灯显示;

剩余10页未读,继续阅读

a815073773

- 粉丝: 0

- 资源: 3

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0