实验四的目的是让学生熟悉使用Quartus II和ModelSim软件,掌握原理图和Verilog HDL混合输入设计方法,以及4位计数器的设计与仿真流程。在这个实验中,学生需要设计一个4位计数器,并在KX3C10F+开发板上实现,同时编写计数器模块CNT4B和数码管译码驱动模块DECL7S的Verilog HDL代码,完成整个系统的仿真。

实验原理基于FPGA内部电路,设计的4位计数器是一种常见的数字逻辑电路,用于计数一定范围内的脉冲。在这个案例中,计数器模块CNT4B需要包含四个二进制计数单元,可以实现从0000到1111的计数,即从0到15。模块通常包括输入时钟CLK、复位RST信号,输出out连接到数码管译码驱动模块DECL7S,用于显示当前计数值。

计数器的工作原理是,每当CLK上升沿到来时,计数器的值加1,如果计数达到最大值(1111),则会自动回零,形成循环计数。RST信号用于将计数器重置到初始状态(通常是0)。模块CNT4B的Verilog HDL代码可能包含如下的结构:

```verilog

module CNT4B(

output reg [3:0] out,

input wire CLK,

input wire RST

);

always @(posedge CLK or posedge RST) begin

if (RST)

out <= 4'b0000;

else

out <= out + 1'b1;

end

endmodule

```

数码管译码驱动模块DECL7S的作用是将4位二进制数转换为7段数码管的控制信号,使得数码管能够正确显示对应的数字。译码过程涉及查找对应于输入二进制数的7段码,每段对应一个LED,可以开启或关闭。例如,对于4位二进制数0001(十进制1),译码器将输出特定的7段码,点亮数码管的相应部分显示数字1。

在实验设备方面,使用KX3C10F+开发板,这是一块集成了FPGA的硬件平台,允许用户在板上实现和测试数字电路设计。电脑则用于运行Quartus II和ModelSim软件,进行设计、编译和仿真。

在编译阶段,Quartus II会分析Verilog代码,将高级描述转化为具体的逻辑门级表示,占用FPGA中的逻辑元素(LEs)。实验数据显示,11个LEs被用作组合逻辑,4个用于时序逻辑。组合逻辑负责无记忆的计算功能,而时序逻辑包含存储元件,如寄存器,用于保存数据并响应时钟信号变化。

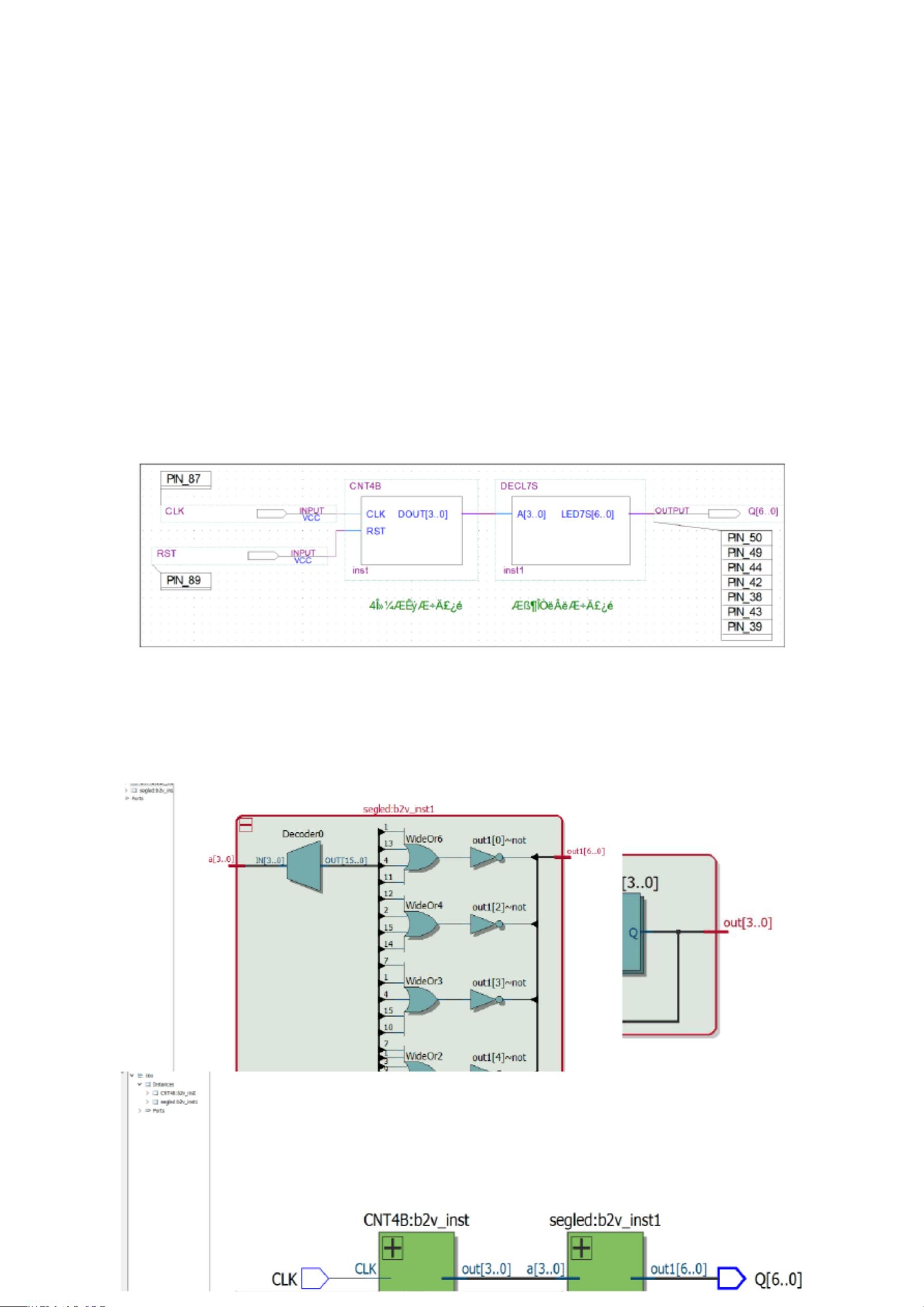

通过查看综合出来的电路图,可以看到CNT4B模块和segled模块(七段数码管显示)的连接。CLK和RST信号分别连接到计数器模块的输入,输出连接到译码驱动模块,以驱动数码管显示计数器的当前值。

在实验步骤中,除了设计和编译外,还需要对设计进行仿真验证。仿真测试模块(test module)会发送模拟的CLK和RST信号,并检查输出是否按预期工作。这通常涉及创建各种测试向量,以覆盖所有可能的计数情况和边界条件。

通过这个实验,学生不仅能够学习到FPGA设计的基本流程,还能深入理解计数器和数码管译码器的工作原理,为未来更复杂的数字系统设计打下坚实基础。