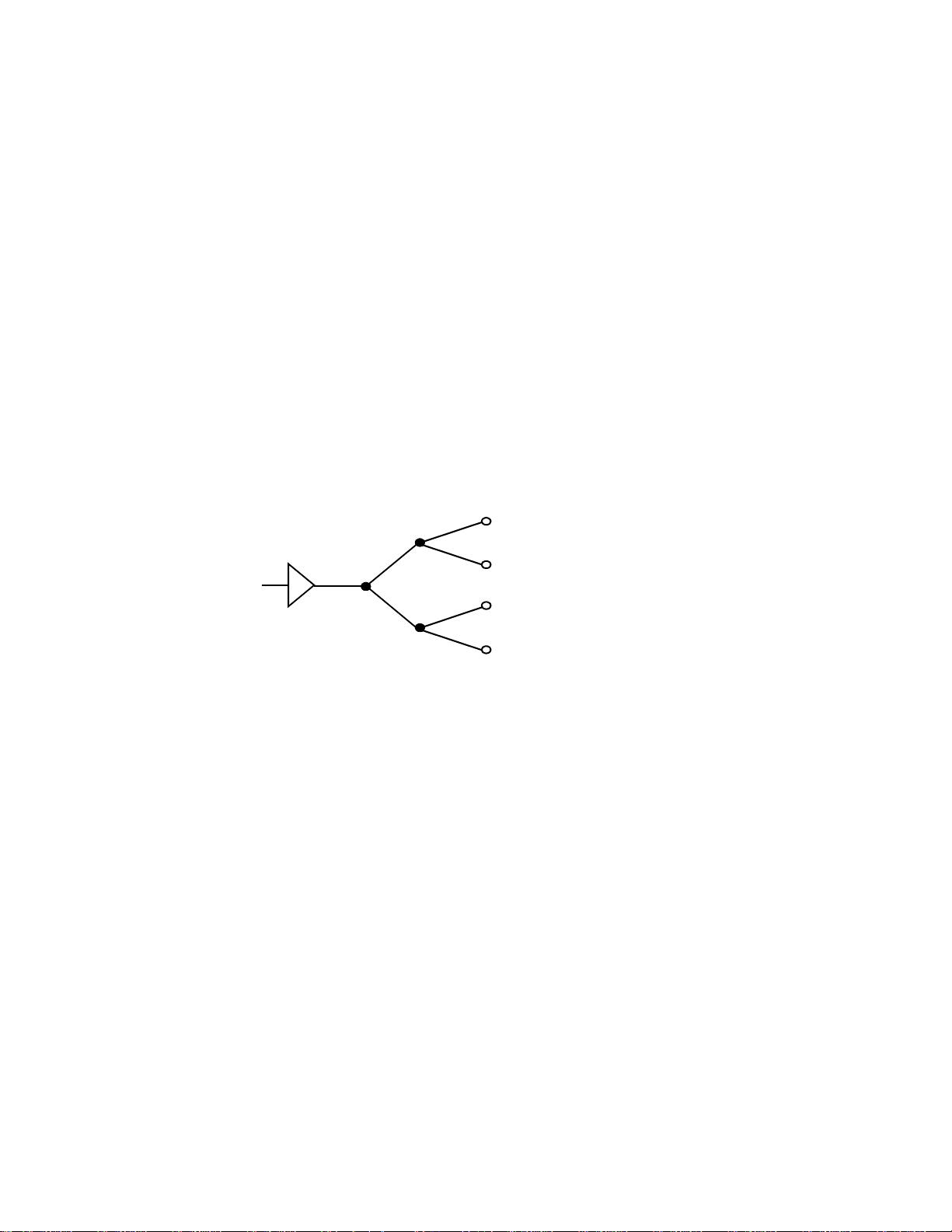

"时钟分布网络设计与分析" 在数字电路设计中,时钟分布网络是一个非常重要的组件,它对整个系统的时序性能产生了极大的影响。本章节我们将讨论时钟分布网络的设计和分析,包括时钟网络的拓扑结构、时钟信号的延迟和抖动、时钟网络的模型化和仿真等方面的内容。 让我们从时钟分布网络的基本概念开始。时钟分布网络是指从时钟源到各个寄存器或 Flip-Flop 的clock信号的分配网络。这个网络的设计对整个系统的时序性能产生了极大的影响。时钟分布网络的设计需要考虑许多因素,包括时钟信号的延迟、抖动和 skew 等。 在 Problem 1 中,我们讨论了时钟分布网络的设计和分析。假设我们有一个时钟分布网络,如 Figure 0.1 所示。每个时钟线段的长度为 5mm,宽度为 3 µm,材料为多晶硅(Polysilicon)。在每个终端节点上都有一个负载电容,电容值为 100 fF。在这种情况下,我们需要计算时钟驱动器的平均电流,以确保时钟信号的稳定性。 在计算时钟驱动器的平均电流时,我们可以忽略时钟网络的电阻和感抗,但是这并不是实际情况。在实际情况下,我们需要考虑时钟网络的电阻和感抗对时钟信号的影响。因此,我们可以使用 Π 型网络模型来描述时钟网络的行为。Π 型网络模型是一种常用的时钟网络模型,它可以描述时钟网络的电阻、感抗和电容对时钟信号的影响。 在问题 1 中,我们还讨论了时钟分布网络的时域分析。时域分析是指对时钟信号的时域响应进行分析,以确定时钟信号的延迟和抖动。时域分析可以帮助我们确定时钟分布网络的性能,并对时钟信号的时序性能进行优化。 在 Problem 2 中,我们讨论了时钟分布网络的设计和优化。假设我们需要设计一个时钟分布网络,以便在多个时钟域之间保持同步。在这种情况下,我们需要对时钟分布网络进行优化,以确保时钟信号的延迟和抖动满足要求。我们可以使用 SPICE 软件来模拟时钟分布网络的行为,并对时钟信号的时序性能进行优化。 在 Problem 3 中,我们讨论了 CMOS 反相器和时钟分布网络的设计和分析。CMOS 反相器是一个常用的数字电路元件,它可以用来实现时钟信号的缓存和反相。在时钟分布网络中,CMOS 反相器可以用来缓存时钟信号,以减少时钟信号的延迟和抖动。我们可以使用 SPICE 软件来模拟 CMOS 反相器和时钟分布网络的行为,并对时钟信号的时序性能进行优化。 本章节我们讨论了时钟分布网络的设计和分析,包括时钟网络的拓扑结构、时钟信号的延迟和抖动、时钟网络的模型化和仿真等方面的内容。我们还讨论了 CMOS 反相器和时钟分布网络的设计和分析,以便对时钟信号的时序性能进行优化。

- 粉丝: 80

- 资源: 9

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 【岗位说明】物业保安人员岗位职责.doc

- 【岗位说明】物业有限公司综合部厨工岗位职责.doc

- 【岗位说明】物业管理处环境部绿化工岗位职责.doc

- 龙门式6点伺服可调中频逆变电阻焊机sw19全套技术资料100%好用.zip

- 【岗位说明】陶瓷部门职能岗位职责.doc

- 【岗位说明】最新实用陶瓷企业生产规范岗位说明书.doc

- 【岗位说明】陶瓷部门职能岗位职责.docx

- 【岗位说明】电力公司岗位职责.docx

- 【岗位说明】电网公司岗位职责02.doc

- 【岗位说明】电力公司岗位职责.doc

- 【岗位说明】电力公司岗位职责说明02.doc

- 【岗位说明】电力施工项目经理岗位职责.doc

- 【岗位说明】供电公司部门职责.doc

- 【岗位说明】苏州电力公司人力资源部主任岗位职责描述.doc

- 【岗位说明】某电力公司客户经理岗位职责描述.doc

- 【岗位说明】石油开采岗位责任制.doc

信息提交成功

信息提交成功