电子线路 EDA 实验指导书

电子科学与技术系

吴友宇 主编

武汉理工大学教材出版中心

2012 年 8 月 26 日

1

目 录

第一部分 实验开发系统硬件介绍………………………………………1

第二部分 Quartus II 软件介绍……………………………………………5

第三部分 数字可编程器件实验部分……………………………………9

实验一 Quartus II 开发环境入门……………………………………9

实验二 全加器设计…………………………………………………25

实验三 触发器及计数器设计………………………………………27

实验四 动态扫描显示电路设计……………………………………29

实验五 综合层次性实验——交通灯设计实验……………………30

实验六 综合层次性实验——数字钟设计实验……………………32

2

第一部分 实验开发系统硬件介绍

1 概述

武汉理工大学 EDA 实验箱是针对数字电路设计 FPGA 实验开发的系统,由于可编程器件的

设计灵活性,其系统更能满足本科电类专业的 EDA 实验教学、课程设计、毕业设计及大学生电

子设计竞赛等。

2 配套软件

Quartus II 8.0 基础版 (商业版见报价单及相关资料说明)

1.运行环境 Win2000/2000XP 2.层次化设计 支持

3.原理图输入 支持 4.文本输入 支持

5.AHDL 输入 支持 6.VHDL 输入 支持

7.原理图设计宏库 基本库 8.仿真和时序分析 支持

9.逻辑综合 支持

10. 硬件编程/下载 支持

11.支持芯片 Cyclone 系列的 EP1C3T144C8

3 注意事项

3.1 核心板上的下载口有 JTAG 和 AS 两种下载口,调试时请用 JTAG 口下载(核心板右边

的下载口)。

3.2 电源孔是内正外负,接 5V 直流电源。

3.3 下载线不可以热插拔,不用实验箱时,一定要关闭实验箱的电源,然后才可以插拔下载

线。

3.4 在使用 QUARTUS II 时,一定要将未使用管脚设置为高阻态,具体步骤为:

assignments->device->device & options->unused pins 中选择。

3

4 系统硬件组成

4.1 开放式实验箱结构组成

本实验箱使用的 ALTERA 的 CYCLONE 系列 EP1C3,该芯片有 144 个管脚。 本实验箱使

用其通用 I/O 口共 98 个。由于实验项目多,所以 I/O 口采用共用的形式。

复用的模块有点阵显示、EEPROM、VGA、UART、PS2、数码管显示、液晶显示、交通灯

共 8 个模块。其具体来说就是点阵显示加上 EEPROM 的 I/O 口与其它 6 个模块使用相同的 I/O

口。具体对应的 I/O 口管脚已经在板子上标明。

开放式实验箱的组成:FPGA 核心板、8 位 8 段数码显示单元、点阵显示单元、拨码开关单

元、按键单元、LCD 显示单元、单片机单元、功能扩展区域、存储器单元(2864)、逻辑电平

单元、JTAG 下载接口、LED 显示单元、交通灯显示单元、数模转换、模数转换、温度采集、

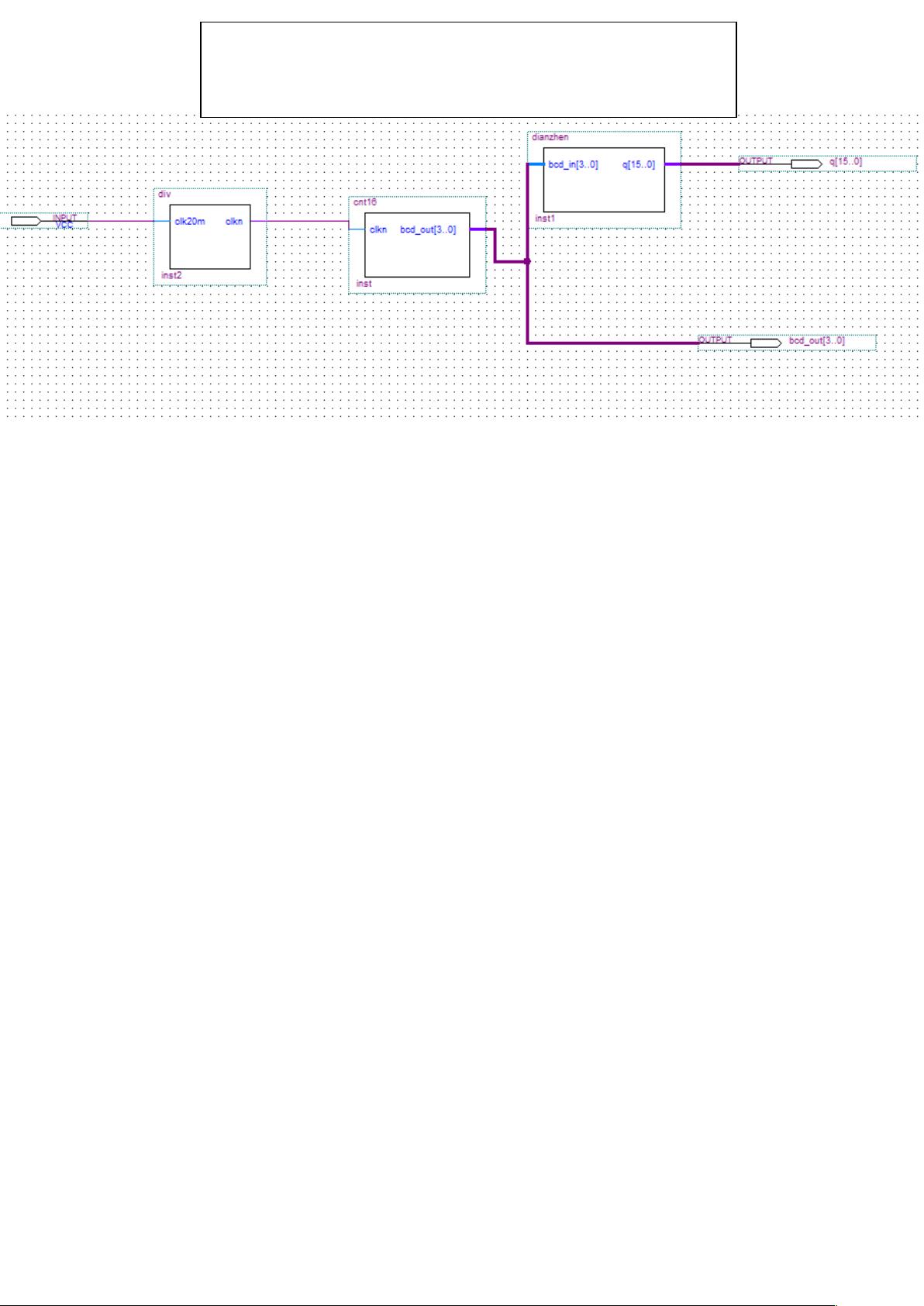

串口、VGA、PS/2 和音频输出模块、电源单元。实验箱组成框图如图 1-1 所示:。

图 1-1 实验箱结构框图

4

4.2 核心板

FPGA 核心板配置是的可编程逻辑器件是 ALTERA 公司的 EP1C3TC144 构成的最小系统,

包括时钟电路,JTAG 下载电路,AS 下载电路,复位按键电路,1 个 LED 指示灯。核心板使用

插座与实验平台底板连接,进行功能扩展。核心板将所有的用户端口接出,以便开发者有足够

的 IO 口资源可以使用。共有 98 个可用 IO 口。

时钟电路采用的是 20M 的有源晶振,送入 FPGA 的全局时钟网络。时钟输入管脚锁定

p16。为了满足特定电子系统的需求,需要设计分频器将频率 20M 时钟变为系统所需要的时钟。

核心板上的下载口有 JTAG 和 AS 两种下载口,调试时请用 JTAG 口下载(核心板右边的下

载口)。JTAG 下载电路是用来调试 FPGA 使用的,其下载的数据掉电后会丢失。当设计完成时

就可以用 AS 下载电路将设计的数据下载到外部配置存储器里,这样上电时数据就会自动配置

到 FPGA 中。当程序运行出现异常时,可以用复位键将外部配置存储器里数据从新配置进

FPGA,让其从新工作。

4.3 流水灯和交通灯

8 位流水灯和 12 位交通灯都是采用的共阴极的连接方式,即输出高电平是 LED 亮,输出低

电平时 LED 灭,这比较符合我们的思维习惯,有利于初学者使用。LED 对应的 IO 管脚已经在

电路板上标注,如:实验箱 8 位 LED 灯输出管脚锁定 p104~p111。

其中交通灯的管脚是和点阵模块的一部分管脚共用的,使用时请注意:一个管脚在一个时

刻只能被一个模块使用,点阵使用时,交通灯就不能使用。

4.4 拨码开关和按钮

16 位拨码开关和 16 位按钮是属于输入模块,他们都有两种状态,输入高电平或者输入低

电平。16 位拨码开关输入管脚锁定 p49~p62,p67,p68,p49~p62,p67,p68;

使用时请注意:由于它们都是机械开关,都有一定的抖动,所以在输入信号输入 FPGA 时

一定要加上去抖电路,这样才能保证设计中不会产生误操作,使设计具有好的稳定性。

4.4 数码管显示

数码管显示模块使用两个四位的共阴极数码管,为了减少对 FPGA 管脚的占用,电路中采用

动 态 显 示 方 式 。 8 个 数 码 管 的 段 选 端 是 并 接 的 , 其 8 位 段 驱 动 接 口 :

5