《VHDL 语言》课程设计

设计题目:基于 FPGA 的数字秒表的 VHDL 设计

系 别:电子信息科学与技术学院

姓 名: 牛 洪 军

班 级: 05 电子

学 号: 0509010019

指导老师: 孙惠章

设计时间:2008 年 6 月 16 日

《VHDL》课程设计报告 2022-6-19

目 录

前言…………………………………………………………………2

一、设计任务及要求……………………………………………2

二、方案论证……………………………………………………2

三、设计总体框图………………………………………………4

四、硬件电路设计与程序设计………………………………5

五、编译仿真……………………………………………………10

六、心得体会………………………………………………………12

参考文献:……………………………………………………………12

1

《VHDL》课程设计报告 2022-6-19

前言

秒表计时器常常用于体育竞赛及各种其他要求有较精确时间的各领域中。其中启/停开关的

使用方法与传统的机械计时器相同,即按一下启/停开关,启动计时器开始计时,再按一下

启/停开关计时终止。而复位开关可以在任何情况下使用,即使在计时过程中,只要按一下

复位开关,计时应立即终止,并对计时器清零。本文是主要是用 CPLD 的一些知识简单的

设计秒表的过程。

一、设计任务及要求

1. 设计数码管显示的秒表。

2. 能够准确的计时并显示。

3. 开机显示 00.00.00。

4. 用户可以随时清零、暂停、计时。

5. 最大记时 59.59.99 分钟,最小精确到 0.01 秒。

二、方案论证

方案一 采用 8051IP 核设计。用 FPGA 构成一个 8051 单片应用系统具有如下优缺点:

1、拥有标准 8051 完全兼容的指令系统的 CPU;

2、256 字节内部 RAM;

3、4K 字节程序 ROM;

4、每一此编译下载后都能根据需要更新 ROM 中的程序,所以该单片机的实现和使用如

同 89C51/52 一样方便。

缺点:

1. 设计烦琐可以直接用 8051 单片机代替。

2. 程序复杂。

方案二 采用芯片 EP1C12Q240C8、共阴七段数码管、按键开关、发光二极管设计。

2

《VHDL》课程设计报告 2022-6-19

1

“EP1C12Q240C8 是 Cyclone 器 件 ,Cyclone 可 以 最 多 支 持 129 个 通 道 的 LVDS 和

RSDS。Cyclone 器件的 LVDS 缓冲器可以支持最高达 640Mbps 的数据传输速度。与单端的

I/O 口标准相比,这些内显置于 Cyclone 器件内部的 LVDS 缓冲器保持了信号的完整性,并

且有更低的电磁干扰、更好的电磁兼容性(EMI)及更低的电源功耗。采用此芯片设计简

单,不需要用汇编语言编写程序,直接用 VHDL 编写即可以.”

缺点:与 8051IP 核相比精确度不是很高。但是对于秒表系统设计可以满足要求。

采用方案二也有两种具体的实现方法:

1、模块式设计方法。在此采用此方式设计。

2、一个整体 VHDL 语言描述的 VHDL 模块(张亦华的《数字电路 EDA 入门》一书中

有其原理介绍)。

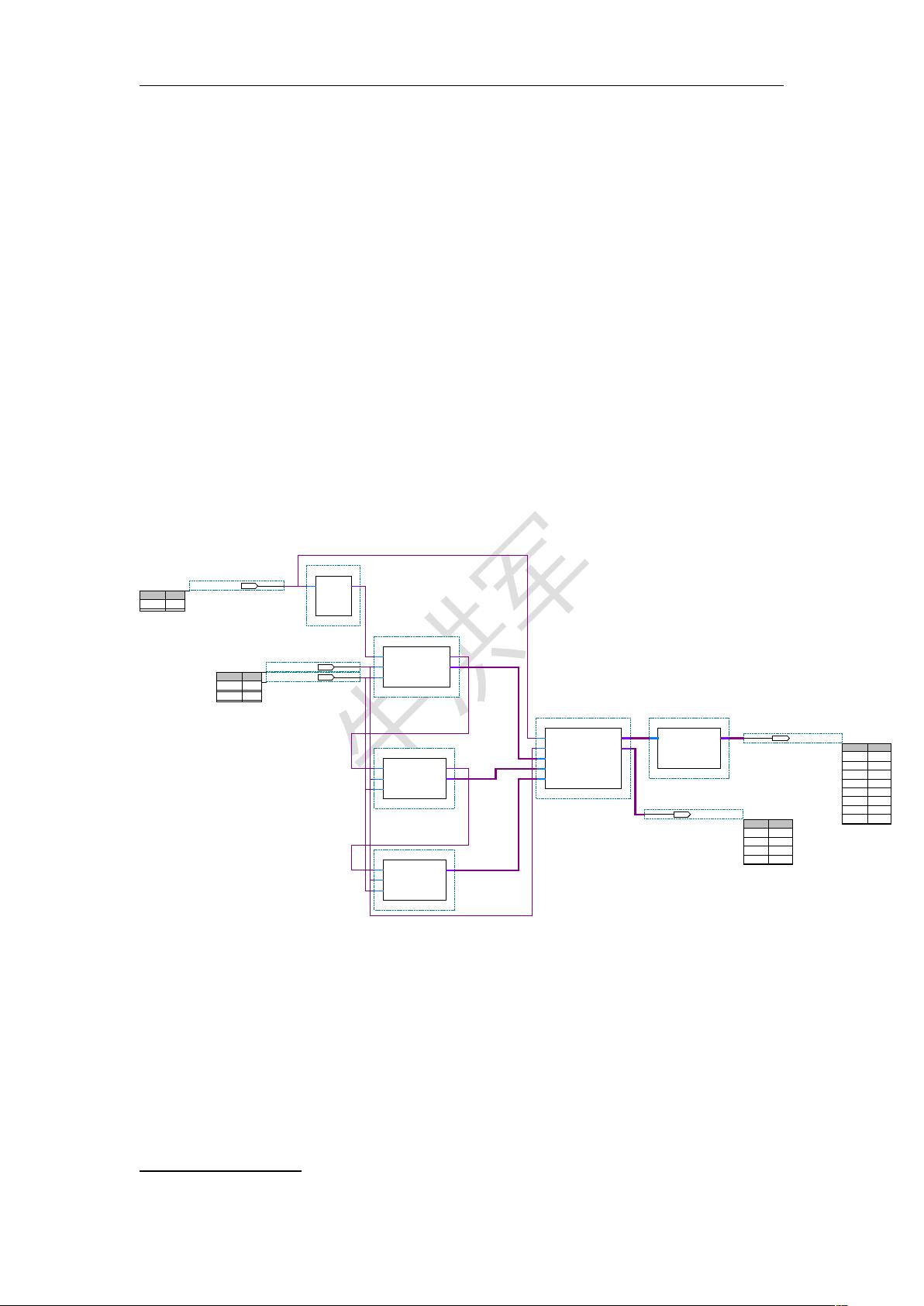

三、设计总体框图

Location PIN_4

Option V alue

VCC

set

INPUT

Location PIN_3

Option V alue

VCC

reset

INPUT

Location PIN_2

Option V alue

VCC

clk

INPUT

Location PIN_5

Location PIN_6

Location PIN_7

Location PIN_8

Location PIN_11

Location PIN_12

Location PIN_13

Location PIN_14

Option Value

led[6..0]

OUTPUT

Location PIN_15

Location PIN_16

Location PIN_17

Location PIN_18

Option Value

sel[ 2..0]

OUTPUT

clk

reset

setmsec

ensec

daout[ 7..0]

ms econd

inst

clk

reset

setmin

daout[ 6..0]

minute

inst2

num[3..0] led[6..0]

deled

inst3

clk 1

reset

msec[7..0]

sec[6..0]

minute[6.. 0]

daout[3..0]

sel[ 2..0]

zhishi

inst4

clk newclk

f enpin

inst 10

clk

reset

sets ec

enmin

daout[ 6..0]

second

inst5

1

在网上获得。

3

《VHDL》课程设计报告 2022-6-19

三、硬件电路设计与程序设计

本设计采用模块化设计,共分为 顶层文件、控制毫秒模块(msecond)、控制秒模块

(second)、控制分钟模块(minute)、LED 模块(alert)、数码管扫描模块(zhishi)、分频

器模块(fenpin)六个模块。其中 LED 模块可以去掉,不影响秒表正常运行以下对各个模块

一一描述。

1. 分频器模块

clk newclk

f enpin

inst10

系统的输入时钟为 4100HZ,用来驱动显示电路;同时输入时钟通过 41 分频,可以

产生 100HZ 的频率来驱动计数电路,即为 0.01 秒,程序实现如下:

LIBRARY ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

ENTITY fenpin IS

port (

clk : IN STD_LOGIC;

newclk : OUT STD_LOGIC);

END entity fenpin ;

ARCHITECTURE fun OF fenpin IS

signal enter: integer;

begin

process(clk)is

begin

if clk’event and clk=’1’ then

if enter=40 then enter<=0;

else enter<=enter+1;

end if;

end if;

end process;

process(enter)is

begin

if enter=40 then newclk<=’1’;

else newclk<=’0’;

end if;

4