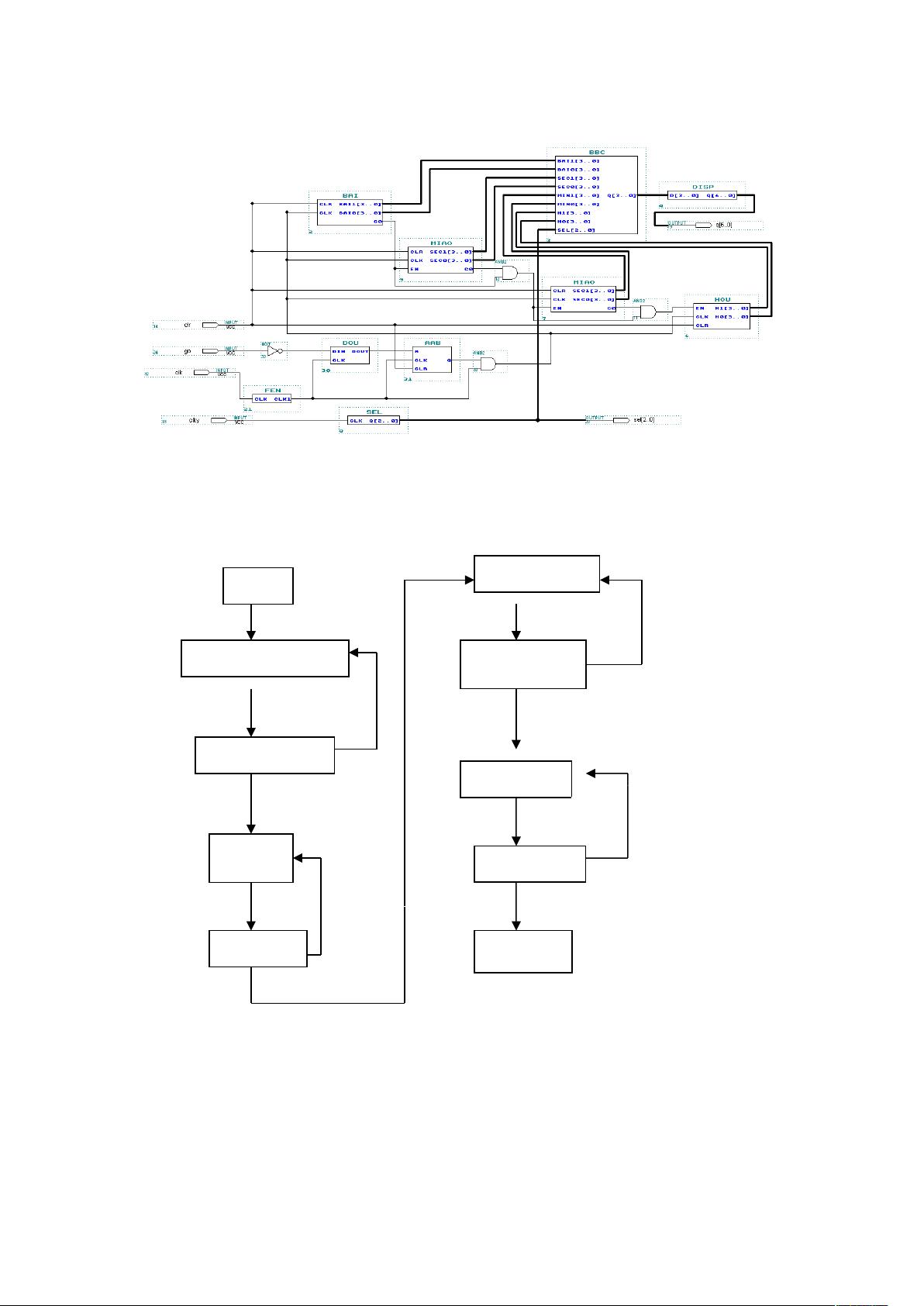

结构原理图:

流程图:在整个流程中,按 clr 信号都会清零,按 go 信号会停止或开始。

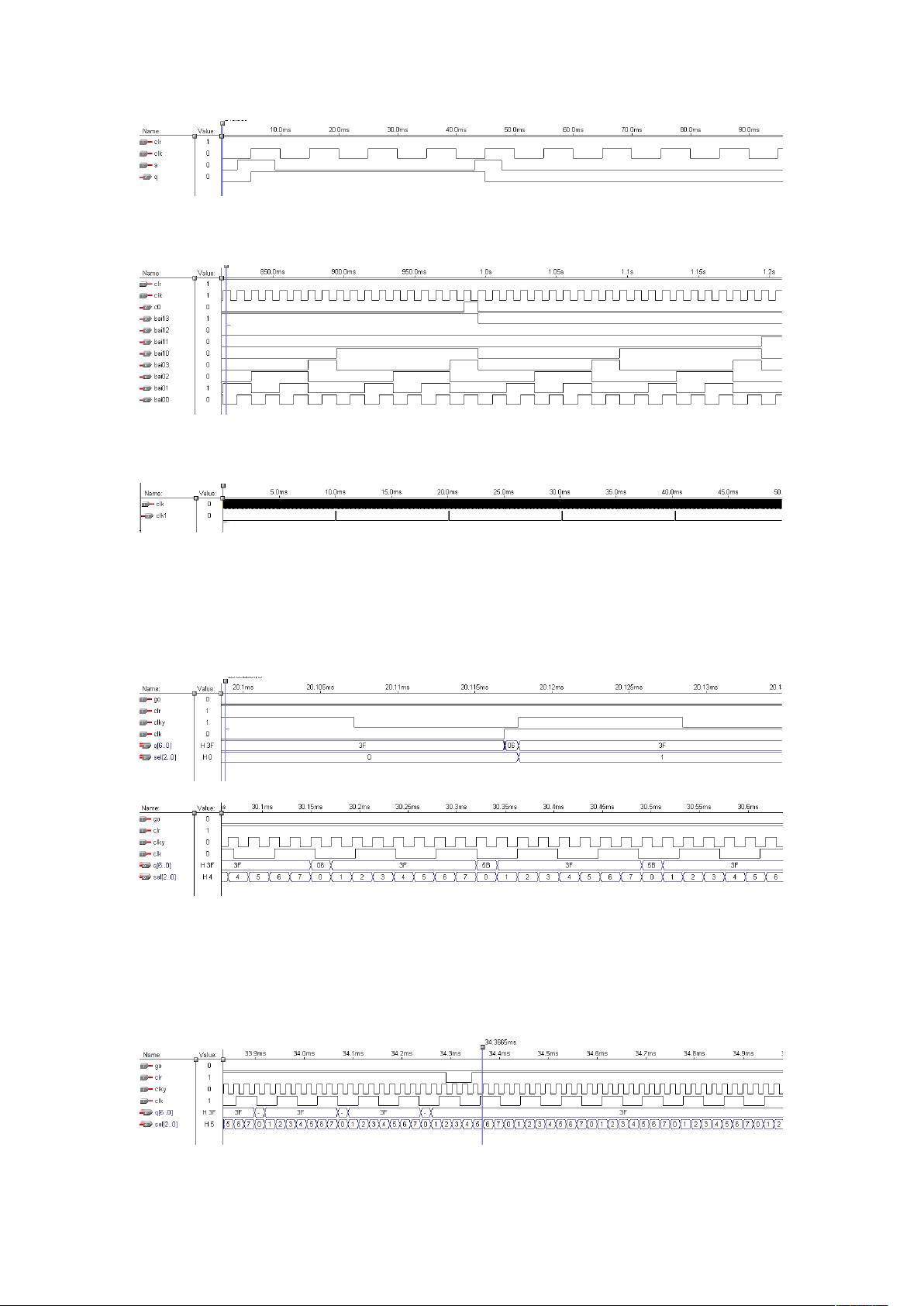

系统仿真:

部分模块仿真:

1、启停模块

开始

ms 自增 10ms

计满 1000ms ?

s 自增 1

计 满

60s ?

h 自增 1

计满 24 ?

初始状态

N

Y

N

NY

Y

Minute 自增 1

Minute 满

60 ?

N

Y

当有一个脉冲时,在时钟是上升沿,输出状态 q 即发生改变。

2、毫秒模块

在 1s 时,计数器 co 进 1 位。60 进制和 24 进制模块同理。

3、分频模块

输入时钟频率 clk 为 12kHz,输出频率为 100Hz(10ms)。

clk 时钟频率为 12kHz,位选时钟频率为 47kHz。go 信号置低电平,由于是低电平清零,所

以 clr 置高电平,在 34.4ms 处给一清零信号。

从以上两图可以知道,在 20.11ms 处,开始有计数(3FH 表示 0,06H 表示 1),数码管

显示 00 00 00 01,在相隔 10ms 左右,即 30.32ms 处,计数增 1(5BH 表示 2),数码管显示

00 00 00 02。

考虑到仿真的时间和速度,只做了 40ms 的仿真,但我们不难从中看出,该系统是以 10ms

为一次计数的。

在 34.4ms 处给一清零信号,此后系统不计数,数码管显示 00 00 00 00。

系统的功能是正确的。

注:这是所有的模块,有些模块可以写上,有些模块也可以不要

要添加一些必要的注释

模块程序:

1、 启停模块

----秒表的启停是通过控制送给计数器的时钟来实现的,当按下启停键后,输出端 Q 的状态

发生反转。

----Q 为‘1'时,时钟可通过与门,秒表计时;Q 为‘0'时,时钟被屏蔽,计数器得不到时钟,

停止计数

library ieee;

use ieee.std_logic_1164.all;

---------------------------------

entity aab is

port(a,clk,clr:in std_logic;

q:out std_logic);

end aab;

---------------------------------

architecture aab_arc of aab is

begin

process(clk)

variable tmp:std_logic;

begin

if clr='0'then tmp:='0'; ---清零,封锁与门

elsif clk'event and clk='1'then

if a='1'then ---当检测到脉冲时

tmp:=not tmp; ---输出低电平,封锁与门

end if;

end if;

q<=tmp;

end process;

end aab_arc;

2、100 进制计数器模块

-----100 进制计数器模块 输出值为 0.01 s和 0.1 s

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;