没有合适的资源?快使用搜索试试~ 我知道了~

vivado fir IP核的使用

温馨提示

Vivado fir IP核的使用手册 内容详细,方便查阅.,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,

资源推荐

资源详情

资源评论

FIR Compiler v7.2

LogiCORE IP Product Guide

Vivado Design Suite

PG149 November 18, 2015

FIR Compiler v7.2 www.xilinx.com 2

PG149 November 18, 2015

Table of Contents

IP Facts

Chapter 1: Overview

Feature Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Licensing and Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Chapter 2: Product Specification

Performance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Resource Utilization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Port Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Chapter 3: Designing with the Core

Clocking. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

AXI4-Stream Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Core Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Input and Output Sample Rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Resource Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Chapter 4: Design Flow Steps

Customizing and Generating the Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

System Generator for DSP. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Constraining the Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Synthesis and Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

Chapter 5: C Model

Unpacking and Model Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

Installation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

C Model Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

MATLAB Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

Dependent Libraries . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

Send Feedback

FIR Compiler v7.2 www.xilinx.com 3

PG149 November 18, 2015

Chapter 6: Test Bench

Demonstration Test Bench . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

Appendix A: Migrating and Upgrading

Migrating to the Vivado Design Suite from ISE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

Upgrading within the Vivado Design Suite. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

Appendix B: Debugging

Finding Help on Xilinx.com . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

Debug Tools . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

Simulation Debug. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

AXI4-Stream Interface Debug . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

Appendix C: Additional Resources and Legal Notices

Xilinx Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

Please Read: Important Legal Notices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

Send Feedback

FIR Compiler v7.2 www.xilinx.com 4

PG149 November 18, 2015 Product Specification

Introduction

The Xilinx® LogiCORE™ IP FIR Compiler core

provides a common interface to generate

highly parameterizable, area-efficient

high-performance FIR filters.

Features

• AXI4-Stream-compliant interfaces

• High-performance finite impulse response

(FIR), polyphase decimator, polyphase

interpolator, half-band, half-band

decimator and half-band interpolator,

Hilbert transform and interpolated filter

implementations

• Support for up to 256 sets of coefficients,

with 2 to 2048 coefficients per set

• Input data up to 49-bit precision

• Filter coefficients up to 49-bit precision

• Support for up to 1024 interleaved data

channels

• Support for advanced interleaved data

channel sequences

• Support for multiple parallel data channels

with shared control logic

• Interpolation and decimation factors of up

to 64 generally and up to 1024 for single

channel filters

• Support for sample frequency greater than

clock frequency

• Online coefficient reload capability

• User-selectable output rounding

• Efficient multi-column structures for all

filter implementations and optimizations

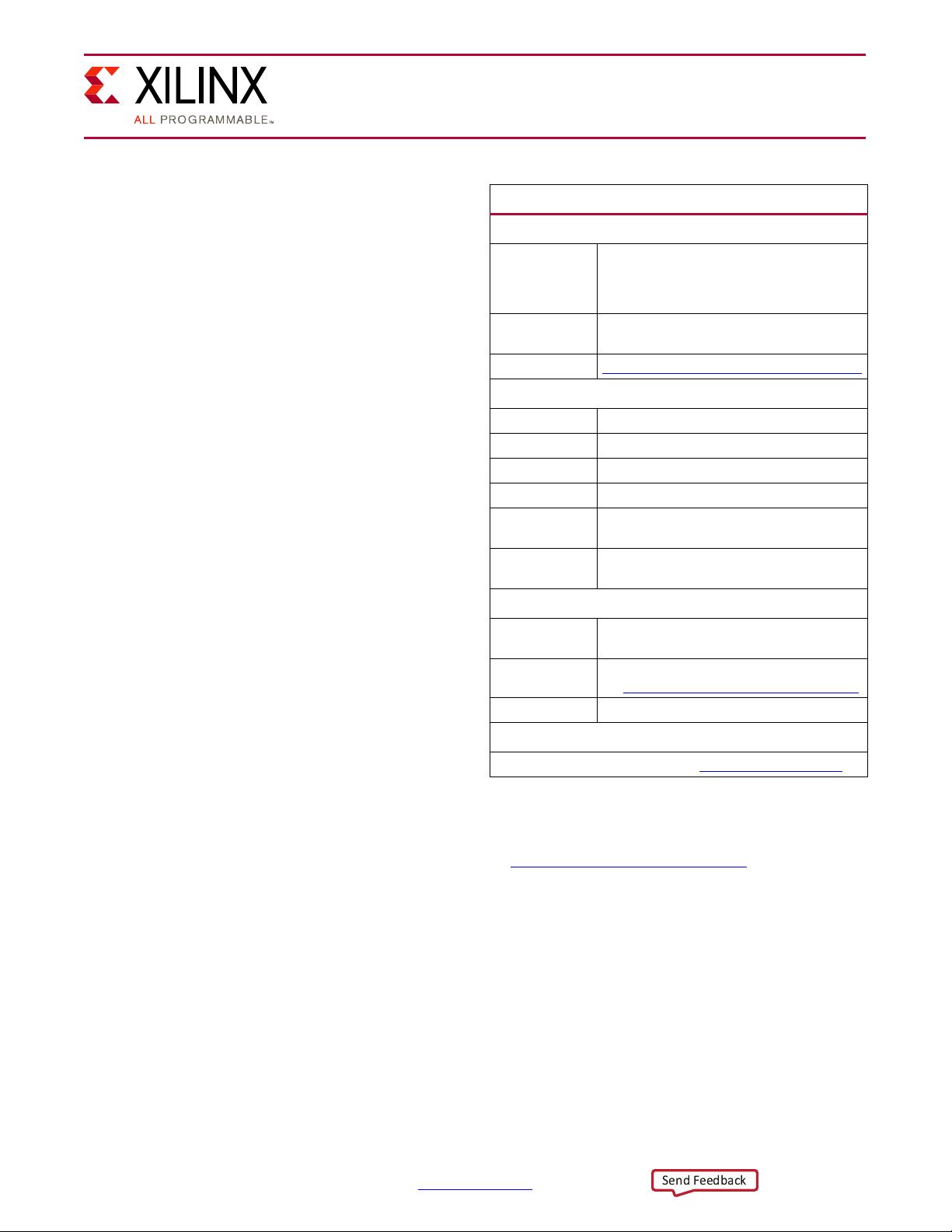

IP Facts

LogiCORE IP Facts Table

Core Specifics

Supported

Device Family

(1)

UltraScale+™ Families

UltraScale™ Architecture

Zynq-7000 All Programmable SoC

7 Series

Supported User

Interfaces

AXI4-Stream

Resources Performance and Resource Utilization web page

Provided with Core

Design Files Encrypted RTL

Example Design Not Provided

Tes t Be nch VHDL

Constraints File Not Provided

Simulation

Model

Encrypted VHDL

Supported

S/W Driver

N/A

Tested Design Flows

(2)

Design Entry

Vivado® Design Suite

System Generator for DSP

Simulation

For supported simulators, see the

X

ilinx Design Tools: Release Notes Guide.

Synthesis Vivado Synthesis

Support

Provided by Xilinx at the at the Xilinx Support web page

Notes:

1. For a complete listing of supported devices, see the Vivado IP

catalog.

2. For the supported versions of the tools, see the

X

ilinx Design Tools: Release Notes Guide.

Send Feedback

FIR Compiler v7.2 www.xilinx.com 5

PG149 November 18, 2015

Chapter 1

Overview

A wide range of filter types can be implemented in the Vivado® Integrated Design

Environment (IDE): single-rate, polyphase decimators and interpolators and half-band

decimators and interpolators. Structure in the coefficient set is exploited to produce

area-efficient FPGA implementations. Sufficient arithmetic precision is employed in the

internal datapath to avoid the possibility of overflow.

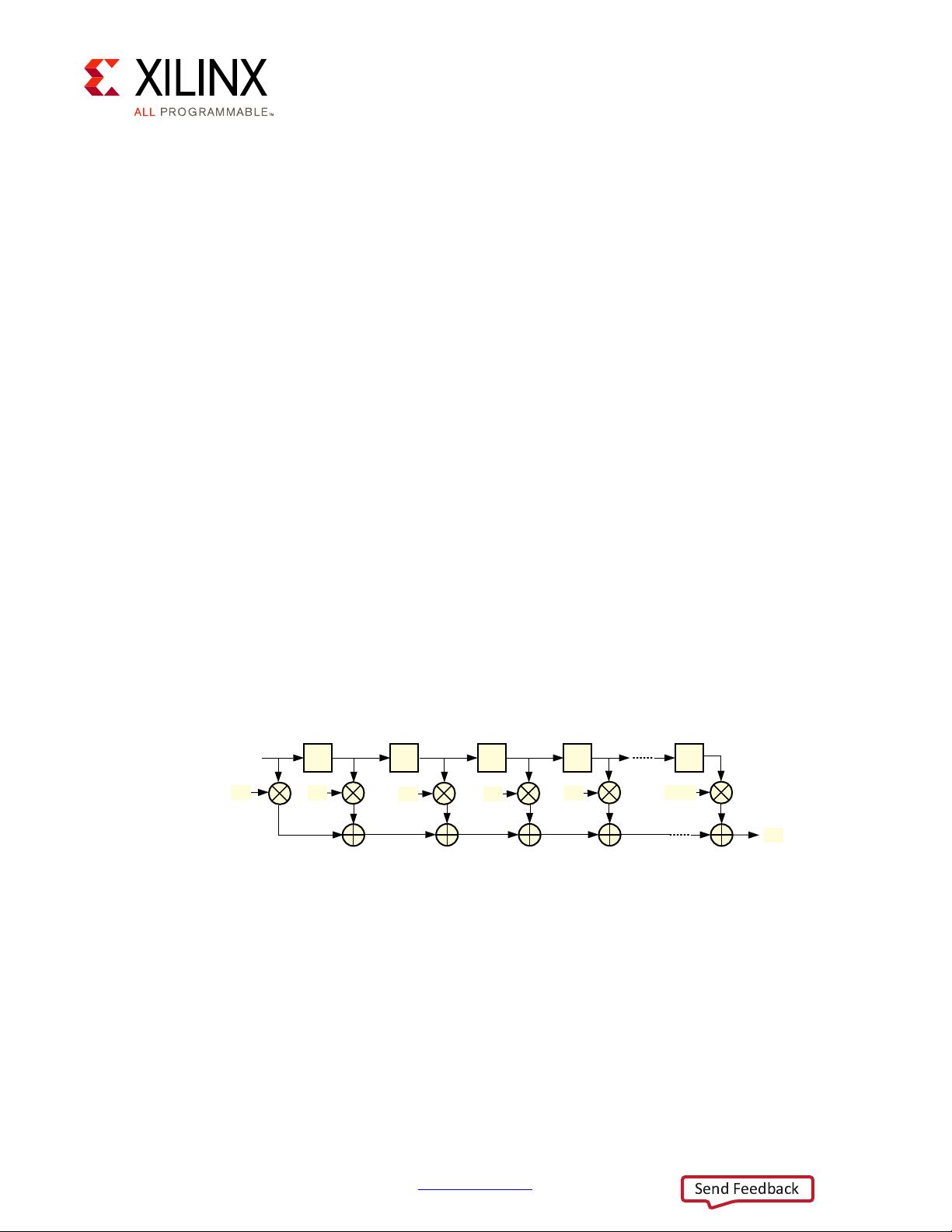

The conventional single-rate FIR version of the core computes the convolution sum defined

in Equation 1-1, where N is the number of filter coefficients.

Equation 1-1

Figure 1-1 shows the conventional tapped delay line realization of this inner-product

calculation, and although the illustration is a useful conceptualization of the computation

performed by the core, the actual FPGA realization is quite different.

One or more time-shared multiply-accumulate (MAC) functional units are used to service

the N sum-of-product calculations in the filter. The core automatically determines the

minimum number of MAC engines required to meet user-specified throughput.

X-Ref Target - Figure 1-1

Figure 1-1: Conventional Tapped Delay Line FIR Filter Representation

yk() an()xk n–()

n 0=

N 1–

= k 01…,,=

=

=

dž;ŶͿ

Ă;ϬͿ

Ă;ϭͿ

Ă;ϮͿ

Ă;ϯͿ

Ă;ϰͿ

=

=

=

Ă;EͲϭͿ

LJ;ŶͿ

Send Feedback

剩余130页未读,继续阅读

资源评论

AshleyK2023-07-26文件结构清晰,每个步骤都有明确的解释和演示代码,使得读者能够轻松跟随并实践。

AshleyK2023-07-26文件结构清晰,每个步骤都有明确的解释和演示代码,使得读者能够轻松跟随并实践。 林祈墨2023-07-26文中给出了一些实用的例子和问题解答,能够帮助读者更好地理解和应用fir IP核。

林祈墨2023-07-26文中给出了一些实用的例子和问题解答,能够帮助读者更好地理解和应用fir IP核。 Xhinking2023-07-26这篇文件虽然简短,但提供了足够的信息和资源,是一个值得推荐的参考文献。

Xhinking2023-07-26这篇文件虽然简短,但提供了足够的信息和资源,是一个值得推荐的参考文献。 基鑫阁2023-07-26这篇文件对于初学者而言非常友好,清晰地介绍了vivado fir IP核的使用方法。

基鑫阁2023-07-26这篇文件对于初学者而言非常友好,清晰地介绍了vivado fir IP核的使用方法。 ask_ai_app2023-07-26文件中详细说明了fir滤波器的原理和实现步骤,对于需要使用该功能的人来说,是一个不错的指导。

ask_ai_app2023-07-26文件中详细说明了fir滤波器的原理和实现步骤,对于需要使用该功能的人来说,是一个不错的指导。

F_laver

- 粉丝: 11

- 资源: 20

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功