用VHDL设计的计数显示电路

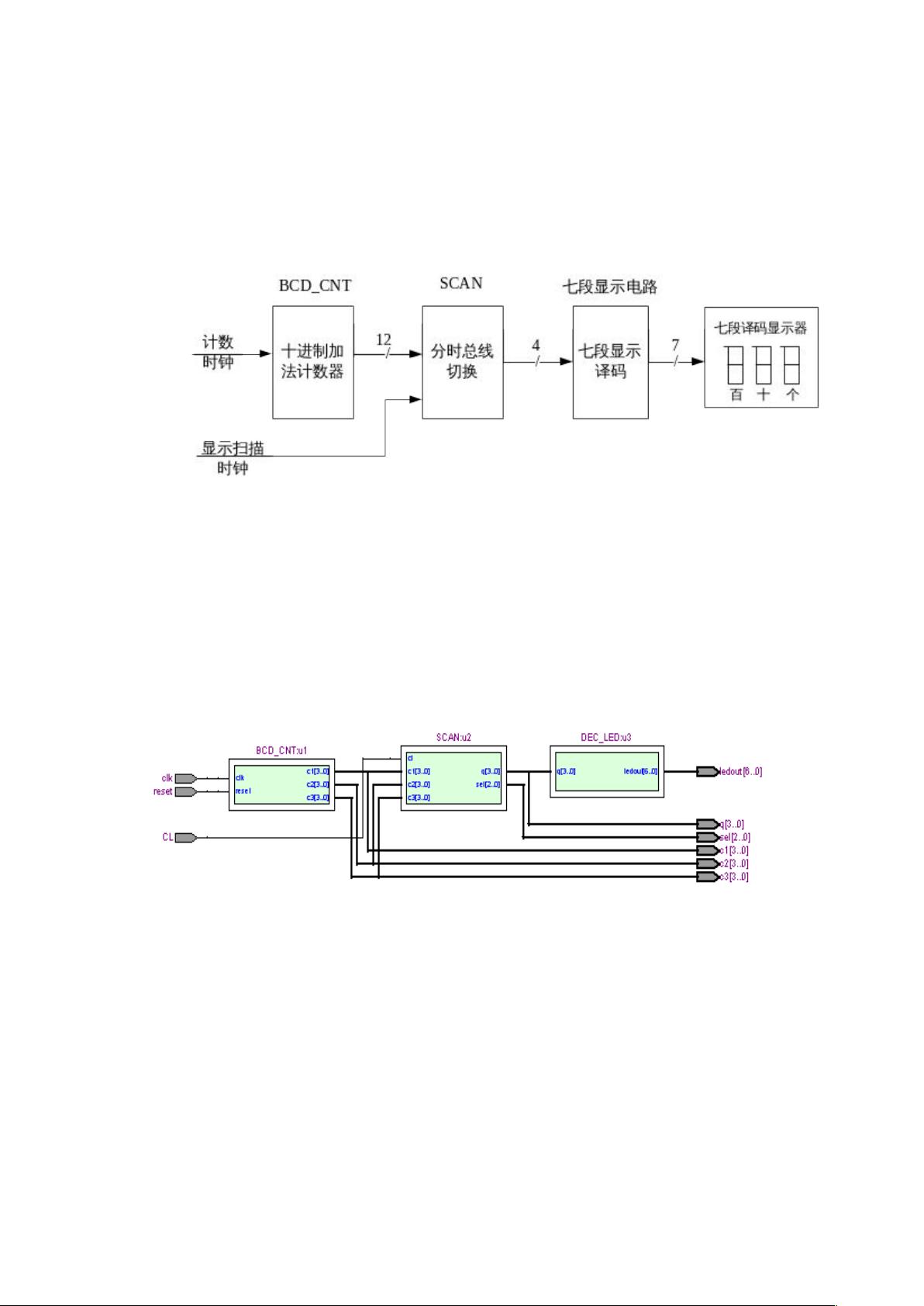

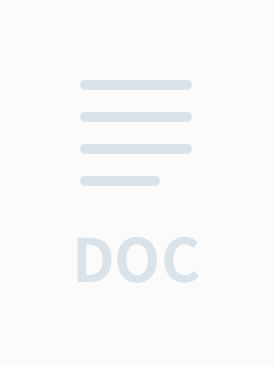

### VHDL设计中的计数显示电路详解 #### 一、设计概述 本设计旨在通过VHDL语言实现一个能够输出3位BCD码的计数显示电路。该电路由三个核心模块组成:十进制计数器(BCD_CNT)、分时总线切换电路(SCAN)以及七段显示译码器电路(DEC_LED)。通过这三个模块协同工作,实现了从0到999的十进制计数,并将计数结果通过LED数码管动态地显示出来。 #### 二、设计原理 ##### 1. 十进制计数器模块(BCD_CNT) 十进制计数器模块负责生成3位BCD码,即从0到999的计数序列。此模块接收一个时钟信号(clk)和一个异步复位信号(reset)。当reset信号为低电平(0)时,计数器清零;当reset信号为高电平(1)且clk信号有上升沿时,计数器增加1。计数器输出三组4位BCD码,分别表示百位(c3)、十位(c2)和个位(c1)。 ##### 2. 分时总线切换电路模块(SCAN) 分时总线切换电路模块的主要功能是对三个LED数码管进行动态扫描,以实现数据的有效显示。此模块同样接收一个时钟信号(CL),并在每个CL信号的上升沿时改变数码管的扫描顺序。具体而言,模块根据CL信号控制一个三位选择信号(sel),以此决定当前被选中的数码管,从而实现动态显示。同时,模块还会输出一个四位信号(q),该信号包含了当前被选中数码管需要显示的BCD码值。 ##### 3. 七段显示译码器电路模块(DEC_LED) 该模块负责将来自SCAN模块的BCD码转换成七段LED数码管所需的驱动信号(ledout)。通过这种方式,BCD码被转换为可以直接驱动LED数码管的信号,从而实现数字的显示。 #### 三、VHDL实现 ##### 1. 顶层模块 顶层模块(top)是整个设计的核心,它负责连接和协调各个子模块。在VHDL代码中,顶层模块声明了所有的输入输出端口,并定义了各个子模块之间的连接方式。具体来说: - 输入端口包括时钟信号(clk)、复位信号(reset)以及用于控制数码管扫描的时钟信号(CL)。 - 输出端口则包含用于显示的数码管选择信号(sel)、七段LED驱动信号(ledout),以及用于调试的计数器输出(c1、c2、c3)和分时输出信号(q)。 此外,代码还定义了三个子模块(BCD_CNT、SCAN、DEC_LED)并指明了它们之间的连接关系。 ##### 2. 子模块设计 - **BCD_CNT模块**:负责实现十进制计数逻辑,其内部细节包括时钟同步的计数机制以及BCD码的生成等。 - **SCAN模块**:主要实现数码管的分时扫描逻辑,确保各个数码管能够按照正确的顺序被点亮。 - **DEC_LED模块**:完成BCD码到七段LED驱动信号的转换,使得数字可以正确地显示在LED数码管上。 #### 四、总结 本设计利用VHDL语言实现了从计数到显示的完整流程,不仅展示了VHDL语言的强大功能,同时也为理解和学习数字电路设计提供了一个很好的范例。通过对各个模块的具体分析,我们可以深入了解如何使用VHDL来实现复杂的数字系统设计。

剩余6页未读,继续阅读

- 粉丝: 0

- 资源: 3

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- AI数据集生成20231221

- 手机电池用PCM焊接机sw18可编辑全套技术资料100%好用.zip

- 双工位贴易撕贴胶纸设备sw18全套技术资料100%好用.zip

- 手机锂电池长宽厚尺寸测量设备sw18可编辑全套技术资料100%好用.zip

- 手机主板插拔耐压测试sw17可编辑全套技术资料100%好用.zip

- 糖果生产输送线sw18全套技术资料100%好用.zip

- 铜线切断机sw18可编辑全套技术资料100%好用.zip

- 双工位自动浇筑机(含DFM)sw18可编辑全套技术资料100%好用.zip

- 凸轮(ppu)机械手全套技术资料100%好用.zip

- shacesrric0101.zip

- 梁烨炜网页期末作业.zip

- 桶提手成型组装设备sw20可编辑全套技术资料100%好用.zip

- 微型断路器保险丝组装设备(含DFM)sw17可编辑全套技术资料100%好用.zip

- 物料储存机sw18可编辑全套技术资料100%好用.zip

- usb开发资料linux

- 机器学习中决策树练习数据

信息提交成功

信息提交成功

- 1

- 2

前往页