没有合适的资源?快使用搜索试试~ 我知道了~

Part A2 SD Host Controller Standard Specification Ver3

温馨提示

试读

161页

配合SD Physical Layer Specification Version 3.00所做的host controller specification,包括了3.0版本所有新加功能。

资源推荐

资源详情

资源评论

AMD, Inc

Downloaded by Suki Xu AMD, Inc on 01/11/2010

SD Specifications

Part A2

SD Host Controller

Standard Specification

Version 3.00 Draft 1.00

November 9, 2009

Technical Committee

SD Association

AMD, Inc

Downloaded by Suki Xu AMD, Inc on 01/11/2010

©Copyright 2002-2009 SD Association

SD Host Controller Standard Specification Version 3.00 Draft 1.00

Confidential

i

Draft Only Page

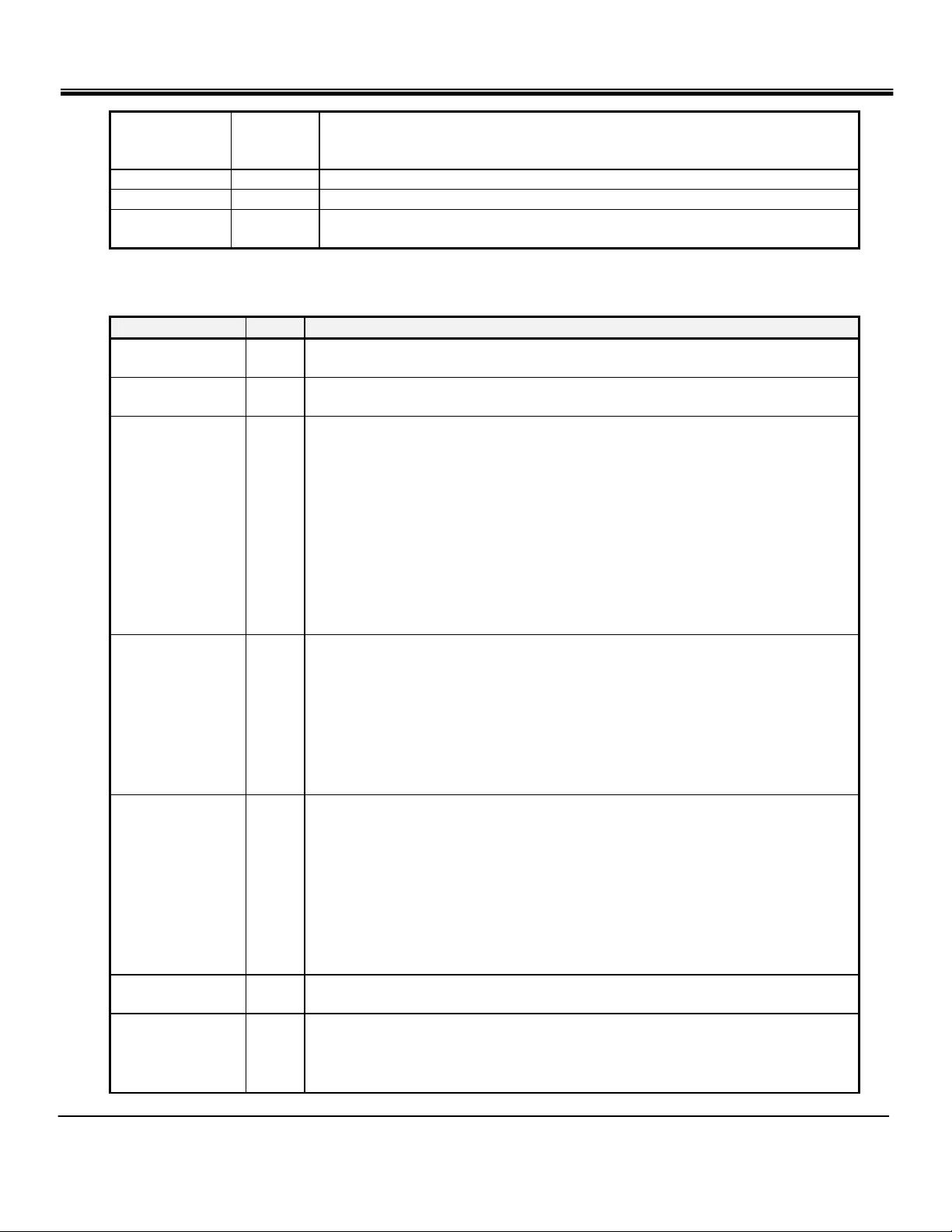

Draft Revision History for Version 2.00

Date Version Changes compared to previous issue

July 29, 2005 2.00 Add following features and register sets

contents which are described in the SD Host ver1.00 Supplementary

Note

ADMA (Advanced DMA)

Test Register

Force Event Register for Error Interrupt Status

Force Event Register for Auto CMD12 Error Status

ADMA Error Status Register

ADMA System Address Register

Modify (Update) following register sets

Host Control Register

Error Interrupt Status Register

Error Interrupt Status Enable Register

Error Interrupt Signal Enable Register

Capabilities Register

Host Controller Version Register

Add following sequence

SD Transaction Generation (Using ADMA)

High Speed Mode Setting

Sep. 17, 2005 1st Adding explanation for ADMA

Adding internal ADMA register (ADMA Data Length Register, ADMA Data

Address Register)

Adding explanation for the test register in the Host Control Register

Removing the description for MMC 8 bit

April 12, 2006 2nd Add High Capacity initialization sequence. Switching bus speed mode.

miniSD adaptor issue.

July 13, 2006 3rd Modify ADMA Specification.

July 24, 2006 3rd Typos fixed. Explanation of Stop At Block Gap Request is changed.

Aug. 1, 2006 3rd Command with busy is not explained in DAT Line Active and Transfer

Complete. Modify explanation of Auto CMD12 Error Interrupt.

Final draft release from WG,TG

Aug. 10 2006 4th Clean up 3rd changes.

Add Force Event and ADMA register in Section 1.2.

R7 is added in Table 2-10.

SDIO initialization (CMD5) is added in Section 3.6.

Wide figures are fitted to sheet width.

Aug. 25, 2006 5th Typo fixed. (Spell check is performed but fixed word is not marked.)

Some sentences are changed and indicated by orange

DMA is changed to SDMA if it refers to only SDMA.

(Section 1.4 and others)

Field names and register names related to SDMA are changed.

SDMA Support, Host SDMA Buffer Boundary etc.

Add explanation to Buffer Write Enable that the controller should not

AMD, Inc

Downloaded by Suki Xu AMD, Inc on 01/11/2010

©Copyright 2002-2009 SD Association

SD Host Controller Standard Specification Version 3.00 Draft 1.00

Confidential

ii

issue interrupt after the last block data written.

Change flow chart of Using ADMA. (DMA int is changed to AMDA Error)

Appendix B.2 is changed.

Sep. 1, 2006 2.00 Final draft for TC Review

Sep. 26, 2006 2.00 Final draft for IP Review

Oct. 10, 2006 2.00 Final draft for IP Review

Table 1-10 is fixed to indicate 16-bit length.

Draft Revision History for Version 3.00

Date Draft Changes compared to previous issue

Feb. 23, 2009 Draft

0.30

The first draft for Version 3.00

Feb. 26, 2009 Draft

0.40

First draft for review

Mar. 19, 2009 Draft

0.41

• Preset Value Enable is moved to Host Control 2 register

• Asynchronous Interrupt Enable is changed to Bit14.

• A bit "Shared Bus Slot" is changed to 2-bit "Slot Type".

• SDMA Address is extended for 32-bit Block Count for CMD23

• Previous "Block Count" is changed to "16-bit Block Count"

• Auto CMD23 is added in Transfer Mode register

• Auto CMD23 error is indicated to Auto CMD Error Status register.

• The name "Auto CMD12" is changed to "Auto CMD" if it is also used for

Auto CMD23.

• Table 2-42 : Preset Value Register Select Condition is changed

• Host Controller Version 3.00 is added

Apr. 9, 2009 Draft

0.42

• P19 Explanation for Block Count is added in Section 1.15.

• P28 Explanation of Auto CMD23 Enable is changed

• P79 XPC control method is described in Maximum Current Capabilities

• P87 Back-End Power Control is added to Shared Bus Control Register

• P89 Implementation Note for Lock-Reset is added

• Section 3.6 Card Initialization and Identification is fixed.

• Section 3.6.1 Signal Voltage Switch Procedure is added.

• Section 3.9 Bus Speed Mode Selection is fixed.

Apr. 14, 2009 Draft

0.43

• Rename 32-bit Block Count to "Argument 2"

• Remove "16-bit" from "16-bit Block Count"

• "Argument" register is changed to "Argument 1" register

• Table 1-1 is fixed (ADMA is added, Argument 1 and Argument 2)

• Re-tuning Request is added in the Present State register

• P74 Explanation regarding tuning is fixed.

• "Preset Values" is changed to "Preset Value".

• P89 Implementation Note for Lock-Reset is fixed

• Section 3.9 "EHS and EUHS[2:0]" is changed to "EHS or EUHS[2:0]".

Apr. 14, 2009 Draft

0.50

The first draft for TG review

Apr. 27, 2009 Draft

0.51

Feedback from Atheros is applied.

• Wordings are improved for better understandings.

• Section 1.7.4 is removed

• Section 1.8 clearing Card Interrupt Status Enable

AMD, Inc

Downloaded by Suki Xu AMD, Inc on 01/11/2010

©Copyright 2002-2009 SD Association

SD Host Controller Standard Specification Version 3.00 Draft 1.00

Confidential

iii

• Appendix C.4 Device State is changed for async. int support.

• Appendix C.4 Device State for embedded device is added.

• Section 2.2.15 Implementation Note is added for timeout.

May 11, 2009 Draft

0.52

• Figure 1-2 is modified and Table 1-1 is added (following Tables in Section

1 are re-numbered)

• Section1.3 and Figure 1-3 are fixed.

• Re-Tuning Event is added to Table 2-15 Re-Tuning Request.

• Re-Tuning Event is added to Normal Interrupt registers

May 18, 2009 Draft

0.53

• Figure 1-1 and below explanation are fixed.

• Table 2-32 1.8V Signaling Enable is cleared by host controller fails.

• Table 2-32 explanation for Read Wait is changed.

• Step (4) and (8) are added in Figure 3-10 and explanation below.

• Fix completion status to 1111b in Figure 3-10 and explanation below.

May 19, 2009 Draft

0.60

Draft for TG review

June 11, 2009 Draft

0.61

• Wording and typos are fixed (Page 19,20,28,45,61,71,75,87,89)

• Page37 Explanation for Re-Tuning Request is changed.

• Page39 Explanation is added for Auto CMD12 and Auto CMD23

• Page56 Explanation is added for Auto CMD12 and Auto CMD23

• Page73 Explanation for re-tuning is removed.

• Page74 Clock Multiplier field is moved

• Page74 New capabilities are added to bit 42-40

• Page103 Exchange step (3) and (4)

June 24, 2009 Draft

0.62

Clear condition of Re-Tuning Request is added.

3 fields are modified in Capabilities register

• Timer Count for Re-Tuning (add a new field)

• Use Re-Tuning Request During Non Data Transfer

(Rename of Use Re-Tuning Timer)

• Use Re-Tuning Request During Data Transfer

Page 53 and 54 table is added in INT_A, INT_B, INT_C

Example of Shared Bus Host Controller is added in Appendix D

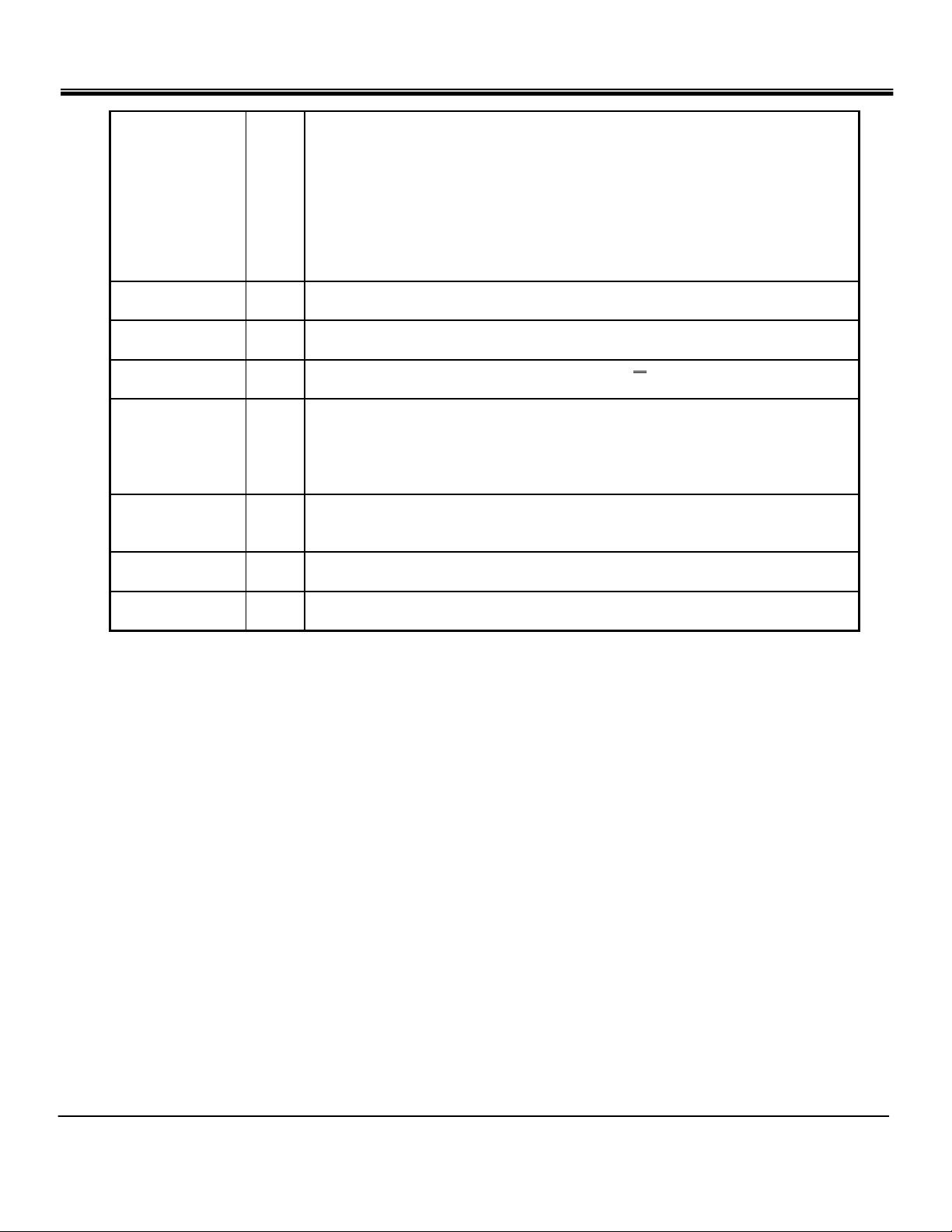

July 21, 2009 Draft

0.63

Page7 Section 1.7.4 is removed.

Page18 Explanation of Sampling Clock Tuning is changed

Page36 Explanation of Re-Tuning Request is changed.

Page56 Explanation is added in Tuning Error.

Page58 Tuning Error interrupt is added

Page63 Tuning Error Status Enable is added.

Page67 Tuning Error Signal Enable is added.

Page70 Explanation of Sampling Clock Select is changed.

Page72 Figure 2-29 is fixed. Explanation below Figure 2-29 is changed.

Page73 Re-Tuning Modes in Capabilities is added.

Page74 Fields assignments in Capabilities are changed.

August 4, 2009 Draft

0.64

Section 1.2: A sentence is added.

Section 1.4: Remove description regarding infinite transfers

Capabilities Update

(1) Explanation is added to bit 20

(2) Re-Tuning Modes is changed

(3) Timer Count for Re-Tuning assignment is changed.

Some editorial changes are applied.

August 12, 2009 Draft

0.70

Page3 Typo is fixed in Section 1.4

Page33 Missing Re-Tuning Request in Fig2-9 is fixed

AMD, Inc

Downloaded by Suki Xu AMD, Inc on 01/11/2010

©Copyright 2002-2009 SD Association

SD Host Controller Standard Specification Version 3.00 Draft 1.00

Confidential

iv

Page40 Explanation of Extended Data Transfer Width is added.

Page73 Missing section number of Capabilities register is fixed.

Page73 Shared Bus Slot is changed to Slot Type in Figure 2-30

Page73 D18 "for eSD" is changed to "for Embedded Device"

Page74 Explanation of Re-Tuning Modes is changed.

Page81 A line is fixed in Figure 2-32

Page86 A line is fixed in Figure 2-36

Page88 Bus Width Preset is added in Shared Bus register

Page88 Bit assignment is changed in Shared Bus register

Sep. 3, 2009 Draft

0.71

Page 73: The definition of Re-Tuning Modes is changed.

Page 75: The definition of Timer Count for Re-Tuning is changed.

October 1, 2009 Draft

0.80

Typos are fixed.

As Physical Ver3.01 will be released, Physical Version 3.0x is used.

October 1, 2009 Draft

0.90

Clean up all the deleted sentences by using .

Oct. 22, 2009 Draft

0.91

The candidate of the final draft.

Typos are fixed. ("Refer to", "Section xxx")

P10,P12,P26,P34,P38,P42,P57,P78, P145

The other typos fixed: P40,P98,P104

Section 2.2.27 and 2.2.28 are exchanged.

Oct. 22, 2009 Draft

0.92

The Final Draft

C 3.2: Refer to C.3.3 Slot Information Register (C.3.3 is moved)

INT# is removed from eSD in Figure D-1

Oct. 22, 2009 Draft

1.00

Draft for TC Review

Nov. 9, 2009 Draft

1.00

Draft for IP Review

剩余160页未读,继续阅读

hongye299

- 粉丝: 2

- 资源: 28

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- Screenshot_20240427_031602.jpg

- 网页PDF_2024年04月26日 23-46-14_QQ浏览器网页保存_QQ浏览器转格式(6).docx

- 直接插入排序,冒泡排序,直接选择排序.zip

- 在排序2的基础上,再次对快排进行优化,其次增加快排非递归,归并排序,归并排序非递归版.zip

- 实现了7种排序算法.三种复杂度排序.三种nlogn复杂度排序(堆排序,归并排序,快速排序)一种线性复杂度的排序.zip

- 冒泡排序 直接选择排序 直接插入排序 随机快速排序 归并排序 堆排序.zip

- 课设-内部排序算法比较 包括冒泡排序、直接插入排序、简单选择排序、快速排序、希尔排序、归并排序和堆排序.zip

- Python排序算法.zip

- C语言实现直接插入排序、希尔排序、选择排序、冒泡排序、堆排序、快速排序、归并排序、计数排序,并带图详解.zip

- 常用工具集参考用于图像等数据处理

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

- 1

- 2

- 3

前往页