没有合适的资源?快使用搜索试试~ 我知道了~

SerDes知识详解一、SerDes的作用.pdf

1.该资源内容由用户上传,如若侵权请联系客服进行举报

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

版权申诉

0 下载量 33 浏览量

2023-11-12

08:36:09

上传

评论

收藏 3.69MB PDF 举报

温馨提示

试读

26页

SerDes知识详解一、SerDes的作用.pdf

资源推荐

资源详情

资源评论

SerDes 知识详解

一、 SerDes 的作用

1.1 并行总线接口

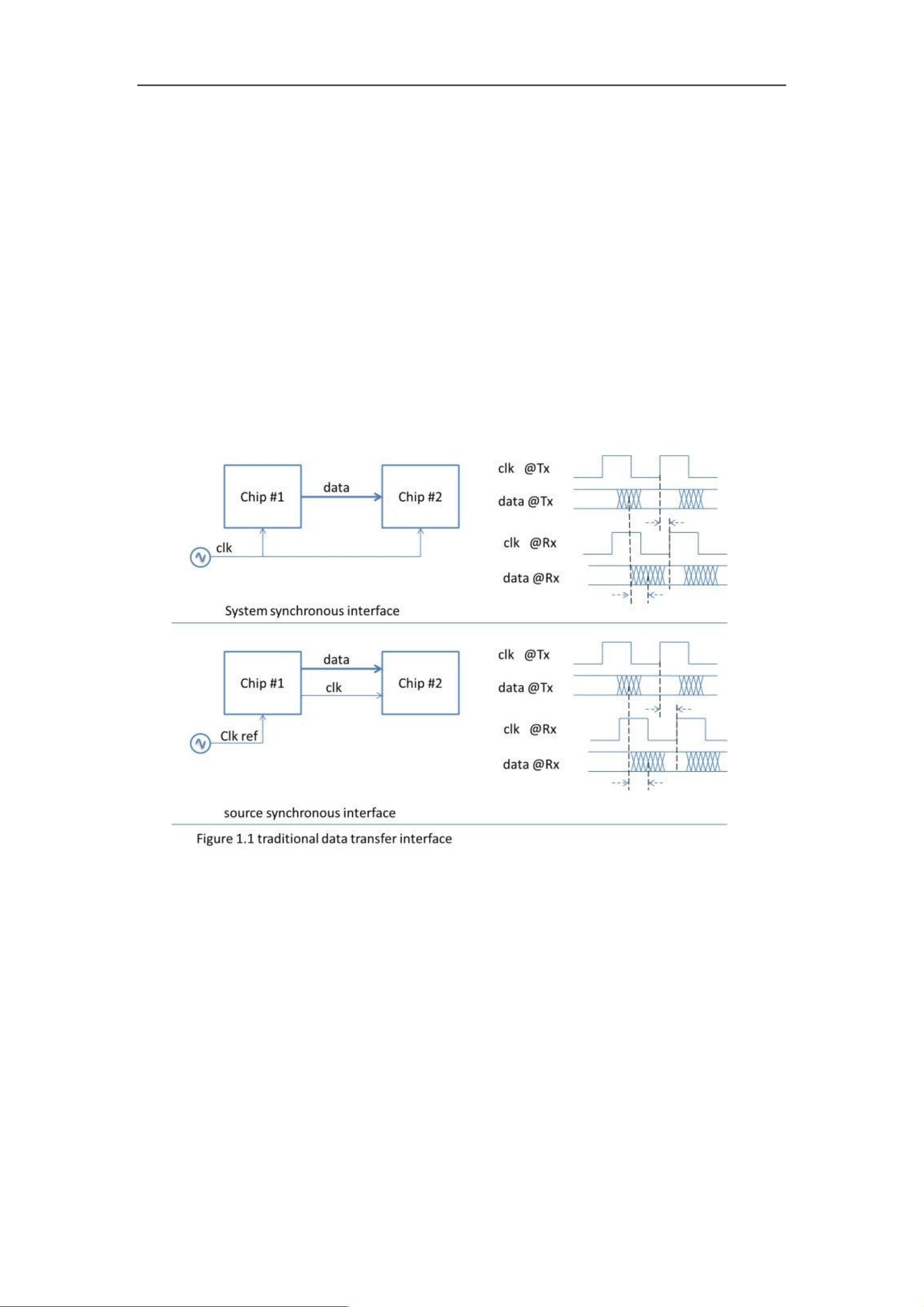

在 SerDes 流行之前 ,芯片之间的互联通过 系统同步或者源同步的并行接口传输数据 ,图

1.1 演示了系统和源同步并行接口。

随着接口频率的提高,在系统同步接口方式中 ,有几个因素限制了有效数据窗口宽度的

继续增加。

时钟到达两个芯片的传播延时不相等 (clock skew)

并行数据各个 bit 的传播延时不相等 (data skew)

时钟的传播延时和数据的传播延时不一致 (skew between data and clock)

虽然可以通过在目的芯片 (chip #2)内用 PLL 补偿时钟延时差 (clock skew),但是 PVT 变化

时,时钟延时的变化量和数据延时的变化量是不一样的。这又进一步恶化了数据窗口。

源同步接口方式中, 发送侧 Tx 把时钟伴随数据一起发送出去 , 限制了 clock skew 对有效

数据窗口的危害 。通常在发送侧芯片内部, 源同步接口把时钟信号和数据信号作一样的处理,

也就是让它和数据信号经过相同的路径,保持相同的延时。这样 PVT 变化时,时钟和数据

会朝着同一个方向增大或者减小相同的量,对 skew 最有利。

我们来做一些合理的典型假设,假设一个 32bit 数据的并行总线,

a)发送端的数据 skew = 50 ps ---很高的要求

b)pcb 走线引入的 skew = 50ps ---很高的要求

c)时钟的周期抖动 jitter = +/-50 ps ---很高的要求

d)接收端触发器采样窗口 = 250 ps ---Xilinx V7 高端器件的 IO 触发器

可以大致估计出并行接口的最高时钟 = 1/(50+50+100+250) = 2.2GHz (DDR)或者 1.1GHz

(SDR)。

利用源同步接口,数据的有效窗口可以提高很多。通常频率都在 1GHz 以下。在实际应

用中可以见到如 SPI4.2 接口的时钟可以高达 DDR 700MHz x 16bits 位宽。DDR Memory 接口也

算一种源同步接口,如 DDR3 在 FPGA 中可以做到大约 800MHz 的时钟。

要提高接口的传输带宽有两种方式,一种是提高时钟频率,一种是加大数据位宽。那么

是不是可以无限制的增加数据的位宽呢?这就要牵涉到另外一个非常重要的问题-----同步开

关噪声(SSN)。

这里不讨论 SSN 的原理,直接给出 SSN 的公式: SSN = L *N* di/dt。

L 是芯片封装电感,N 是数据宽度,di/dt 是电流变化的斜率。

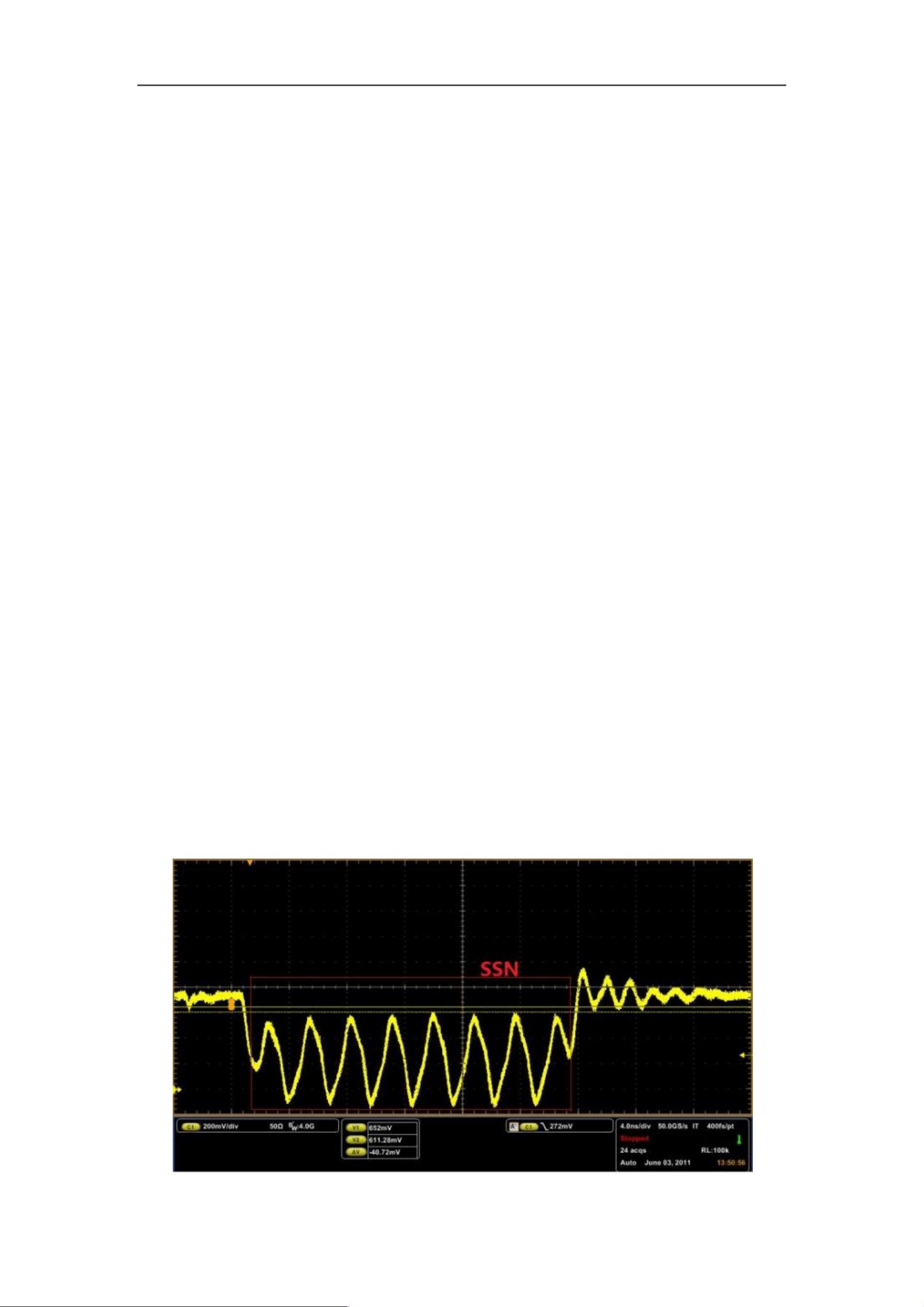

随着频率的提高,数据位款的增加,SSN 成为提高传输带宽的主要瓶颈。图 1.2 是一个

DDR3 串扰的例子。图中低电平的理论值在 0V,由于 SSN 的影响,低电平表现为震荡,震荡

噪声的最大值达 610mV,因此噪声余量只有 1.5V/2-610mV=140mV。

Figure 1.2 DDR3 串扰演示

因此也不可能靠无限的提高数据位宽来继续增加带宽。一种解决 SSN 的办法是使用差

分信号替代单端信号,使用差分信号可以很好的解决 SSN 问题,代价是使用更多的芯片引

脚。使用差分信号仍然解决不了数据 skew 的问题,很大位宽的差分信号再加上严格的时序

限制,给并行接口带来了很大的挑战。

1.2 SerDes 接口

源同步接口的时钟频率已经遇到瓶颈, 由于信道的非理想 (channel)特性, 再继续提高频

率,信号会被严重损伤,就需要采用均衡和数据时钟相位检测等技术。这也就是 SerDes 所

采用的技术。 SerDes(Serializer-Deserializer)是串行器和解串器的简称。串行器 (Serializer)也称

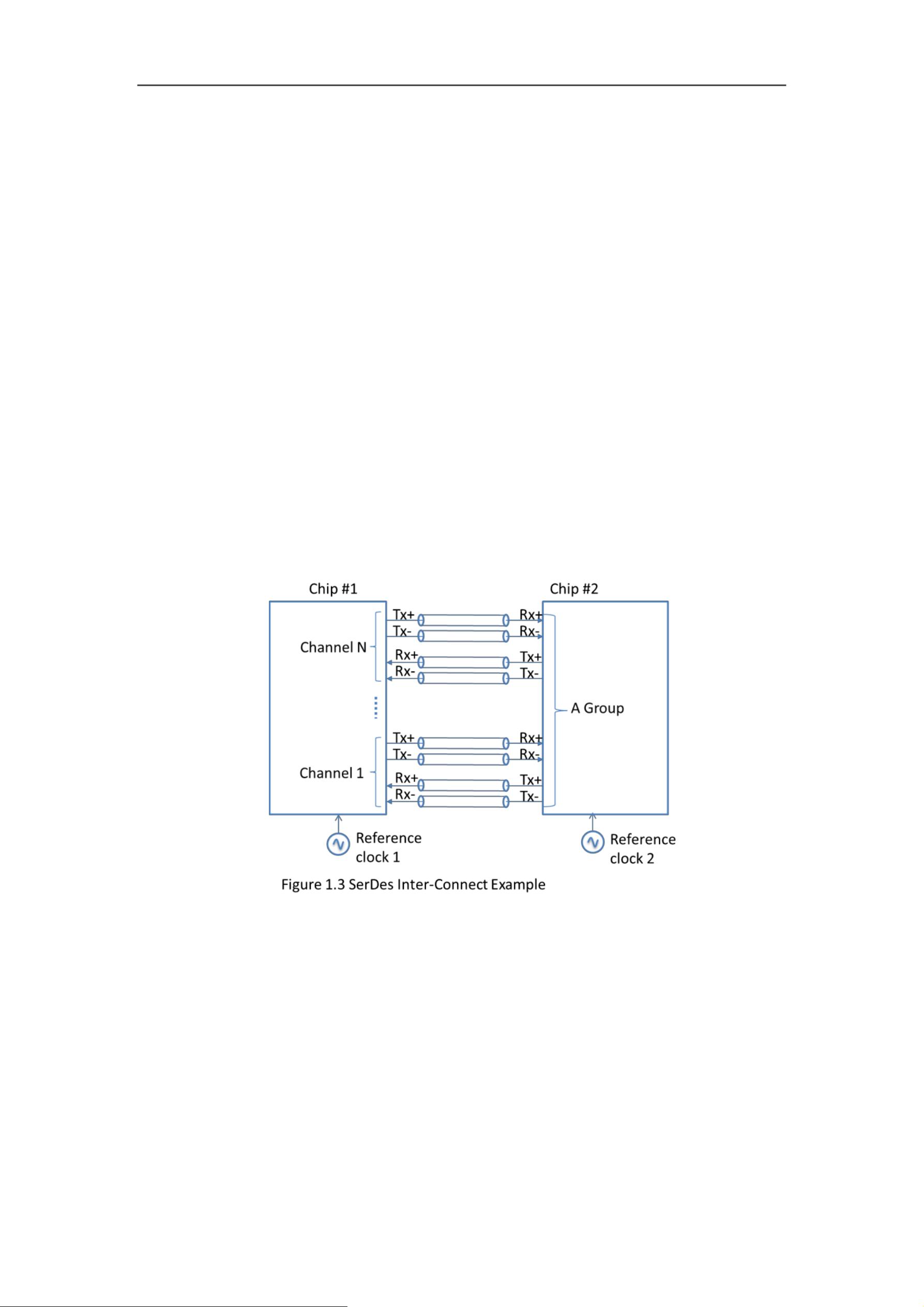

为 SerDes 发送端 (Tx), (Deserializer)也称为接收端 Rx。 Figure1.3 是一个 N 对 SerDes 收发通道

的互连演示 ,一般 N 小于 4。

可以看到, SerDes 不传送时钟信号,这也是 SerDes 最特别的地方, SerDes在接收端集

成了 CDR(Clock Data Recovery)电路,利用 CDR从数据的边沿信息中抽取时钟,并找到最

优的采样位置。

SerDes采用差分方式传送数据。一般会有多个通道的数据放在一个 group 中以共享 PLL

资源,每个通道仍然是相互独立工作的。

SerDes需要参考时钟(Reference Clock),一般也是差分的形式以降低噪声。接收端 Rx

和发送端 Tx 的参考时钟可以允许几百个 ppm 的频差 (plesio-synchronous system),也可以是

同频的时钟,但是对相位差没有要求。

作个简单的比较,一个 SerDes 通道 (channel)使用 4 个引脚 (Tx+/-,Rx+/-), 目前的 FPGA 可

以做到高达 28Gbps。而一个 16bits 的 DDR3-1600 的线速率为 1.6Gbps*16 = 25Gbps,却需要

50 个引脚。此对比可以看出 SerDes 在传输带宽上的优势。

相比源同步接口, SerDes 的主要特点包括 :

SerDes在数据线中时钟内嵌,不需要传送时钟信号。

SerDes通过加重/均衡技术可以实现高速长距离传输,如背板。

SerDes 使用了较少的芯片引脚

1.3 中间类型

也存在一些介于 SerDes 和并行接口之间的接口类型,相对源同步接口而言,这些中间

类型的接口也使用串行器 (Serializer)解串器 (Deserializer),同时也传送用于同步的时钟信号。

这类接口如视频显示接口 7:1 LVDS 等。

二、 SerDes 结构(architecture)

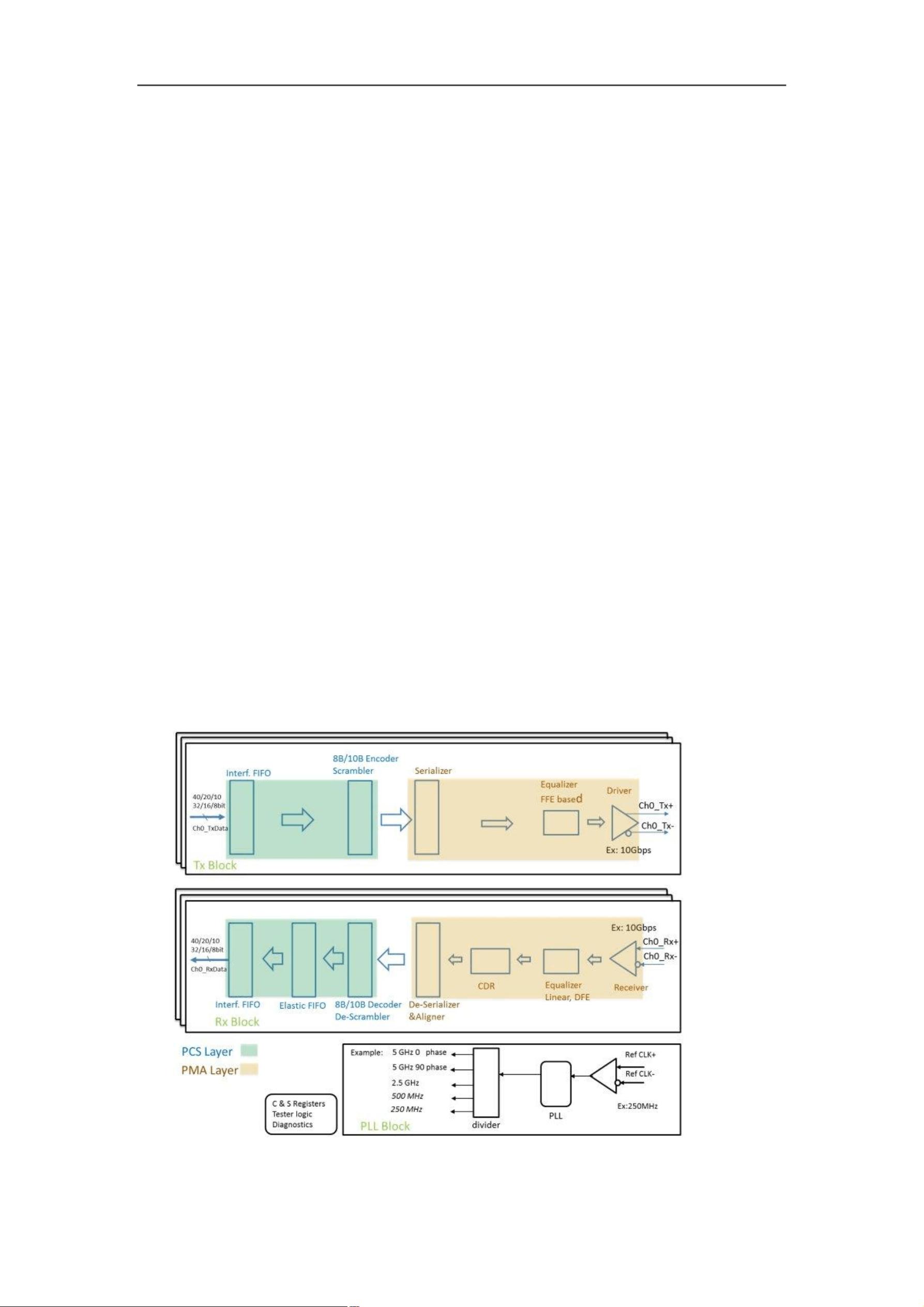

SerDes 的主要构成可以分为三部分, PLL 模块, 发送模块 Tx,接收模块 Rx。为了方便维

护和测试,还会包括控制和状态寄存器,环回测试, PRBS 测试等功能。见图 2.1。

Figure 2.1 Basic Blocks of a typical SerDes

剩余25页未读,继续阅读

资源评论

hhappy0123456789

- 粉丝: 59

- 资源: 5万+

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功