没有合适的资源?快使用搜索试试~ 我知道了~

资源推荐

资源详情

资源评论

沈阳理工大学课程设计

1 十三进制同步减法计数(无效状态为 0001、0010、0011)的

设计

1.1 课程设计的目的:

1、了解同步计数器的工作原理和逻辑功能。

2、掌握计数器电路的分析、设计方法及应用。

3、熟悉设计过程和边沿 JK 触发器原理。

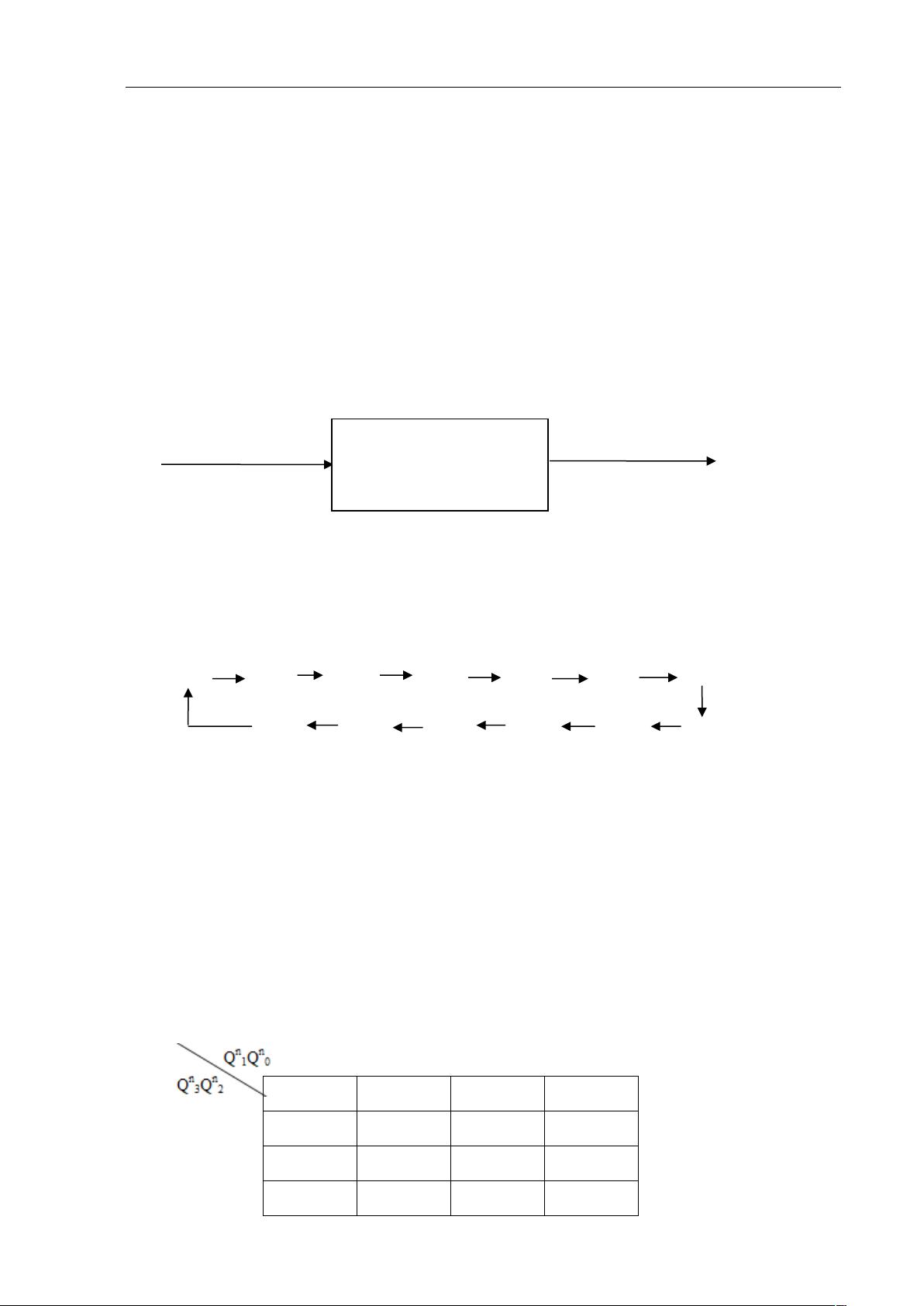

1.2 设计总框图:

CP

输入减法计数器脉冲 输出进位信号

1.3 设计过程:

1.3.1、状态图:

/ 0 / 0 / 0 / 0 / 0 / 0

1 1 1 1 1 1 1 0 1 1 0 1 1 1 0 0 1 0 1 1 1 0 1 0 1 0 0 1

/ 0

0 0 0 0 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0

/ 1 / 0 / 0 / 0 / 0 / 0

1.3.2、 选择触发器、求时钟方程、输出方程和状态方程

(1)选择触发器

由于 JK 触发器功能齐全、使用灵活,故选用 4 个下降沿出发的边沿 JK 触发器。

(2)求时钟方程

CP

0

=CP

1

=CP

2

=CP

3

=CP

( 3 ) 求输出方程

输出方程的卡诺图为:

00 01 11 10

00

01

11

10

1

1 × × ×

0 0 0 0

0 0 0 0

0 0 0 0

十三进制同步减法计数器

8421 BCD 码

沈阳理工大学课程设计

输出方程: Y = Q

n

3

Q

n

2

(4)状态方程:

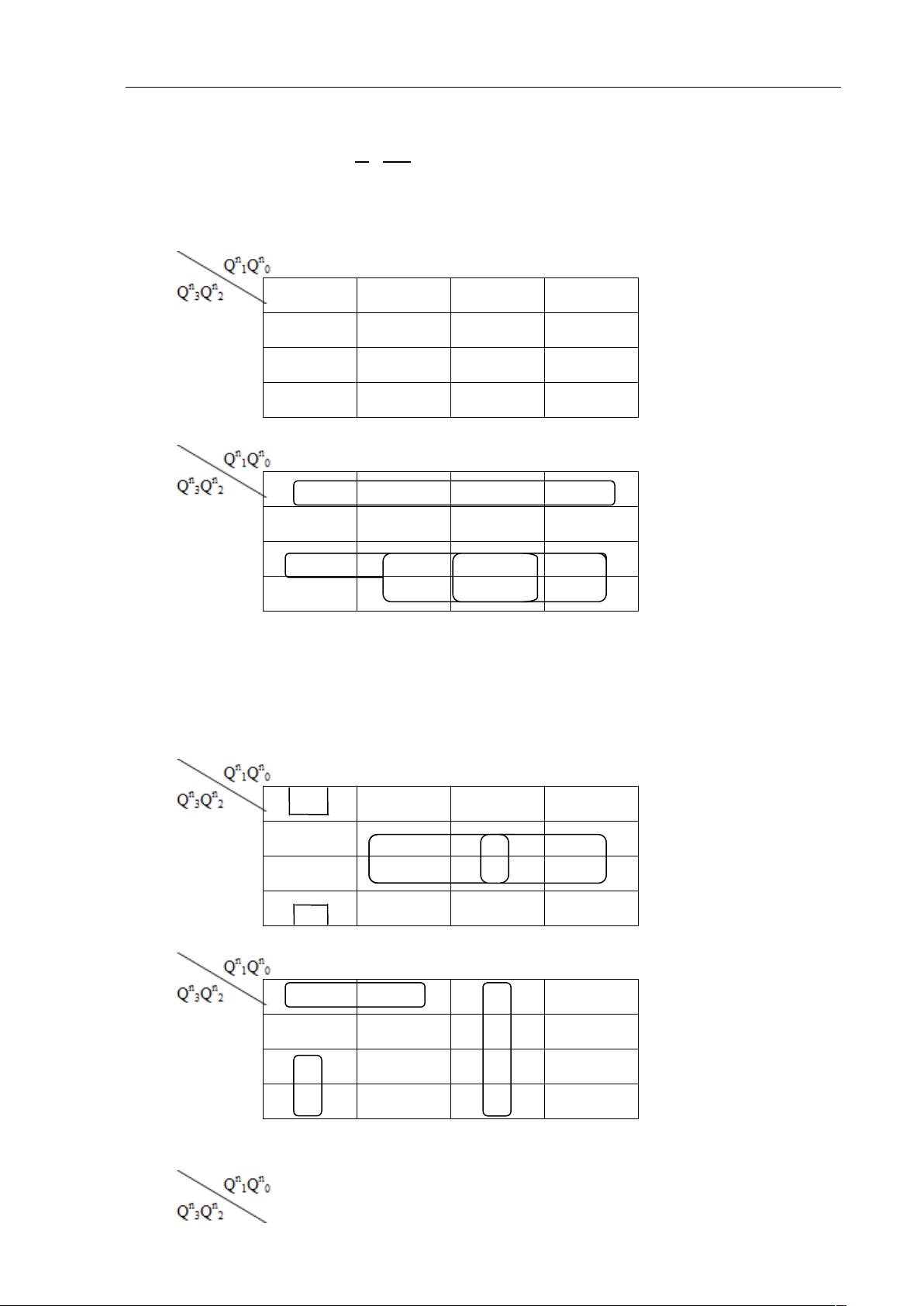

次态卡诺图:

00 01 11 10

00

01

11

10

所以:

Q

3

n+1

的 卡诺图为:

00 01 11 10

00

01

11

10

Q

2

n+1

的卡诺图为:

00 01 11 10

00

01

11

10

Q

1

n +1

的卡诺图为:

00 01 11 10

00

01

11

10

Q

0

n+1

的卡诺图为:

2

1111 ×××× ×××× ××××

0000 0001 0110 0101

1011 1100 1110 1101

0111 1000 1010 1001

1 × × ×

0 0 0 0

1 1 1 1

0 1 1 1

1 × × ×

0 1 1 1

0 1 1 1

1 0 0 0

1 × × ×

0 0 1 0

1 0 1 0

1 0 1 0

沈阳理工大学课程设计

00 01 11 10

00

01

11

10

状 态方程:

Q

3

n+1

= Q

n

3

Q

n

2

+ Q

n

3

Q

n

0

+ Q

n

3

Q

n

1

+

——

Q

n

3

_——

Q

n

2

=

——

Q

n

3

_——

Q

n

2

+ (Q

n

0

+Q

n

1

+Q

n

2

)Q

n

3

Q

2

n+1

=

——

Q

n

2

——

Q

n

1

——

Q

n

0

+ (Q

n

0

+Q

n

1

)Q

n

3

Q

1

n+1

=

——

Q

n

1

——

Q

n

0

Q

n

3

+ Q

n

1

Q

n

0

+

——

Q

n

1

——

Q

n

3

_——

Q

n

2

Q

0

n+1

=

——

Q

n

0

(Q

n

3

+Q

n

1

+

——

Q

n

2

)

驱动方程为:

J3=

_——

Q

n

2

K3=

_——

Q

2

——

Q

0

——

Q

1

J2=

——

Q

n

1

——

Q

n

0

K2=

——

Q

n

1

——

Q

n

0

J1==

——

Q

n

0

Q

n

2

Q

n

2

——

Q

n

3

——

Q

n

0

Q

n

3

K1=

——

Q

n

0

J0= Q

n

1

Q

n

2

Q

n

3

K0=1

(6) 检验能否自启动(无效状态 0001,0010,0011)

0011 0010 1001

0001 1010

所以能自启动

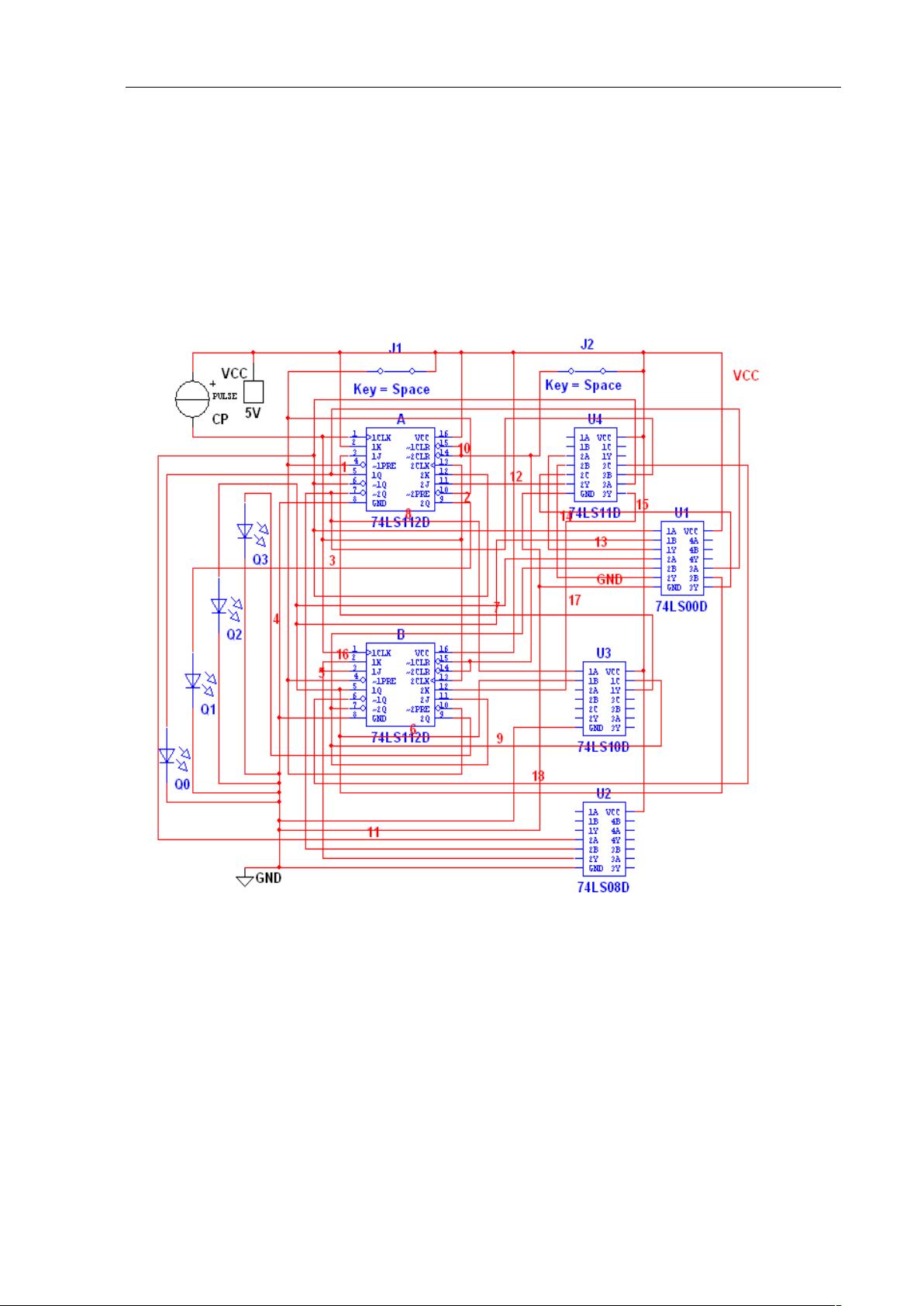

1.4 逻辑接线图:

3

1 × × ×

0 0 0 1

1 0 0 1

1 0 0 1

沈阳理工大学课程设计

1.5 电路接线图

1.6 实验仪器

74LS112 芯片 2 块,74LS08 芯片 1 块 74LS00 芯片 2 块 开关导线若干

1.7 实验结论(分析实验中出现的故障及产生的原因)

实验正常,个芯片运行正常。

4

沈阳理工大学课程设计

2 串行序列信号检测器(检测序列为 1101)

2.1 课程设计的目的:

1、了解同步计数器的工作原理和逻辑功能。

2、掌握计数器电路的分析、设计方法及应用。

3、熟悉设计过程和边沿 JK 触发器原理。

2.2 设计总框图:

CP

序列发生器的时钟脉冲 输出信号

2 . 3 设计过程

2 . 3 . 1 进行逻辑抽象,建立原始状态图。

1/0

0/0

1/0 1/0 0/0 1/1

S

0

S

1

S

2

S

3

S

4

1/0

0/0 0/0

0/0

2 . 3 . 2 进行状态化简,画出最简状态图

1、 合并等价状态,化简原始状态图得到最简状态图

0/0

1/1

1/0 1/0 0/0

S

0

S

1

S

2

S

3

0/0 0/0 1/0

2、 进行状态分配,画出用二进制编码后的状态图

状态图如下:

0/0

1/0 1/0 0/0

0 0 0 1 1 0 1 1 1 / 1

5

序列信号检测器(检测序

列为 1101)

剩余20页未读,继续阅读

资源评论

baooer2012-07-12很早以前下的都没评论,好好,东西很不错,做一点修改就好了

baooer2012-07-12很早以前下的都没评论,好好,东西很不错,做一点修改就好了

guodongwuyu

- 粉丝: 9

- 资源: 8

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 卡方数据.sav

- Python实现基于Django框架的二手物品购物网站设计源码+数据库.zip

- 基于Python和Django的二手物品购物网站设计源码+数据库脚本.zip

- 【计算机毕业设计】基于h5的移动网赚项目小程序【源码+lw+部署文档+讲解】

- 【计算机毕业设计】基于ssm-vue的oa系统设计与实现【源码+lw+部署文档+讲解】

- 基于pytorch实现的YOLOV5+SORT的车辆行人目标识别及追踪系统源码.zip

- 【计算机毕业设计】基于servlet+jdbc的在线选房系统设计与实现【源码+lw+部署文档+讲解】

- 投身科技创新,勇担时代先锋.pptx

- 【计算机毕业设计】基于SSM的仿微博系统的设计与实现【源码+lw+部署文档+讲解】

- 使用 Web Components 实现,遵循 Material You 设计规范的 Web 前端组件库

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功