没有合适的资源?快使用搜索试试~ 我知道了~

两组四输入与非门。 The 74HC20; 74HCT20 is a dual 4-input NAND gate. Inputs include clamp diodes. This enables the use of current limiting resistors to interface inputs to voltages in excess of VCC.

资源推荐

资源详情

资源评论

1. General description

The 74HC20; 74HCT20 is a dual 4-input NAND gate. Inputs include clamp diodes. This

enables the use of current limiting resistors to interface inputs to voltages in excess of

V

CC

.

2. Features and benefits

Complies with JEDEC standard JESD7A

Low-power dissipation

Input levels:

For 74HC20: CMOS level

For 74HCT20: TTL level

ESD protection:

HBM JESD22-A114F exceeds 2000 V

MM JESD22-A115-A exceeds 200 V

Multiple package options

Specified from 40 Cto+80C and from 40 Cto+125C.

3. Ordering information

74HC20; 74HCT20

Dual 4-input NAND gate

Rev. 3 — 3 September 2012 Product data sheet

Table 1. Ordering information

Type number Package

Temperature range Name Description Version

74HC20N 40 C to +125 C DIP14 plastic dual in-line package; 14 leads (300 mil) SOT27-1

74HCT20N

74HC20D 40 C to +125 C SO14 plastic small outline package; 14 leads; body width

3.9 mm

SOT108-1

74HCT20D

74HC20DB 40 C to +125 C SSOP14 plastic shrink small outline package; 14 leads; body

width 5.3 mm

SOT337-1

74HCT20DB

74HC20PW 40 C to +125 C TSSOP14 plastic thin shrink small outline package; 14 leads;

body width 4.4 mm

SOT402-1

74HCT20PW

74HC_HCT20 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2012. All rights reserved.

Product data sheet Rev. 3 — 3 September 2012 2 of 16

NXP Semiconductors

74HC20; 74HCT20

Dual 4-input NAND gate

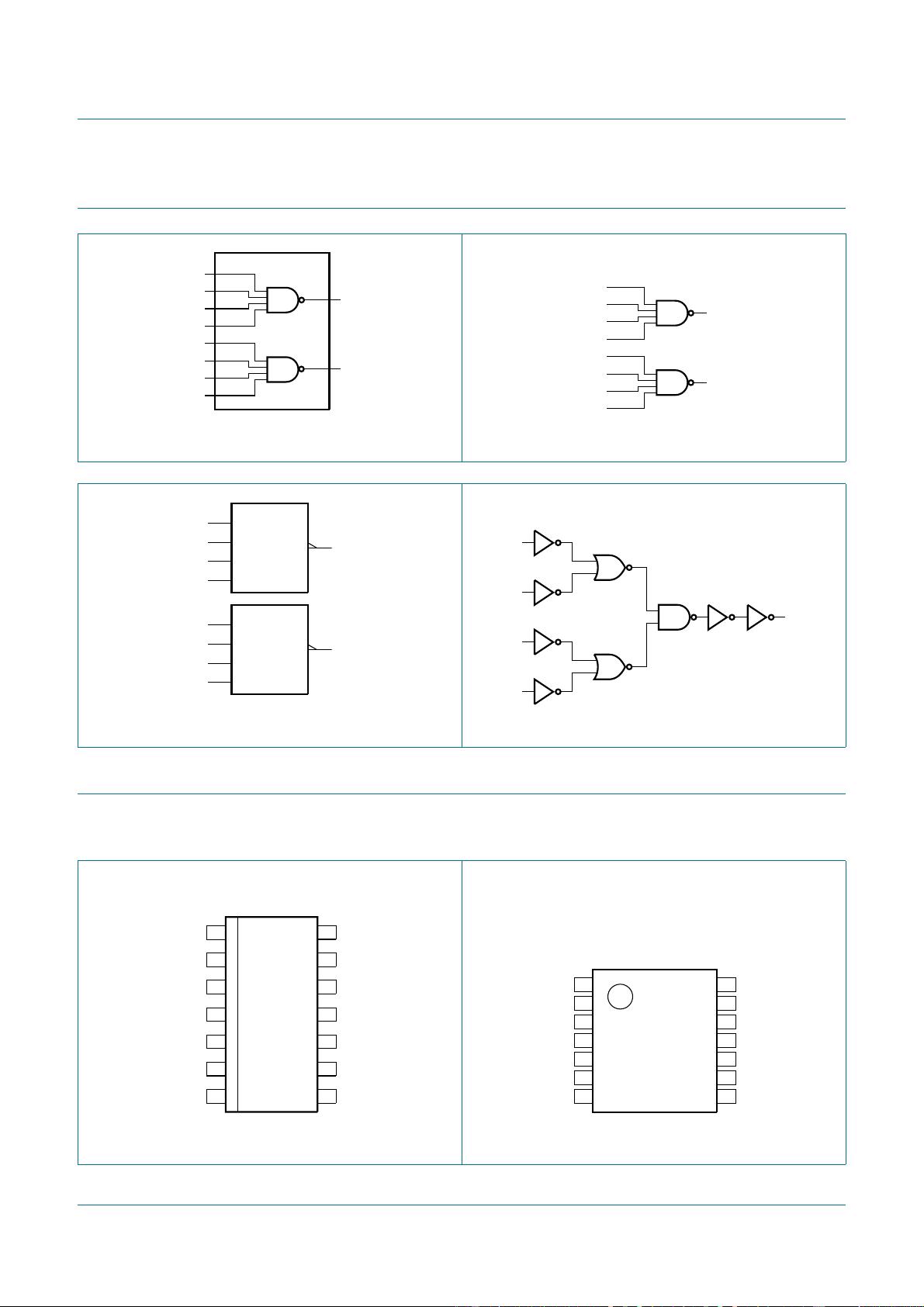

4. Functional diagram

5. Pinning information

5.1 Pinning

Fig 1. Functional diagram Fig 2. Logic symbol

$

%

&

'

<

$

%

&

'

<

DDD

$

%

&

'

<

$

%

&

'

<

DDD

Fig 3. IEC Logic symbol Fig 4. Logic diagram

DDD

$

%

&

'

<

DDD

Fig 5. Pin configuration SOT27-1 and SOT108-1 Fig 6. Pin configuration SOT337-1 and SOT402-1

9

&&

'

&

QF

%

$

<

+&

+&7

DDD

$

%

Q

F

&

'

<

*1

'

$

9

&&

%

'

Q

F

&

&

QF

'

%

<

$

*1

'

<

+&

+&7

DDD

74HC_HCT20 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2012. All rights reserved.

Product data sheet Rev. 3 — 3 September 2012 3 of 16

NXP Semiconductors

74HC20; 74HCT20

Dual 4-input NAND gate

5.2 Pin description

6. Functional description

[1] H = HIGH voltage level; L = LOW voltage level; X = don’t care.

7. Limiting values

[1] The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

[2] For DIP14 package: P

tot

derates linearly with 12 mW/K above 70 C.

For SO14 package: P

tot

derates linearly with 8 mW/K above 70 C.

For (T)SSOP14 packages: P

tot

derates linearly with 5.5 mW/K above 60 C.

Table 2. Pin description

Symbol Pin Description

1A, 1B, 1C, 1D 1, 2, 4, 5 data input

n.c. 3, 11 not connected

1Y 6 data output

GND 7 ground (0 V)

2Y 8 data output

2A, 2B, 2C, 2D 9, 10, 12, 13 data input

V

CC

14 supply voltage

Table 3. Function table

[1]

Input Output

nA nB nC nD nY

LXXXH

XLXXH

XXLXH

XXXLH

HHHHL

Table 4. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V).

Symbol Parameter Conditions Min Max Unit

V

CC

supply voltage 0.5 +7 V

I

IK

input clamping current V

I

< 0.5 V or V

I

>V

CC

+0.5 V

[1]

- 20 mA

I

OK

output clamping current V

O

< 0.5 V or V

O

>V

CC

+0.5V

[1]

- 20 mA

I

O

output current 0.5 V < V

O

< V

CC

+0.5V - 25 mA

I

CC

supply current - 50 mA

I

GND

ground current 50 - mA

T

stg

storage temperature 65 +150 C

P

tot

total power dissipation

[2]

DIP14 package - 750 mW

SO14, and (T)SSOP14

packages

- 500 mW

剩余15页未读,继续阅读

资源评论

ZoeyCool

- 粉丝: 3

- 资源: 23

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 微信小程序的图书管理系统-论文.zip

- 个人发卡源码发卡系统二次元发卡系统二次元发卡源码发卡程序动漫发卡PHP发卡源码异次元发卡项目资源O.zip

- 1吸烟抽烟行为识别数据集-超高识别率,支持YOLOV9格式的标注,10162张各种姿势场景下的吸烟图片.yolov9.zip

- 基于Layui和SpringBoot动漫商城管理的设计与实现--论文.zip

- 144ssm学生自我管理hsg4886B6程序.zip

- weixin149家庭财务管理系统的设计与实现ssm.rar

- 【java毕业设计】动漫之家系统源码(ssm+mysql+说明文档+LW).zip

- ssm444基于Java Web的线上办公管理系统设计与实现vue.rar

- springbootmysql学生选课系统.zip

- springboot345基于java敬老院管理系统202335806.zip

- 仿制商城小程序.zip

- Python从零开始实现神经网络及其应用详解

- 30-电影购票系统.zip

- 个人发卡源码发卡系统二次元发卡系统二次元发卡源码发卡程序动漫发卡PHP发卡源码异次元发卡项目资源.zip

- ssm620城投公司企业人事管理系统设计与实现vue.rar

- 550汉服推广网站.zip

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功