没有合适的资源?快使用搜索试试~ 我知道了~

A Low-Cost 12-bits Speech CODEC Using the MSP430F13x

需积分: 7 0 下载量 3 浏览量

2020-03-31

09:33:26

上传

评论

收藏 247KB PDF 举报

温馨提示

This application report illustrates a design of a single chip speech codec (ADC and DAC) using the MSP430F133 MCU from Texas Instruments. The ADC part of this codec uses the on chip 12-bit ADC. The DAC part uses a novel PWM technique which enables the DAC to operate at a high over-sampling frequency with high resolution. This simplifies the subsequent filter circuitry. Combined with on-chip voice compression algorithms, this solution forms a cost effective and ultra-low-power base band circuit for voice communication applications.

资源推荐

资源详情

资源评论

Application Report

SLAA131 –September 2001

1

A Low-Cost 12-Bit Speech CODEC Design Using the

MSP430F13x

Kes Tam, Vincent Chan MSP/MSC

ABSTRACT

This application report illustrates a design of a single chip speech codec (ADC and DAC)

using the MSP430F133 MCU from Texas Instruments. The ADC part of this codec uses

the on chip 12-bit ADC. The DAC part uses a novel PWM technique which enables the

DAC to operate at a high over-sampling frequency with high resolution. This simplifies the

subsequent filter circuitry. Combined with on chip voice compression algorithms, this

solution forms a cost effective and ultra-low-power base band circuit for voice

communication applications.

Contents

1 Introduction......................................................................................................................................................2

2 System Overview .............................................................................................................................................3

3 Filters response ...............................................................................................................................................4

3.1 Moving Average and Comb Filter .............................................................................................................4

3.2 Forth-Order LPF........................................................................................................................................5

3.3 Combined Response.................................................................................................................................7

4 Oversampling...................................................................................................................................................9

5 Dual PWM .........................................................................................................................................................9

6 Summary.........................................................................................................................................................10

References ..............................................................................................................................................................11

Appendix A. Schematic..........................................................................................................................................12

Appendix B. Software Listing ...............................................................................................................................13

Figures

Figure 1. System Block Block Diagram ................................................................................................................3

Figure 2. Moving Average or Comb Filter Gain Response .................................................................................5

Figure 3. A Second Order Low-Pass Filter ...........................................................................................................6

Figure 4. Output Analog LPF Gain Response......................................................................................................7

Figure 5. Ouput Section Gain Response ..............................................................................................................8

Figure 6. Overall System Gain Response.............................................................................................................8

Figure 7. Combing Two PWM Outputs................................................................................................................10

SLAA131

2 A Low-Cost 12-Bit Speech CODEC Design Using the MSP430F13x

1 Introduction

The MSP430F13x series MCU from Texas Instruments (hereafter referred to as F13x) has a

built-in 12 bit high quality ADC, which is well suited for voice as well as instrumentation

applications. However, for many voice communication applications, a DAC is also required.

The F13x, like many other MCUs, uses its PWM modules as a DAC. The challenge here is to

maintain the power consumption level, and therefore the clock speed, to a minimum while

providing good DAC resolution at a high over-sampling frequency. The high over-sampling

frequency is required to simplify the post filtering circuitry and therefore to keep down cost circuit

space.

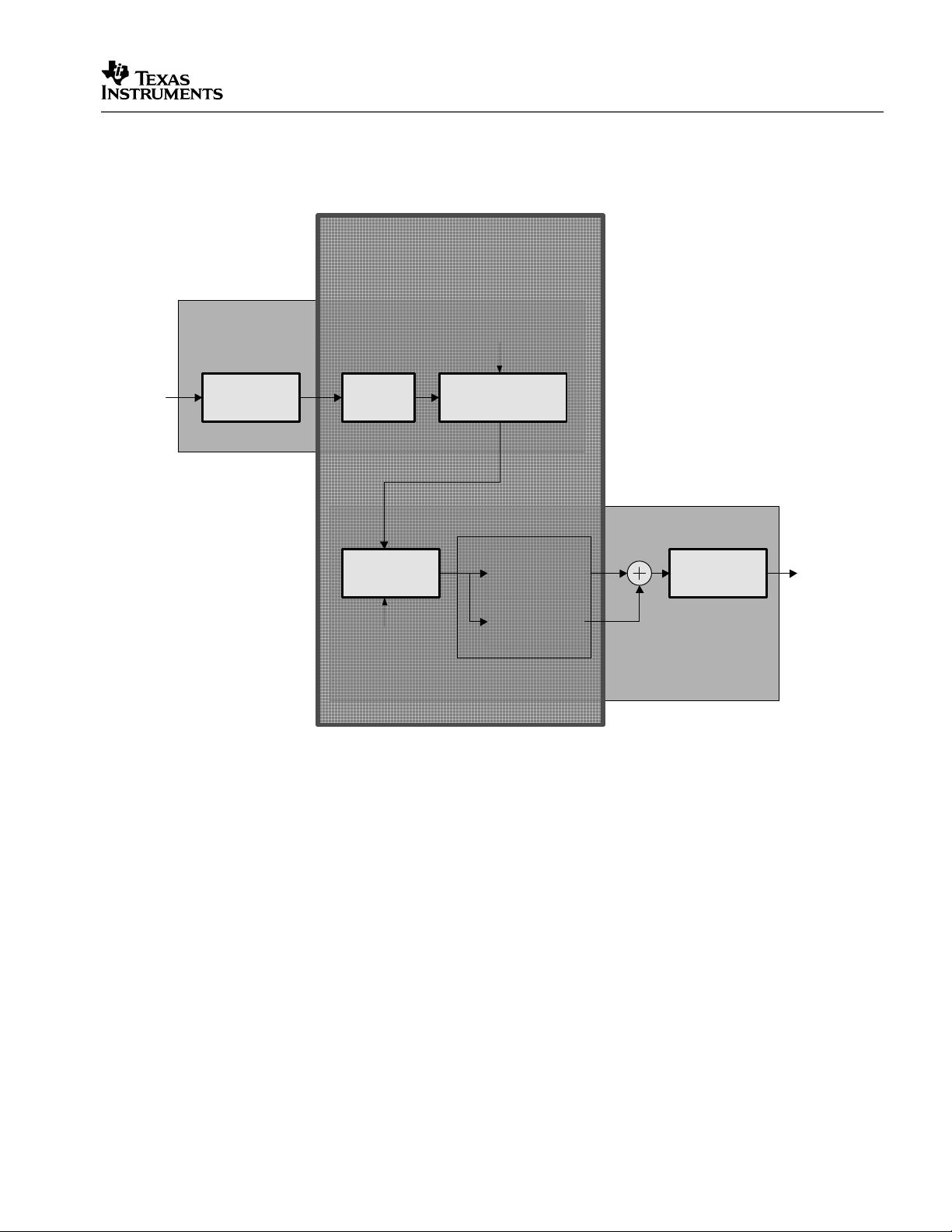

Section 2 shows the system block diagram of this design from audio input, through different

digital and analog sampling and filtering stages, to the final audio output.

We have used digital filters with over-sampling to simplify the hardware. Section 3 describes the

digital and analog filters used in this system. Section 4 talks about the over-sampling technique

used.

This design uses a PWM DAC of 12 bits resolution at 40 ksps (5 times over-sampling) running

from an 8 MHz clock. These contrasting demands are met by using a novel dual PWM

technique. This technique is described in detail under Section 5.

The hardware schematic and software listing is included in the appendices. It can be easily

constructed using Texas Instruments’ MSP-FET430P140 development tools.

SLAA131

A Low-Cost 12-Bit Speech CODEC Design Using the MSP430F13x 3

2SystemOverview

Moving Average

Filter

12-bits

ADC

Audio

in

First-order

LPF

Input Section

Downsampling

to 8KHz

(40KHz)

Comb Filter

Audio

out

Forth-order

LPF

Output Section

Upsampling

to 40KHz

(40KHz)

MSP430F13x

PWM1

(lower 6-bits)

PWM2

(upper 6-bits)

Figure 1. System Block Diagram

Figure 1 shows the system block diagram. The voice signal is first over-sampled at 40 ksps and

then internally down sampled to 8 ksps. The frequency response of the codec is designed to

have a very fast roll off at approximate 3.5 kHz.

For easy understanding, the whole system is represented as input to output signal chain.

The input section consists of three stages.

a) The first stage provides first-order pre-sample low pass filtering and electret microphone

amplification. The roll off is set to start at 4 kHz, and because the signal is over-sampled at

40 ksps, the roll off of this low pass filter can be very gentle.

b) The second stage provides the analog to digital conversion using the on chip 12-bit ADC of

the F13x device. The built-in 16 word auto-scan buffer of the ADC allows multiple samples to

be accessed simultaneously. This economizes on CPU ADC access bandwidth.

SLAA131

4 A Low-Cost 12-Bit Speech CODEC Design Using the MSP430F13x

c) The third stage consists of a moving average filter and a down sampler from 40 ksps to 8

ksps. The cut off frequency of this digital filter is set to 4 kHz.

For demonstration purpose, the output data of the input section is internally routed to the output

section. In real applications, the sampled data is often further processed before being sent

through a network. For example, for wireless voice communication, data is compressed using

ADPCM coding before being sent out.

The output section consists also of three stages.

a) In the first stage, samples come in at 8 ksps and go out at 40 ksps. In between is anup-

sampler and a comb filter.

b) The next stage is the PWM DAC process. In this stage, two 6 bit PWMs makes up a12-bit

DAC. More detail will be covered in Section 5.

c) The last stage is a forth-order analog low pass filter which converts the digital output of the

PWM to an analog signal. The 40-kHz carrier is filtered out.

3 Filters response

A total of four filters are used, two analog and two digital. The first stage low-pass filter has been

covered in Section 2. We will cover the comb filter and the moving average filter in detail here.

The forth-order LPF (low pass filter) is made up of two second-order LPFs cascaded together.

They are made identical to simplify the design.

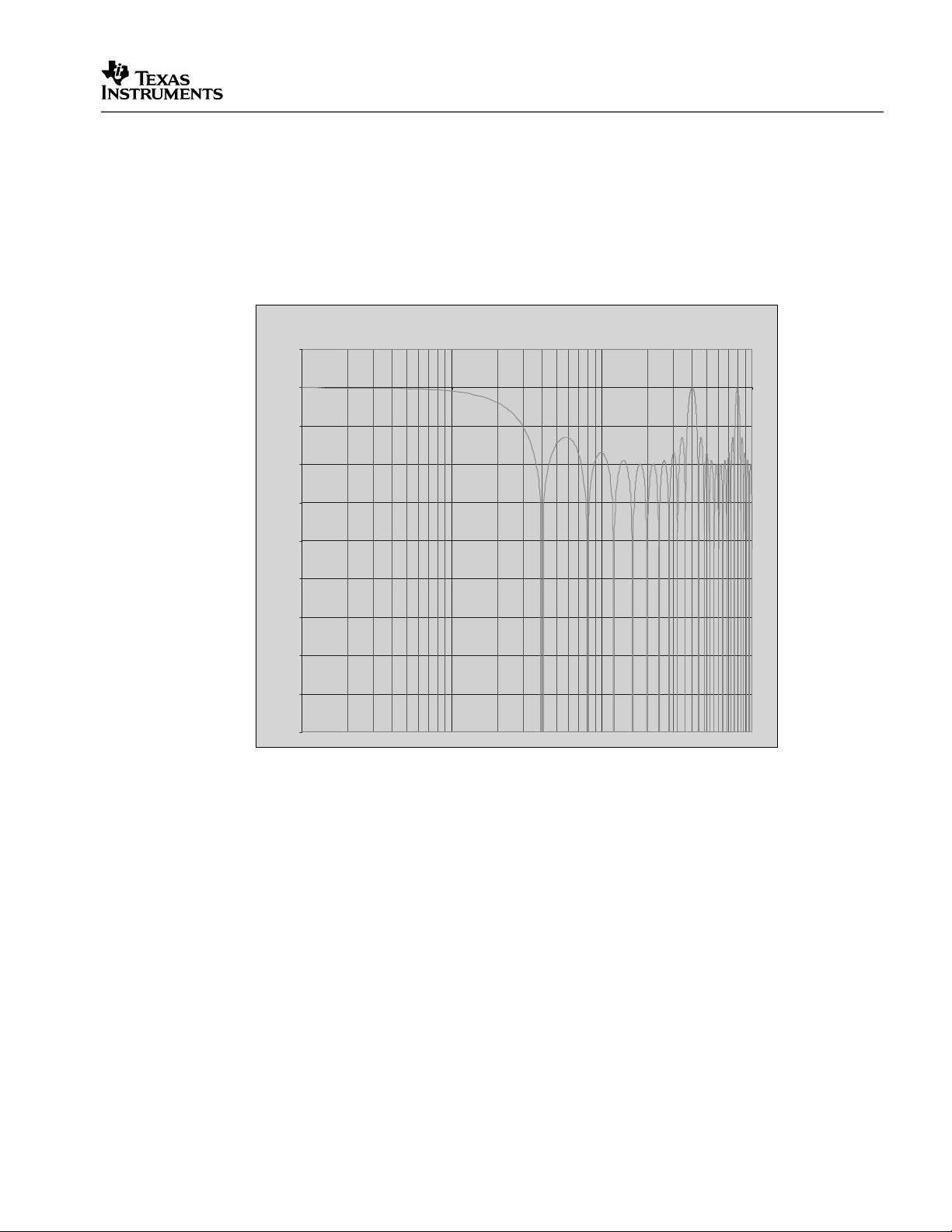

3.1 Moving Average and Comb Filter

Moving average filters and comb filters does not provide very fast roll off. However, they are very

simple filters to implement.

The transfer function of the comb filter used here is given by

H(z) = (1/k)*(1-z

-k

)/(1-z

-1

)(1)

Where:

f

c

=f

s

/k

f

c

= cut off frequency

f

s

= sampling frequency

In actual implementation, the output sequence can be obtained with the equation below.

y[n] = y[n-1] + (x[n] – x[n-k])/k (2)

where y is the output and x is the input

The moving average filter comes out the same as the comb filter. The output of the moving

average of k inputs is given by:

y[n] = (x[n] + x[n-1] + . . . + x[n-(k-1)])/k (3)

For next output, it will be:

y[n+1] = (x[n+1] + x[n] + . . . + x[(n+1)-(k-1)])/k

or y[n+1] = (x[n+1] + k*y[n]-x[n-(k-1)])/k

SLAA131

A Low-Cost 12-Bit Speech CODEC Design Using the MSP430F13x 5

or y[n+1] = y[n] + (x[n+1]-x[n-(k-1)])/k

If we put n back with n-1,weget

y[n] = y[n-1] + (x[n]-x[n-k])/k

which is the same equation as (2).

This means the moving average filter is the same as the comb filter. To have a cutoff frequency

of 4 kHz, we choose k=10 and the response is shown in Figure 2.

-90

-80

-70

-60

-50

-40

-30

-20

-10

0

10

100 1000 10000 100000

Hz

db

Figure 2. Moving Average or Comb Filter Gain Response

3.2 Forth-Order LPF

The forth-order LPF is constructed by cascading two identical second-order LPFs. These two

filter stages are designed to be identical for simplicity only, the component values can be

redesigned to be different from stage to stage. Figure 3 shows one possible form of a second-

order filter.

剩余27页未读,继续阅读

资源评论

gj_john_dx

- 粉丝: 0

- 资源: 25

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 形状检测32-YOLO(v5至v9)、COCO、CreateML、Darknet、Paligemma数据集合集.rar

- qwewq23132131231

- 2024年智算云市场发展与生态分析报告

- 冒泡排序算法解析及优化.md

- MySQL中的数据库管理语句-ALTER USER.pdf

- 论文复现:结合 CNN 和 LSTM 的滚动轴承剩余使用寿命预测方法

- 2018年最新 ECshop母婴用品商城新版系统(微商城+微分销+微信支付)

- 形状分类31-YOLO(v5至v11)、COCO、CreateML、Darknet、Paligemma、VOC数据集合集.rar

- 常见排序算法概述及其性能比较

- 前端开发中的JS快速排序算法原理及实现方法

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功