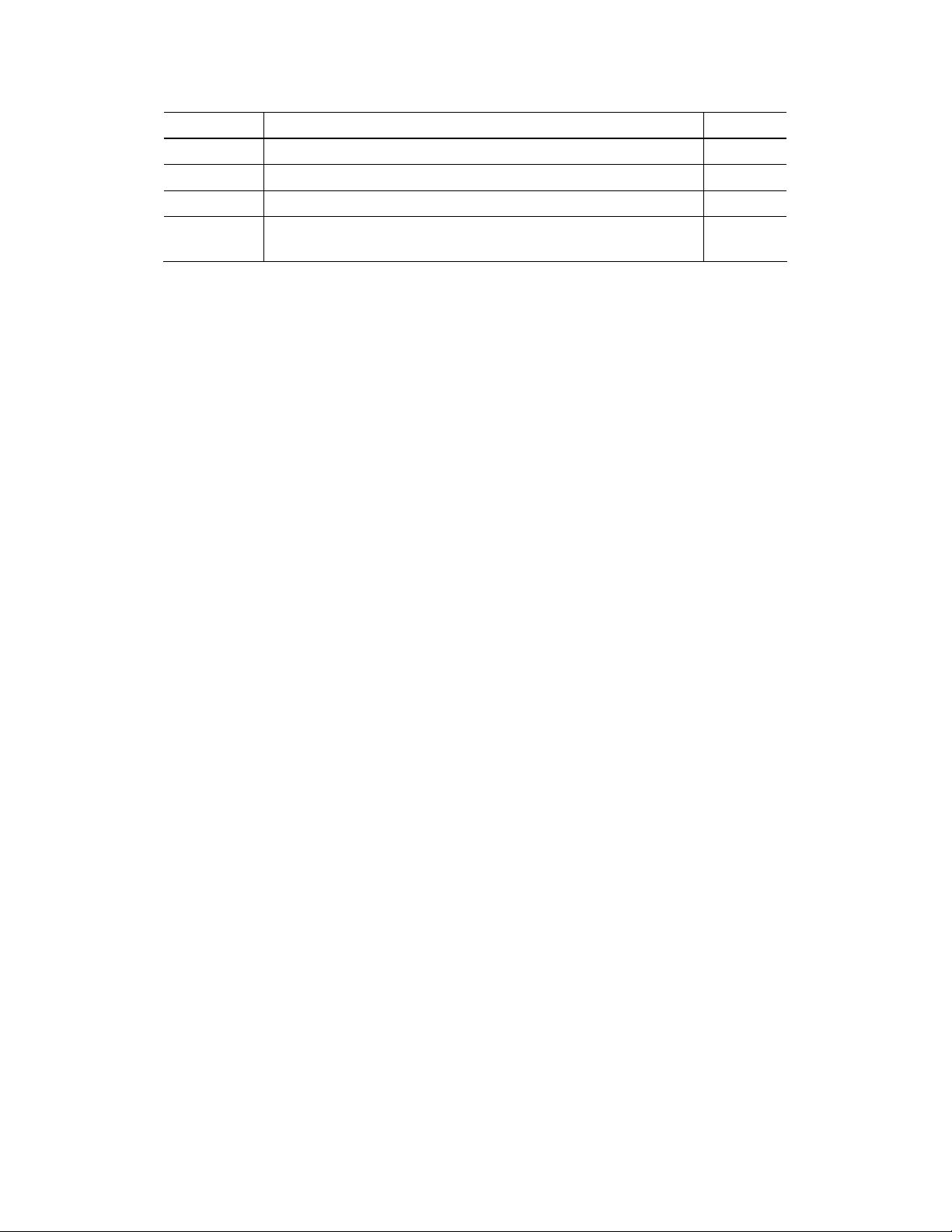

### PCIE Base Spec 2.0 知识点解析 #### 一、概述与文档组织结构 《PCI Express Base Specification Revision 2.0》(以下简称“PCIE 2.0”)是PCI-SIG(Peripheral Component Interconnect Special Interest Group)发布的一项关于PCI Express接口的技术规范。这份规范详细介绍了PCI Express 2.0版本的技术特性、架构设计以及实现方法等重要内容。该版本主要增加了5.0 GT/s的数据传输速率,并且合并了之前版本中的错误修正和技术更新。 PCIE 2.0文档由多个部分组成,包括但不限于以下章节: - **目标**:定义了该规范的主要目标。 - **文档组织**:概述了文档的整体结构和组织方式。 - **文档约定**:介绍了文档中使用的术语和格式。 - **术语和缩略语**:列出了文档中出现的重要术语及其定义。 - **参考文档**:列举了制定本规范时参考的相关资料和技术文档。 #### 二、技术要点 - **第1章:介绍** - **第1.1节:第三代I/O互联**:这部分阐述了PCI Express作为一种高级I/O技术的发展历程和设计理念。它强调了PCI Express相较于早期技术的优势,如更高的带宽、更低的延迟以及更好的可扩展性。 - **第1.2节:PCI Express链路**:详细描述了构成PCI Express系统的基本单元——链路(Link)。链路由一个或多个通道(Lane)组成,每个通道能够独立传输数据,提高了系统的可靠性和灵活性。 - **第1.3节:PCI Express拓扑结构**: - **根复合体(Root Complex)**:是PCI Express系统的核心组件之一,负责管理和协调整个系统的通信。它包含了PCI Express配置空间的一部分,以及多个端点(Endpoint)之间的连接控制。 - **端点(Endpoint)**:可以是任何形式的设备,如显卡、声卡等,它们通过链路与根复合体或其他端点相连。 - **交换机(Switch)**:用于扩展PCI Express拓扑,允许更多的设备连接到同一个系统中。交换机本身也具备一定的路由能力。 - **根复合体事件收集器(Root Complex Event Collector)**:用于收集并处理来自端点和其他组件的事件信息。 - **PCI Express到PCI/PCI-X桥接器**:用于将传统的PCI/PCI-X设备与PCI Express系统连接起来。 - **第1.4节:PCI Express拓扑结构配置**:讨论了如何配置不同的PCI Express拓扑结构,以满足不同应用场景的需求。 - **第1.5节:PCI Express分层概述**: - **事务层(Transaction Layer)**:负责处理上层协议请求并将其转换为适合物理层传输的格式。 - **数据链路层(Data Link Layer)**:确保数据在物理层上的可靠传输,包括错误检测与纠正机制。 - **物理层(Physical Layer)**:直接与硬件接口交互,负责信号的发送与接收,包括电气特性的定义等。 #### 三、修订历史 PCIE 2.0的修订历史如下: - **1.0版**:初始版本,于2002年7月22日发布。 - **1.0a版**:合并了C1-C66和E1-E4.17的错误修正,于2003年4月15日发布。 - **1.1版**:进一步合并了已批准的错误修正和工程更改通知(ECN),于2005年3月28日发布。 - **2.0版**:增加了5.0 GT/s的数据传输速率,并合并了所有已批准的错误修正和ECN,于2006年12月20日发布。 #### 四、免责声明与联系方式 文档还包含了一系列的免责声明,强调PCI-SIG不承担任何使用该文档及其中信息所导致的责任。此外,提供了联系PCI-SIG的方式,以便获取最新版本的规范文档或提出相关问题。 #### 五、总结 PCIE 2.0不仅是一项重要的技术标准,也是计算机行业发展的里程碑之一。它不仅提高了数据传输速度,还增强了系统的可扩展性和兼容性。通过阅读此规范,我们可以更深入地理解PCI Express技术的工作原理和发展趋势,这对于从事计算机硬件设计、开发和维护的专业人士来说是非常有价值的参考资料。

剩余607页未读,继续阅读

「已注销」2018-10-11这种资源你还要币?你有脸吗?良心不痛吗?原版的官方文档,你居然有脸作为自己的私有文档?当然是共享了!!!你以为你自己写的吗?

「已注销」2018-10-11这种资源你还要币?你有脸吗?良心不痛吗?原版的官方文档,你居然有脸作为自己的私有文档?当然是共享了!!!你以为你自己写的吗? taipeirayon2011-10-252.0是否可以比1.1快到底如何達成.這資料可以看其相容性.

taipeirayon2011-10-252.0是否可以比1.1快到底如何達成.這資料可以看其相容性. piaohuaxuanfeng2013-06-132.0和3.0 spec内容区别不是很大,看过其中一个,另外一份就容易看懂了.

piaohuaxuanfeng2013-06-132.0和3.0 spec内容区别不是很大,看过其中一个,另外一份就容易看懂了.

- 粉丝: 0

- 资源: 2

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 视频编码中基于改进DAG-SVM模型的H.266/VVC快速CU分区决策算法

- 第二章Rust初步.pptx

- 工具变量-中国农村统计面板数据集(2000-2022年).xlsx

- 第五章.pptx

- The official Meta Llama 3 GitHub site

- 第一章最终.pptx

- 基于Rust的网络软件设计与实现-20241117.docx

- 基于simulink的三自由度汽车操纵模型仿真与分析, 汽车三自由度操纵模型仿真与分析 基于simulink三自由度汽车操纵模型,包含侧向,侧倾和横摆 操纵模型附带具体数据参数,有详细的公式文档说明

- qt-everywhere-opensource-src-5.2.1.tar

- Docker容器技术的基本概念、安装与管理方法及其实用技巧入门指南

- 电池管理(BMS)控制系统 电动客车电池管理系统SOC估算单元设计 设计一款电池管理系统,它包含着以下功能: 1、搭建考虑温度的二阶RC电池Simulink模型,监测并且采集每节电池的电压、采集一部

- 嵌入式系统中的TC305触摸传感器原理与应用详解

- stm32g431 esc 无感foc非线性磁链观测器 速度环 电流环 零速双闭环启动 带载运行 堵转力矩保持 算法资料 只卖资料,没有硬件实物 资料包括cubemx配置文件,mdk项目文件,调试笔

- 扫描文件_QQ浏览器_20250103.pdf

- Python U盘小偷工具

- qt-everywhere-opensource-src-5.0.1.tar

信息提交成功

信息提交成功