FPGA 实现简易 DDS

1. 原理

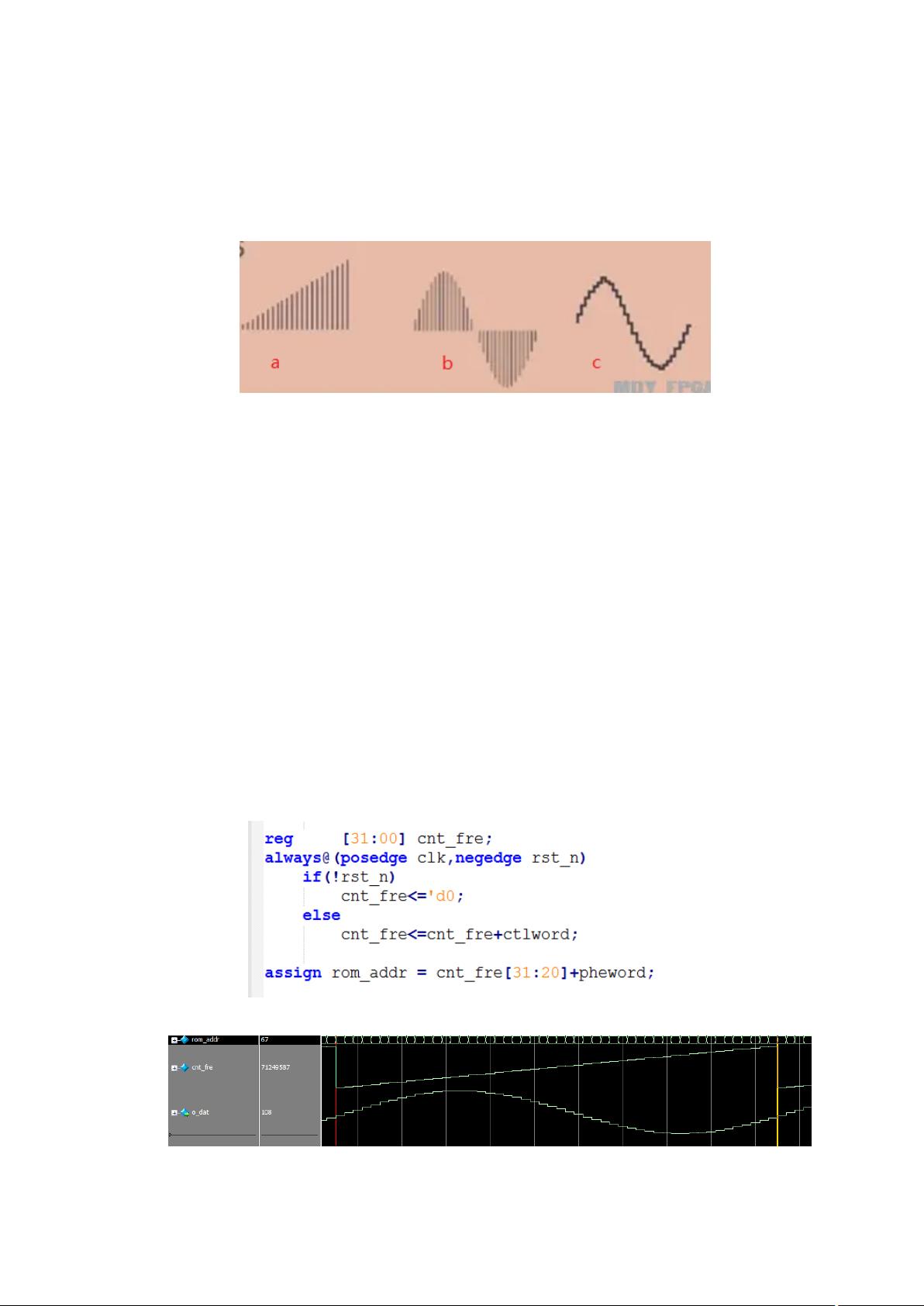

以正弦波为例,在 FPGA 内部开辟一个存储空间(ROM)来存放一个周期的正弦波数据文

件,然后将这个这个波形文件读出再进行 DA 转换就得到一个正弦信号,我觉得下图很形象,

a 是 ROM 的读地址,b 是 ROM 的读出数据,c 是 DA 后输出的波形。

图 1

现在设置 ROM 的大小为 4096 字节,那么地址 addr 位宽为 12 位,然后 addr 在 clk 时钟

驱动下加一,假设 clk 周期为 1us,因此输出的正弦信号周期为 4096*1us。

假设现在 addr 在每个 clk 加 2,那么现在只要 4096/2=2048 个 clk 就能读出 ROM 中的数

据,所以此时输出的正弦信号的周期就是 2048*1us。

继续假设现在 addr 在每个 clk 加 10,那么现在只要 4096/10=409.6 个 clk 就能读出 ROM

中的数据,所以此时输出的正弦信号的周期就是 409.6*1us。

现在设每次 clk 增加的数为 K,在以上的例子中 K=1、2、10;ROM 地址 addr 位宽 N,

在以上例子中,N 等于 12,那么可以得出输出正弦信号的周期 T

out

= (2

N

)/K * T

clk

。

在以上例子中,如果 ROM 中的波形数据数据越多,输出的波形越平滑,但是受限于 FPGA

的存储资源,波形数据不可能做很大,一般是 4096 个点,当然也有 1024、256 个等。然后

使用 32 位的计数器对 clk 计数,选择该计数器的高比特位作为 ROM 的地址,比如在以上例

子中使用计数器的 bit31 到 20bit。

至于相位就是读地址偏移,相位为 0,那么就从地址 0 开始,相位为 90 度,那么就从地

址 1024 开始读。

2. 软件实现

软件核心代码如下,ctlword 是 32 位频率控制字,pheword 是 12 位相位控制字。

图 2 软件核心代码

图 3 软件仿真