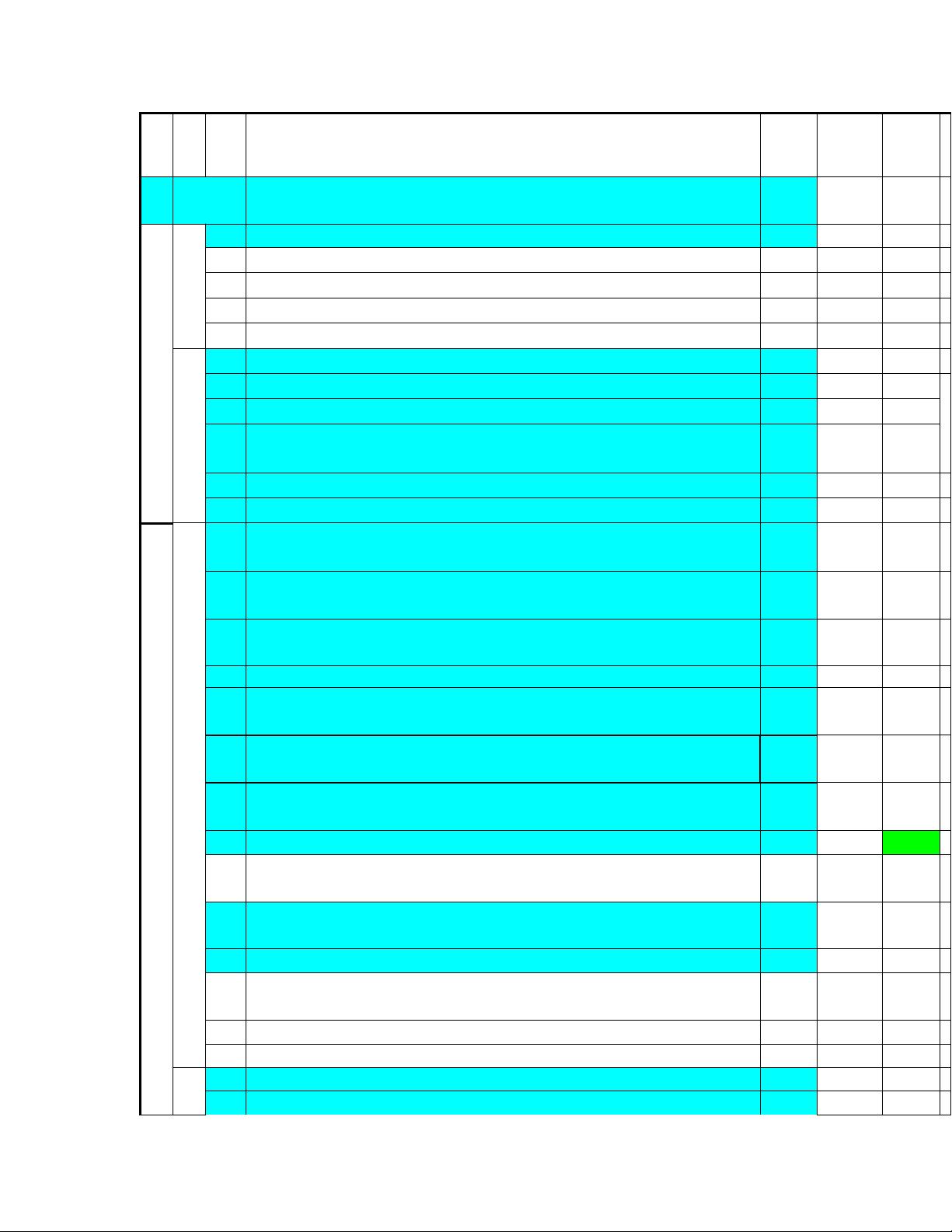

华为硬件PCB设计检查清单 本文档旨在提供一个详细的检查清单,涵盖华为硬件PCB设计的各个方面,包括布局、布线、出加工文件等内容。该检查清单旨在确保PCB设计的正确性和可靠性,避免设计错误和缺陷。 一、 PCB设计检查 1. 确认PCB网表与原理图描述的网表一致 2. 确认外形图是最新的,已经考虑了工艺问题 3. 确认外形图已考虑了禁止布线区、传送边、挡条边、拼板等问题 4. 确认PCB模板是最新的,建议采用外形图的 5. 比较外形图,确认PCB所标注尺寸及公差无误 二、 布局设计检查 6. 数字电路和模拟电路是否已分开,信号流是否合理 7. 时钟器件布局是否合理 8. 高速信号器件布局是否合理 9. 端接器件是否已合理放置 10. IC器件的去耦电容数量及位置是否合理 11. 保护器件(如TVS、PTC)的布局及相对位置是否合理 12. 是否按照设计指南或参考成功经验放置可能影响EMC实验的器件 三、 元器件布局检查 13. 较重的元器件,应该布放在靠近PCB支撑点或支撑边的地方,以减少PCB的翘曲 14. 对热敏感的元件(含液态介质电容、晶振)尽量远离大功率的元器件、散热器等热源 15. 器件高度是否符合外形图对器件高度的要求 16. 压接插座周围5mm范围内,正面不允许有高度超过压接插座高度的元件,背面不允许有元件或焊点 17. 在PCB上轴向插装较高的元件,应该考虑卧式安装。留出卧放空间。并且考虑固定方式,如晶振的固定焊盘 四、 PCB设计其它检查 18. 金属壳体的元器件,特别注意不要与其它元器件或印制导线相碰,要留有足够的空间位置 19. 母板与子板,单板与背板,确认信号对应,位置对应,连接器方向及丝印标识正确 20. 打开TOP和BOTTOM层的place-bound,查看重叠引起的DRC是否允许 21. 波峰焊面,允许布设的SMD种类为:0603以上(含0603) 22. 波峰焊面,SMD放置方向应垂直于波峰焊时PCB传送方向 23. 波峰焊面,阴影效应区域为0.8mm(垂直于PCB传送方向)和1.2mm(平行于PCB传送方向),钽电容在前为2.5mm 24. 元器件是否100%放置 25. 是否已更新封装库(用viewlog检查运行结果) 26. 器件的管脚排列顺序,第1脚标志,器件的极性标志,连接器的方向标识 27. 器件封装的丝印大小是否合适,器件文字符号是否符合标准要求 28. 插装器件的通孔焊盘孔径是否合适、安装孔金属化定义是否准确 29. 表面贴装器件的焊盘宽度和长度是否合适 五、 PCB设计可靠性检查 30. 回流焊面和波峰焊面的电阻和电容等封装是否区分布线EMC与可靠性 31. 布通率是否100% 32. 时钟线、差分对、高速信号线是否已满足(SI约束)要求 33. 高速信号线的阻抗各层是否保持一致 34. 各类BUS是否已满足(SI约束)要求 35. E1、以太网、串口等接口信号是否已满足要求EMC 36. 时钟线、高速信号线、敏感的信号线不能出现跨越参考平面而形成大的信号回路 37. 电源、地是否能承载足够的电流 38. 芯片上的电源、地引出线从焊盘引出后就近接电源、地平面 39. 电源、地层应无孤岛、通道狭窄现象 40. PCB上的工作地(数字地和模拟地)、保护地、静电防护与屏蔽地的设计是否合理 41. 单点接地的位置和连接方式是否合理 42. 需要接地的金属外壳器件是否正确接地 43. 信号线上不应该有锐角和不合理的直角间距 44. Spacing rule set要满足最小间距要求 45. 不同的总线之间、干扰信号与敏感信号之间是否尽量执行了3W原则 46. 差分对之间是否尽量执行了3W原则 47. 差分对的线间距要根据差分阻抗计算,并用规则控制 48. 非金属化孔内层离线路及铜箔间距应大于0.5mm(20mil),外层0.3mm(12mil) 通过该检查清单,PCB设计者可以确保设计的正确性和可靠性,避免设计错误和缺陷,提高PCB的质量和可靠性。

- 粉丝: 0

- 资源: 6

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功

评论0