没有合适的资源?快使用搜索试试~ 我知道了~

温馨提示

试读

42页

VerilogHDL程序都是我们自己为教学目的而编写的,全部程序在CADENCE公司的LWB (Logic Work Bench)环境下和 Mentor 公司的ModelSim 环境下用Verilog语言进行了仿真, 通过了运行测试,并分别用Synergy和Synplify综合器针对不同的FPGA进行了综合。分别用Xilinx和Altera公司的的布局布线工具在Xilinx3098上和Altera Flex10K10实现了布线。 顺利通过综合前仿真、门级结构仿真以及布线后的门级仿真。这个 CPU 模型只是一个教学模型, 设计也不一定合理, 只是从原理上说明了一个简单的RISC _CPU的构成。

资源推荐

资源详情

资源评论

可综合的VerilogHDL设计实例

---简化的RISC CPU设计简介---

前言:

在前面七章里我们已经学习了VerilogHDL的基本语法、简单组合逻辑和简单时序逻辑模块的编

写、Top-Down设计方法、还学习了可综合风格的有限状态机的设计,其中EEPROM读写器的设计

实质上是一个较复杂的嵌套的有限状态机的设计,它是根据我们完成的实际工程项目设计为教学目

的改写而来的,可以说已是真实的设计。

在这一章里, 我们将通过一个经过简化的用于教学目的的 RISC_CPU 的设计过程,来说明这种新设

计方法的潜力。这个模型实质上是第四章的RISC_CPU模型的改进。第四章中的RISC_CPU模型是

一个仿真模型,它关心的只是总体设计的合理性,它的模块中有许多是不可综合的,只可以进行仿

真。而本章中构成RISC_CPU的每一个模块不仅是可仿真的也都是可综合的,因为他们符合可综合

风格的要求。为了能在这个虚拟的CPU上运行较为复杂的程序并进行仿真, 因而把寻址空间扩大到

8K(即15位地址线)。下面让我们一步一步地来设计这样一个CPU,并进行仿真和综合,从中我

们可以体会到这种设计方法的魅力。本章中的VerilogHDL程序都是我们自己为教学目的而编写

的,全部程序在CADENCE公司的LWB (Logic Work Bench)环境下和 Mentor 公司的

ModelSim 环境下用Verilog语言进行了仿真, 通过了运行测试,并分别用Synergy和Synplify综

合器针对不同的FPGA进行了综合。分别用Xilinx和Altera公司的的布局布线工具在Xilinx3098上

和Altera Flex10K10实现了布线。 顺利通过综合前仿真、门级结构仿真以及布线后的门级仿真。

这个 CPU 模型只是一个教学模型, 设计也不一定合理, 只是从原理上说明了一个简单的RISC _CPU

的构成。我们在这里介绍它的目的是想说明:Verilog HDL仿真和综合工具的潜力和本文介绍的设

计方法对软硬件联合设计是有重要意义的。我们也希望这一章能引起对 CPU 原理和复杂数字逻辑

系统设计有兴趣的同学的注意,加入我们的设计队伍。由于我们的经验与学识有限,不足之处敬请读

者指正。

8.1.什么是CPU?

CPU 即中央处理单元的英文缩写,它是计算机的核心部件。计算机进行信息处理可分为两个步骤:

1) 将数据和程序(即指令序列)输入到计算机的存储器中。

2) 从第一条指令的地址起开始执行该程序,得到所需结果,结束运行。CPU的作用是协

调并控制计算机的各个部件执行程序的指令序列,使其有条不紊地进行。因此它必须

具有以下基本功能:

a) 取指令:当程序已在存储器中时,首先根据程序入口地址取出一条程序,为此要发

出指令地址及控制信号。

b) 分析指令:即指令译码。是对当前取得的指令进行分析,指出它要求什么操作,并

产生相应的操作控制命令。

c) 执行指令:根据分析指令时产生的“操作命令”形成相应的操作控制信号序列,通过

运算器,存储器及输入/输出设备的执行,实现每条指令的功能,其中包括对运算

结果的处理以及下条指令地址的形成。

将其功能进一步细化,可概括如下:

1) 能对指令进行译码并执行规定的动作;

2) 可以进行算术和逻辑运算;

3) 能与存储器,外设交换数据;

4) 提供整个系统所需要的控制;

171

尽管各种CPU的性能指标和结构细节各不相同,但它们所能完成的基本功能相同。由功能分析,可

知任何一种CPU内部结构至少应包含下面这些部件:

1) 算术逻辑运算部件(ALU),

2) 累加器,

3) 程序计数器,

4) 指令寄存器,译码器,

5) 时序和控制部件。

RISC 即精简指令集计算机(Reduced Instruction Set Computer)的缩写。它是一种八十年代

才出现的CPU,与一般的CPU 相比不仅只是简化了指令系统,而且是通过简化指令系统使计算机的

结构更加简单合理,从而提高了运算速度。从实现的途径看,RISC_CPU与一般的CPU的不同处在

于:它的时序控制信号形成部件是用硬布线逻辑实现的而不是采用微程序控制的方式。所谓硬布线

逻辑也就是用触发器和逻辑门直接连线所构成的状态机和组合逻辑,故产生控制序列的速度比用微

程序控制方式快得多,因为这样做省去了读取微指令的时间。RISC_CPU也包括上述这些部件,下

面就详细介绍一个简化的用于教学目的的RISC_CPU的可综合VerilogHDL模型的设计和仿真过

程。

8.2. RISC CPU结构

RISC_CPU是一个复杂的数字逻辑电路,但是它的基本部件的逻辑并不复杂。从第四章我们知道可

把它分成八个基本部件:

1) 时钟发生器

2) 指令寄存器

3) 累加器

4) RISC CPU算术逻辑运算单元

5) 数据控制器

6) 状态控制器

7) 程序计数器

8) 地址多路器

各部件的相互连接关系见图8.2。其中时钟发生器利用外来时钟信号进行分频生成一系列时钟信

号,送往其他部件用作时钟信号。各部件之间的相互操作关系则由状态控制器来控制。各部件的具

体结构和逻辑关系在下面的小节里逐一进行介绍。

8.2.1时钟发生器

时钟发生器 clkgen 利用外来时钟信号clk 来生成一系列时钟信号clk1、fetch、alu_clk 送往CPU

的其他部件。其中fetch是外来时钟 clk 的八分频信号。利用fetch的上升沿来触发CPU控制器开始

172

CLK

CLK1

CLKGEN

ALU_CLK

FETCH

CLK

CLK1

ALU_CLK

FETCH

图1. 时钟发生器

RESET

RESET

执行一条指令,同时fetch信号还将控制地址多路器输出指令地址和数据地址。clk1信号用作指令

寄存器、累加器、状态控制器的时钟信号。alu_clk 则用于触发算术逻辑运算单元。

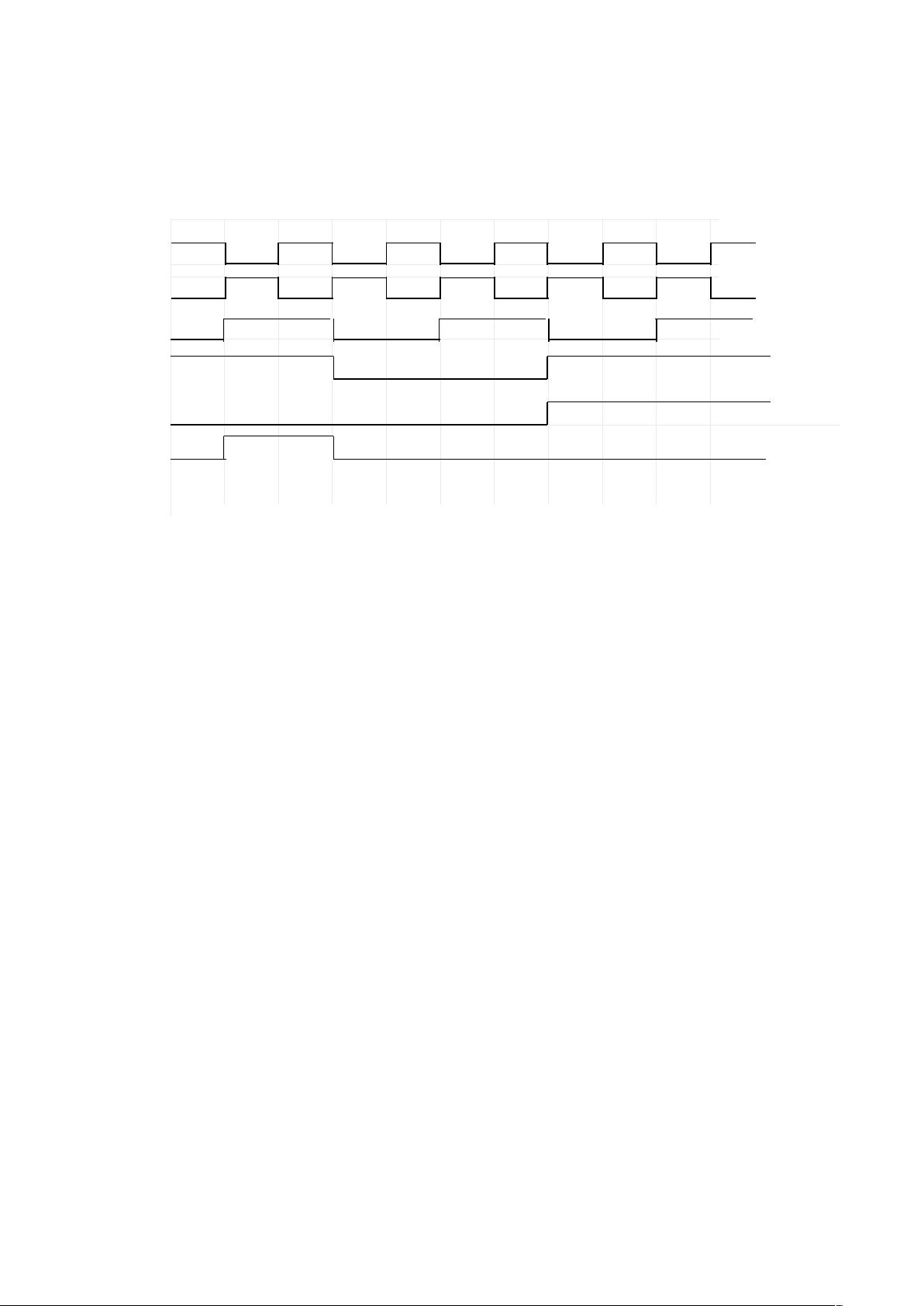

时钟发生器clkgen的波形见下图8.2.2所示:

其VerilogHDL 程序见下面的模块:

module clk_gen (clk,reset,clk1,clk2,clk4,fetch,alu_clk);

input clk,reset;

output clk1,clk2,clk4,fetch,alu_clk;

wire clk,reset;

reg clk2,clk4,fetch,alu_clk;

reg[7:0] state;

parameter S1 = 8'b00000001,

S2 = 8'b00000010,

S3 = 8'b00000100,

S4 = 8'b00001000,

S5 = 8'b00010000,

S6 = 8'b00100000,

S7 = 8'b01000000,

S8 = 8'b10000000,

idle = 8'b00000000;

assign clk1 = ~clk;

always @(negedge clk)

if(reset)

begin

clk2 <= 0;

clk4 <= 1;

fetch <= 0;

alu_clk <= 0;

state <= idle;

end

else

begin

case(state)

S1:

begin

clk2 <= ~clk2;

alu_clk <= ~alu_clk;

state <= S2;

173

clk

clk1

clk2

clk4

fetch

alu_clk

图8.2.2 时钟发生器clkgen的波形

end

S2:

begin

clk2 <= ~clk2;

clk4 <= ~clk4;

alu_clk <= ~alu_clk;

state <= S3;

end

S3:

begin

clk2 <= ~clk2;

state <= S4;

end

S4:

begin

clk2 <= ~clk2;

clk4 <= ~clk4;

fetch <= ~fetch;

state <= S5;

end

S5:

begin

clk2 <= ~clk2;

state <= S6;

end

S6:

begin

clk2 <= ~clk2;

clk4 <= ~clk4;

state <= S7;

end

S7:

begin

clk2 <= ~clk2;

state <= S8;

end

S8:

begin

clk2 <= ~clk2;

clk4 <= ~clk4;

fetch <= ~fetch;

state <= S1;

end

idle: state <= S1;

default: state <= idle;

endcase

end

endmodule

//---------------------------------------------------------------------------

由于在时钟发生器的设计中采用了同步状态机的设计方法,不但使clk_gen模块的源程序可以被各种综

合器综合,也使得由其生成的clk1、clk2、clk4、fetch、alu_clk 在跳变时间同步性能上有明显的提高,

为整个系统的性能提高打下了良好的基础。

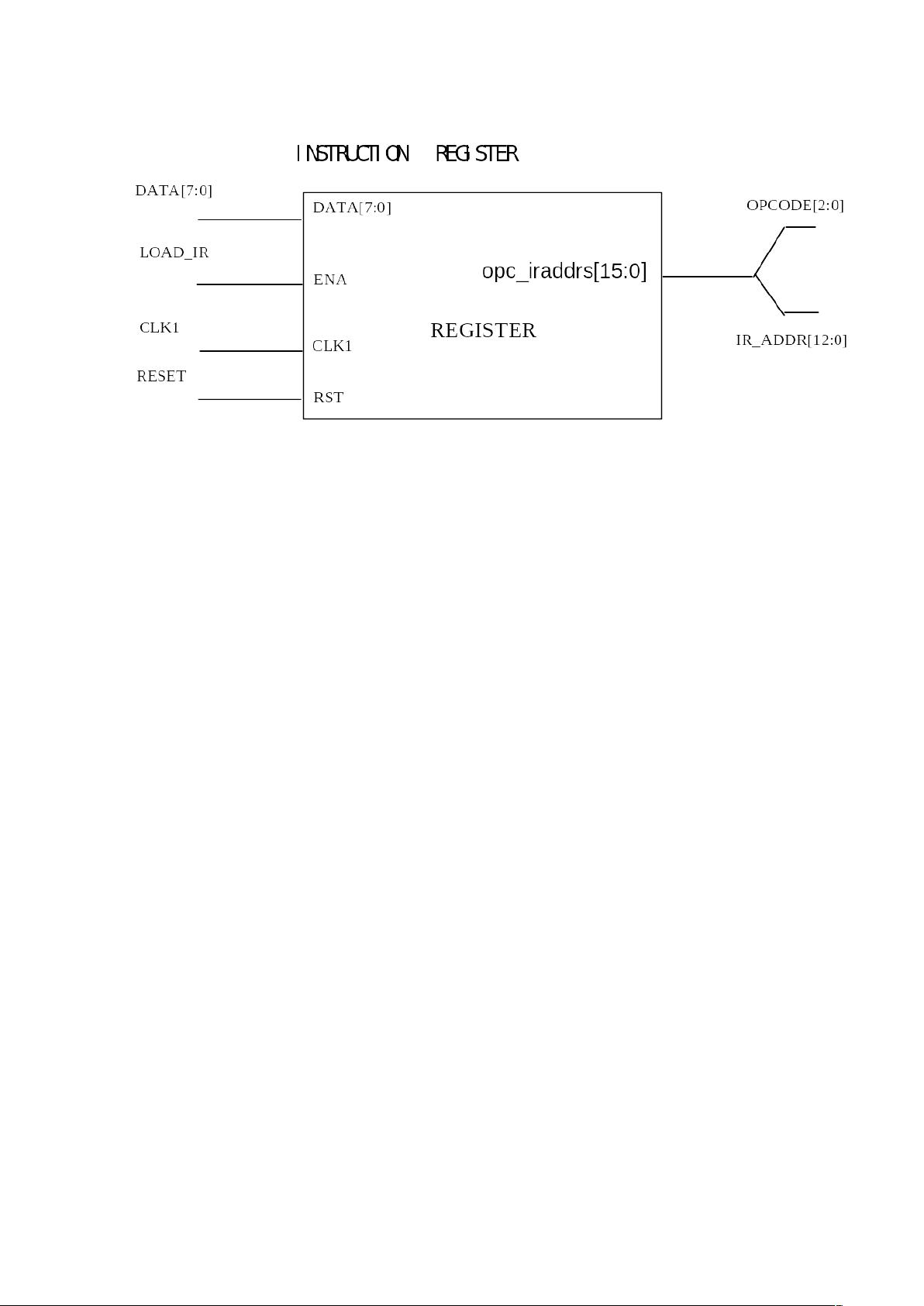

8.2.2 指令寄存器

174

顾名思义,指令寄存器用于寄存指令。

指令寄存器的触发时钟是clk1,在clk1的正沿触发下,寄存器将数据总线送来的指令存入高8位或

低8位寄存器中。但并不是每个clk1的上升沿都寄存数据总线的数据,因为数据总线上有时传输指

令,有时传输数据。什么时候寄存,什么时候不寄存由CPU状态控制器的load_ir信号控

制。load_ir信号通过ena 口输入到指令寄存器。复位后,指令寄存器被清为零。

每条指令为2个字节,即16位。高3位是操作码,低13位是地址。(CPU的地址总线为13位,寻址

空间为8K字节。)本设计的数据总线为8位,所以每条指令需取两次。先取高8位,后取低8位。而

当前取的是高8位还是低8位,由变量state记录。state为零表示取的高8位,存入高8位寄存器,

同时将变量state置为1。下次再寄存时,由于state为1,可知取的是低8位,存入低8位寄存器

中。

其VerilogHDL 程序见下面的模块:

//---------------------------------------------------------------

module register(opc_iraddr,data,ena,clk1,rst);

output [15:0] opc_iraddr;

input [7:0] data;

input ena, clk1, rst;

reg [15:0] opc_iraddr;

reg state;

always @(posedge clk1)

begin

if(rst)

begin

opc_iraddr<=16'b0000_0000_0000_0000;

state<=1'b0;

end

else

begin

if(ena) //如果加载指令寄存器信号load_ir到来,

begin //分两个时钟每次8位加载指令寄存器

casex(state) //先高字节,后低字节

1’b0: begin

opc_iraddr[15:8]<=data;

state<=1;

175

剩余41页未读,继续阅读

资源评论

「已注销」

- 粉丝: 0

- 资源: 5

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功