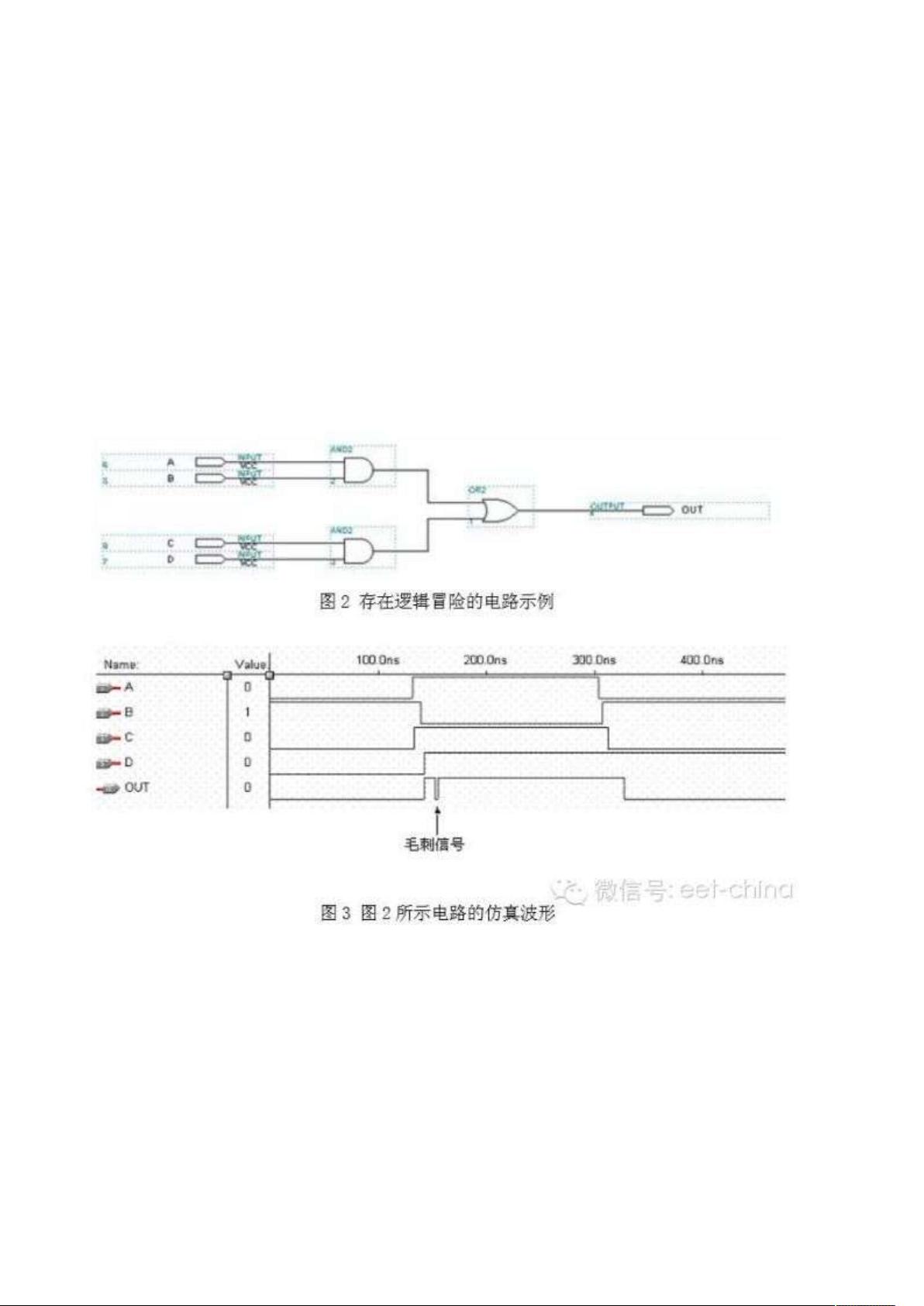

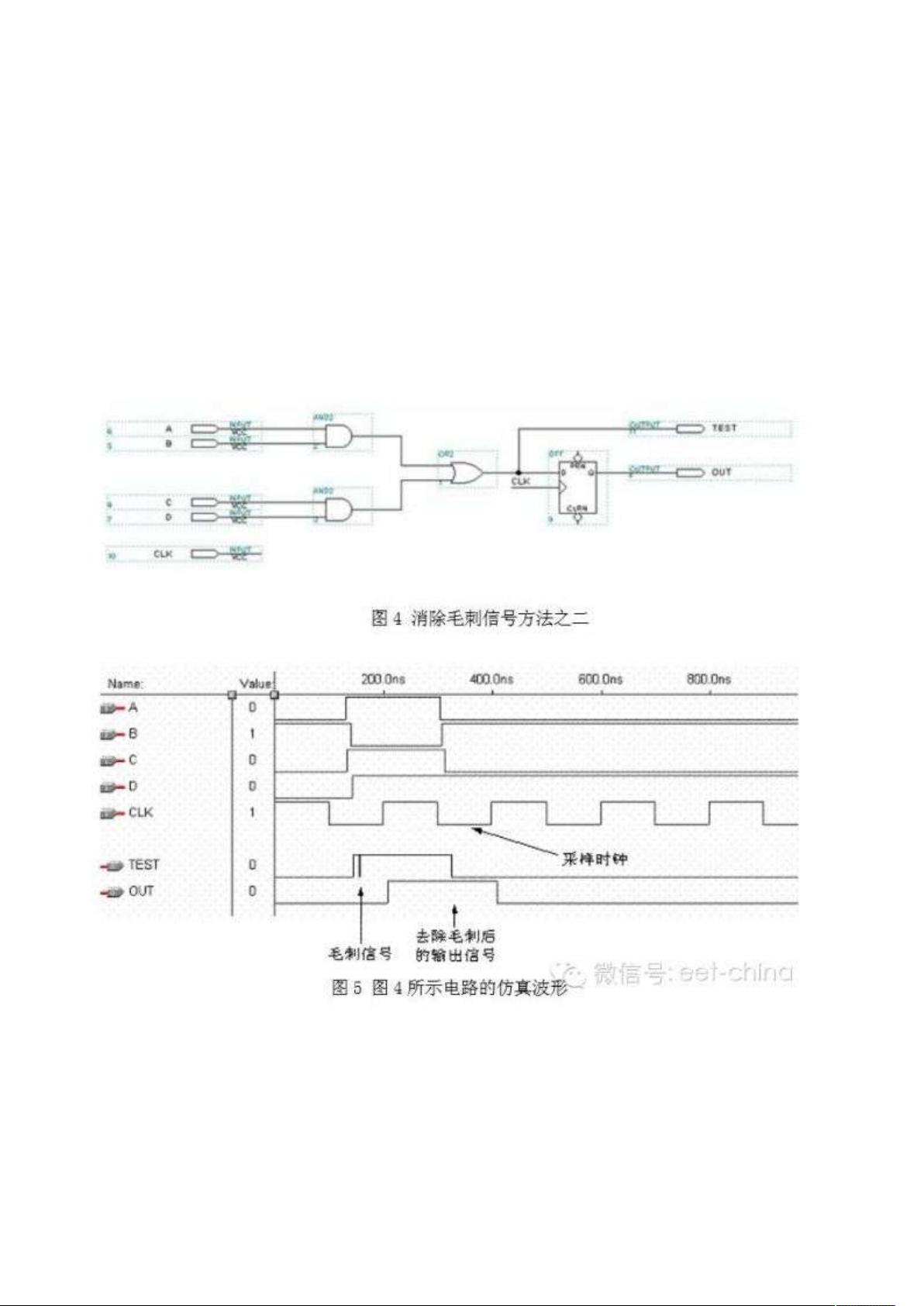

CPLD(复杂可编程逻辑器件)在数字电路设计领域是一种常用的可编程器件,其设计和开发涉及到一系列的重要知识点,本文档旨在分享CPLD数字电路设计的经验和注意事项,特别是时序设计方面的关键点。 建立时间和保持时间是数字电路设计中的基本概念。建立时间指的是触发器在时钟信号上升沿到来之前,输入信号需要稳定的时间。如果输入信号的变化发生在建立时间之内,那么这一变化无法被时钟沿捕获,从而导致数据丢失。保持时间是指时钟沿之后输入信号需要保持稳定的时间。同样地,如果输入信号在保持时间内发生变化,也可能导致数据错误。这两者对于数据的稳定传输至关重要。在设计时,可以通过仿真检查建立时间和保持时间是否满足要求,通常情况下,建立时间和保持时间的值可以为零,但这需要精确的时序控制。 接下来,FPGA和CPLD中的竞争和冒险现象是设计中需要特别注意的问题。在FPGA等可编程器件中,信号通过连线和逻辑单元时会产生一定的延时,这种延时与连线长度、逻辑单元数目、制造工艺、工作电压和温度等因素有关。由于这些因素的存在,在多路信号电平发生变化时,组合逻辑的输出并非总是同步的,可能会出现毛刺(glitch),即瞬间的错误尖峰信号。毛刺可能导致电路出现冒险(hazard),影响电路的稳定性。特别是在时钟端口、清零和置位端口等对信号敏感的输入端口,毛刺的出现可能造成严重后果。 为了处理毛刺,设计时应尽量采用同步电路,因为同步电路的信号变化发生在时钟沿,毛刺产生的可能性相对较低。此外,还可以利用特定的设计技巧减少毛刺的发生,例如使用格雷码计数器代替二进制计数器,因为格雷码计数器的输出变化每次只有一位,从而消除了竞争冒险的条件。D触发器的D输入端对毛刺不敏感,因此在设计时可以利用这一特性,通过在输出信号的保持时间内,用触发器读取组合逻辑的输出信号来减少毛刺。这种方法类似于将异步电路转化为同步电路。 此外,时钟树的偏斜在CPLD/FPGA设计中也是一个需要特别关注的因素。时钟树的偏斜指的是时钟信号在传播到不同的触发器时由于路径长度不同而产生的时间差异。在时钟树设计时,需要考虑时钟树的向前和向后偏斜,并在仿真时通过最大和最小延迟来检查建立和保持时间是否满足要求。在可编程器件中,时钟树的偏斜几乎可以不考虑,因为保持时间通常都是满足的。但在设计时,如果时钟树的设计不合理,即使调整时钟频率也无法解决问题,可能需要对设计进行较大的改动才能保证系统的正常工作。 在CPLD数字电路设计中,时序分析和优化是确保电路稳定工作的关键。设计者需要熟悉相关的设计工具和方法,并在设计过程中不断迭代和验证。本文档分享的这些经验,为设计者提供了一个关于CPLD数字电路设计中时序问题的参考框架,有助于提高设计质量和效率。在实际操作中,结合具体的开发工具和CPLD硬件特性,不断实践和调整设计方案,才能设计出高性能的数字电路系统。

剩余22页未读,继续阅读

- 粉丝: 0

- 资源: 1

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功