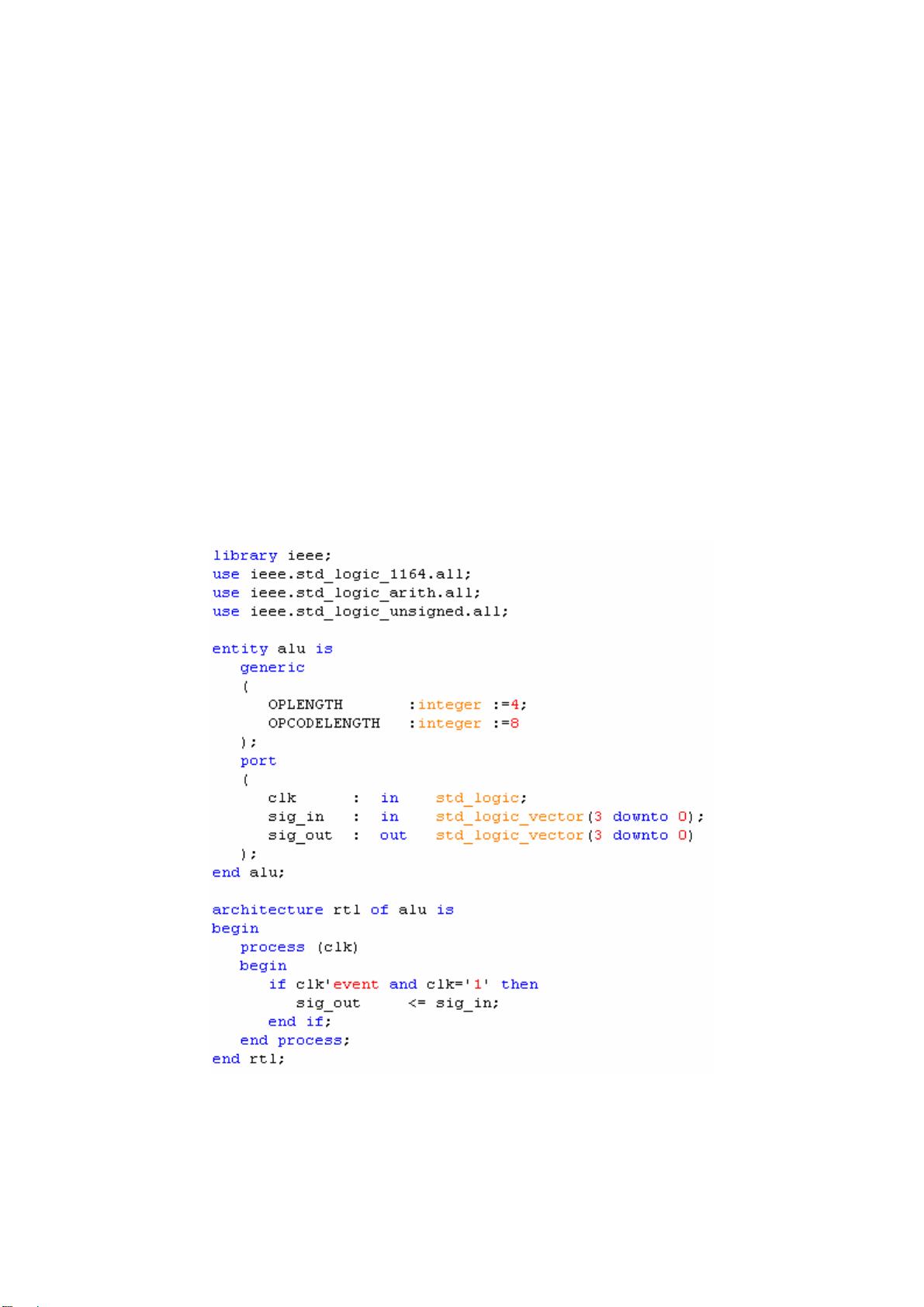

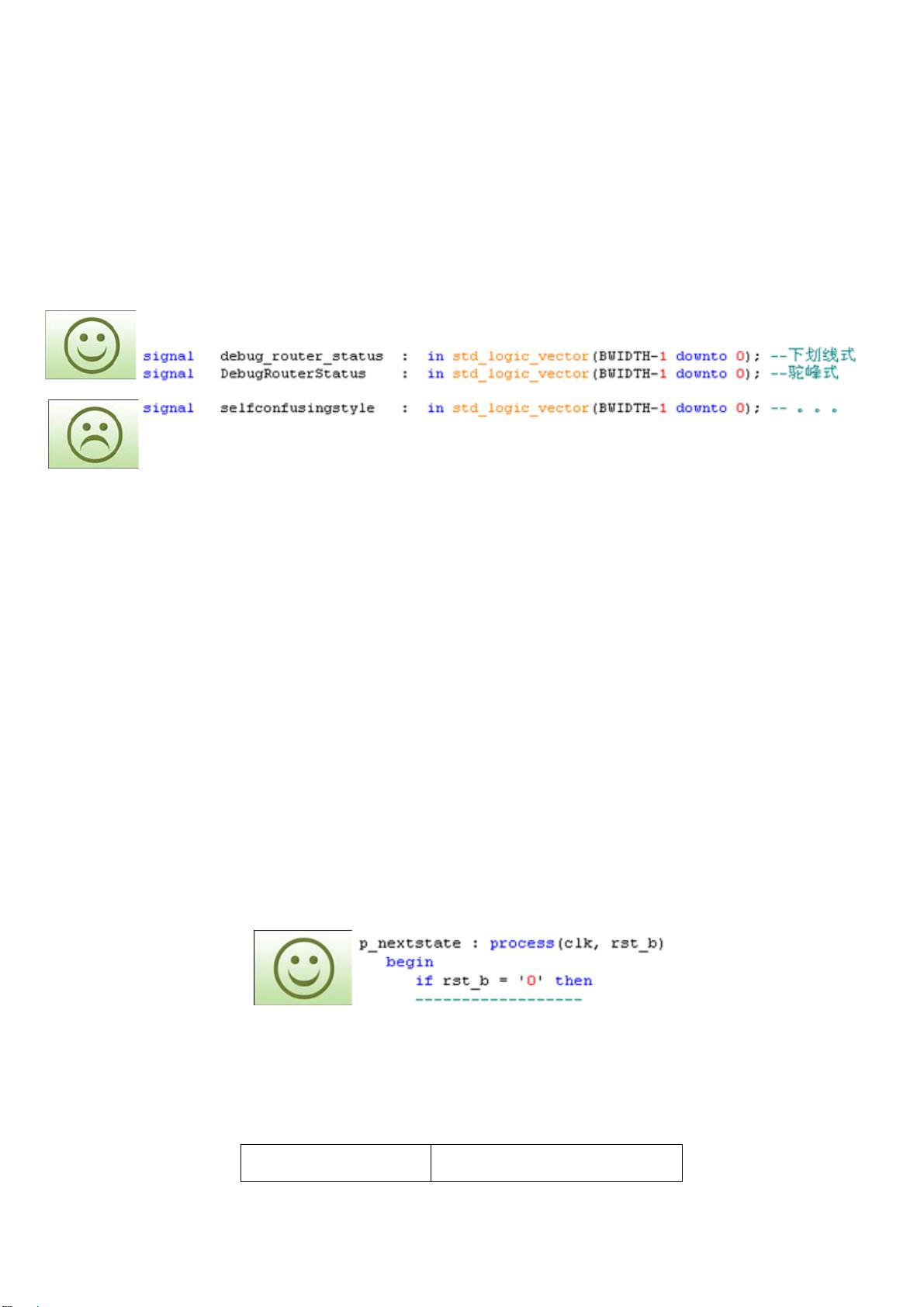

VHDL代码规范是设计和开发高质量数字电路项目的基础,它不仅确保了代码的一致性和可读性,还促进了资源的有效利用。以下是对给定文件中的关键知识点的深入解析: ### 命名惯例 #### 文件命名 1. **每个文件最多一个模块**:这一规则确保了文件的清晰度和易于管理,避免了在一个文件中包含多个实体或架构导致的混乱。 2. **文件名惯例**:文件命名应遵循一定的结构,即`<designunitname>.<description>.vhd`,其中`<designunitname>`通常与实体名相同,而`<description>`则描述了文件的功能或用途,例如`sim`代表仿真不可综合模块。 #### 代码内项目的命名 1. **名字的首个符号为字母**:所有信号、变量、常数等的名字应以字母开头,避免使用数字或其他特殊字符作为首字符。 2. **多个单词使用下划线或驼峰式命名**:当名字由多个单词组成时,推荐使用下划线(snake_case)或驼峰式(CamelCase)来分隔单词,这有助于保持代码的整洁和一致性。 3. **常数名大写**:为了区分常数和其他元素,常数名应全部使用大写字母,这有助于快速识别代码中的常量。 4. **信号、变量的后缀使用**:特定的后缀如`_b`(非)、`_rst`(复位)、`_clk`(时钟)等,用于表示信号的特性和功能,增强代码的可读性。 5. **变量使用v_前缀**:变量应以`v_`前缀开始,便于区分信号和变量,这是代码规范化的重要实践。 6. **模块实例化名包含实体名称**:实例化其他模块时,实例名应包含被实例化的实体名称,避免使用通用的`U1`, `U2`等命名,增强代码的自解释性。 ### 对齐与注释 1. **语句使用空格对齐**:适当的对齐能够显著提升代码的可读性,使复杂的嵌套结构更加清晰。 2. **Entity声明对齐**:端口映射和其他重要声明应适当对齐,确保结构清晰,易于阅读和理解。 3. **重要语句块的注释**:对实现关键功能的语句块添加注释,帮助后续维护人员理解代码意图和工作原理。 4. **注释不常见实现方式**:对于非标准或非直观的实现方法,应提供详细的注释,解释其原因和目的,避免引起误解。 ### 代码风格 #### 移植与可读性要求 1. **每行一个表达式**:确保每一行只包含一个表达式或信号定义,避免一行多任务的情况,提高代码的可读性和维护性。 2. **显式参数映射**:在`Portmap`和`Genericmap`中使用显式参数映射,明确指出实际参数与形式参数之间的对应关系,增强代码的清晰度。 3. **使用constant代替硬编码**:减少直接在代码中使用数字或字符串,转而使用`constant`定义,这有助于代码的维护和修改。 4. **独立的package定义全局元素**:通过独立的`package`定义全局常数和子程序,保持代码的模块化,便于重用和管理。 5. **避免使用综合命令**:在设计阶段尽量不依赖综合工具的特定命令,以增强代码的可移植性和可读性。 6. **关系定义常数间关系**:当常数之间存在确定的关系时,使用关系定义而非重复声明,简化代码并减少错误。 7. **基址加偏移定义地址**:使用基址和偏移量的方式来定义地址,这种定义方式更灵活,易于调整和扩展。 8. **使用genericmap传递常数**:在模块参数中需要传递可能变化的常数时,采用`genericmap`方式,保持代码的灵活性和可配置性。 9. **使用括号表示优先级**:虽然VHDL有默认的运算符优先级,但在复杂的表达式中使用括号明确优先级,可以减少混淆和错误。 #### 语句使用 1. **信号与变量的恰当使用**:理解信号和变量的区别,根据它们的特点选择合适的使用场景,如信号用于硬件连接,变量用于存储临时计算结果。 2. **信号变量不赋初值**:除非有特殊需求,信号和变量不应赋予初始值,以防导致前后仿真结果不一致。 3. **类型信号定义指定范围**:定义`Integer`和`Natural`类型信号时,明确指定数值范围,避免综合器做出错误的假设。 4. **总线使用**:合理使用总线,减少信号的数量,但同时要确保总线的使用不会引入不必要的复杂性。 5. **输入管脚不悬空**:在模块实例化时,所有输入管脚都应有明确的连接,即使在某些情况下不需要,也应使用专用的空置信号(如`XXX_nc`)来连接。 6. **输出管脚连接于_nc信号**:对于未使用的输出管脚,显式地将其连接到空置信号上,以避免综合器产生错误的逻辑。 7. **避免使用X、U、W赋值**:除了在测试平台中,信号赋值应避免使用不确定状态(X)、未知状态(U)或弱信号(W),以确保设计的稳定性和预测性。 8. **过程类型的选择**:根据不同的需求选择合适的过程类型,如时序过程、组合逻辑过程等,确保设计的高效性和正确性。 9. **防止综合latch**:避免在设计中使用可能导致latch产生的结构,如组合逻辑反馈,因为latch可能会导致时序问题和设计不稳定。 10. **检查敏感列表的完整性**:在编写`process`语句时,确保敏感列表包含所有相关的信号,避免因遗漏而引发的问题。 11. **选择语句分支完备**:在编写`case`或`if`语句时,确保所有的可能情况都有对应的处理分支,避免由于未处理的条件导致的运行时错误。 12. **循环语句限制使用exit或next**:在循环语句中,尽量避免使用`exit`或`next`语句,这些语句可能会导致代码难以理解和调试。 13. **case与if的正确使用**:了解并正确应用`case`和`if`语句,选择最符合当前逻辑需求的控制结构,提高代码的效率和可读性。 14. **循环语句的优化**:在使用循环语句时,考虑循环的终止条件和循环体内的操作,尽可能减少循环次数和不必要的计算。 15. **寄存器复位的设计**:设计寄存器复位机制,确保在系统启动或异常情况下,寄存器能够回到预设的初始状态,提高系统的鲁棒性。 16. **状态机的完备设计**:构建完备的状态机,考虑所有可能的转换路径和状态,确保状态机在任何情况下都能正确执行。 17. **健壮的分支语句**:编写分支语句时,考虑到所有可能的输入和边界条件,确保代码在各种情况下的健壮性和稳定性。 18. **模块输出寄存建议**:推荐在模块的输出端使用寄存器,以改善时序性能,减少信号延迟,并增强设计的可预测性。 遵循VHDL代码规范是确保数字电路设计质量、可读性和可维护性的关键。通过实施这些规范,不仅可以提高个人和团队的编程效率,还能促进代码的一致性,减少潜在的错误和故障,最终实现更高性能和更可靠的数字电路系统。

剩余28页未读,继续阅读

- 粉丝: 0

- 资源: 2

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 分享Java相关的东西 - Java安全漫谈笔记相关内容.zip

- 具有适合 Java 应用程序的顺序定义的 Cloud Native Buildpack.zip

- 网络建设运维资料库职业

- 关于 Java 的一切.zip

- 爬虫安装 XPath Helper 2.0

- 使用特定版本的 Java 设置 GitHub Actions 工作流程.zip

- 使用 Winwheel.js 在 HTML 画布上创建旋转奖品轮.zip

- 使用 Java 编译器 API 的 Java 语言服务器.zip

- 使用 Java 的无逻辑和语义 Mustache 模板.zip

- 使用 Java EE 7 的 Java Petstore.zip

信息提交成功

信息提交成功